# Integrated Circuits for Consumer Applications 1976/77

6250-06-1E

| General Information                       |

|-------------------------------------------|

| ICs for Television and<br>Radio Receivers |

| ICs for Electronic Clocks                 |

| ICs for Motor Vehicles                    |

| ICs for Electronic Organs                 |

| ICs for Other Applications                |

|                                           |

ITT Semiconductors are marketed

in **France** by Société des Produits Industriels ITT Département Semiconducteurs INTERMETALL

Sales Offices:

1, avenue Louis Pasteur F-92223 Bagneux Telephone 253 31 39 Telex 260 925

16, rue Emile Schwoerer F-68000 Colmar Telephone (89) 23 99 70 Telex 880 951

Plant and Literature Service in Colmar

in **Germany** by INTERMETALL Halbleiterwerk der Deutsche ITT Industries GmbH Postfach 840, D-7800 Freiburg Telephone (761) 51 71 Telex 07-72 716

in Italy by ITT Standard, Divisione Semiconduttori Corso Europa, 51-53 I-20093 Cologno Monzese (Milano) Telephone (02) 254 74 91/2/3/4/5 Telex 32 351

in the **United Kingdom** by ITT Semiconductors, Footscray, Sidcup, Kent Telephone (01) 300 3333 Telex 21 836

Addresses of ITT Semiconductors sales outlets in the other European countries available from INTERMETALL GmbH, Postfach 840, D-7800 Freiburg

Address of your local sales office/agent

# TTT

Integrated Circuits for Consumer Applications

Manual 1976/77

\*

# Contents

|                                        | Page |

|----------------------------------------|------|

| General Information                    | 7    |

| Alphabetic Index of Types              | 9    |

| Summary of Types                       | 10   |

| Technical Information                  | 12   |

| ICs for Television and Radio Receivers | 17   |

| ICs for Electronic Clocks              | 111  |

| ICs for Motor Vehicles                 | 131  |

| ICs for Electronic Organs              | 143  |

| ICs for Other Applications             | 159  |

# **General Information**

# Alphabetic Index of Types

| Types                                                                                        | Page                                     | Types                                                                                        | Page                                                 |

|----------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------|

| SAA 1004<br>SAA 1005<br>SAA 1008<br>SAA 1020<br>SAA 1021<br>SAA 1024<br>SAA 1025<br>SAA 1130 | 144<br>148<br>26<br>26<br>38<br>42<br>52 | TDD 1605<br>TDD 1606<br>TDD 1608<br>TDD 1610<br>TDD 1612<br>TDD 1615<br>TDD 1618<br>TDD 1624 | 174<br>174<br>174<br>174<br>174<br>174<br>174<br>174 |

| SAH 215                                                                                      | 160                                      | UAA 210<br>UAA 1007                                                                          | 176<br>126                                           |

| SAJ 110<br>SAJ 270 E<br>SAJ 300 N<br>SAJ 300 T                                               | 152<br>112<br>114<br>116                 | ZTE 1,5<br>ZTE 2<br>ZTE 2,4<br>ZTE 2,7                                                       | 180<br>180<br>180<br>180                             |

| SAK 215                                                                                      | 132                                      | ZTE 3<br>ZTE 3,3                                                                             | 180<br>180<br>180                                    |

| SAY 115                                                                                      | 136                                      | ZTE 3,6<br>ZTE 3,9                                                                           | 180<br>180                                           |

| TAA 550<br>TAA 780<br>TAA 790                                                                | 184<br>118<br>64                         | ZTE 4,3<br>ZTE 4,7<br>ZTE 5,1                                                                | 180<br>180<br>180                                    |

| TBA 800 C<br>TBA 940<br>TBA 950<br>TBA 950 : F                                               | 70<br>78<br>84<br>84                     | ZTK 6,8<br>ZTK 9<br>ZTK 11<br>ZTK 18<br>ZTK 22                                               | 184<br>184<br>184<br>184<br>184                      |

| TCA 350 Y<br>TCA 380<br>TCA 700<br>TCA 860                                                   | 164<br>170<br>140<br>122                 | ZTK 27<br>ZTK 33                                                                             | 184<br>184<br>184                                    |

| TDA 0470-D<br>TDA 1035<br>TDA 1044<br>TDA 1053<br>TDA 9400<br>TDA 9500                       | 156<br>92<br>98<br>102<br>104<br>104     |                                                                                              |                                                      |

# ICs for Television and Radio Receivers

| SAA | 1008  | TV Character Generator                                                                        |

|-----|-------|-----------------------------------------------------------------------------------------------|

| SAA | 1020  | IC Set for Controlling TV Tuners (Storage IC)                                                 |

| SAA | 1021  | IC Set for Controlling TV Tuners (Control IC)                                                 |

| SAA | 1024  | Thirty Channel Ultrasonic Transmitter for<br>Remote-Controlled TV Receivers                   |

| SAA | 1025  | Thirty Channel Ultrasonic Receiver for<br>Remote-Controlled TV Receivers                      |

| SAA | 1130  | Thirty Channel Ultrasonic Receiver<br>with Program Store                                      |

| TAA | 790   | Controlled Pulse Generator                                                                    |

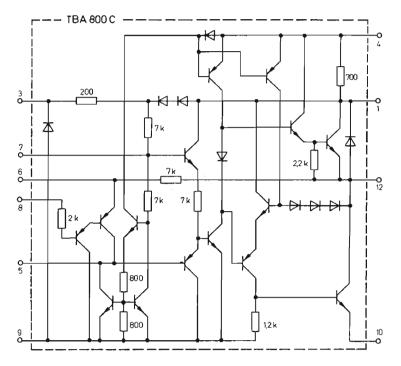

| тва | 800 C | 5 W Audio Power Amplifier                                                                     |

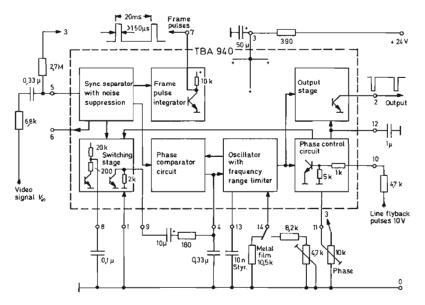

| тва | 940   | Controlled Pulse Generator for Thyristor Line<br>Output Stages                                |

| тва | 950   | Controlled Pulse Generator for Transistor Line<br>Output Stages                               |

| ТВА | 950:F | Controlled Pulse Generator for Transistor Line<br>Output Stages in Multistandard TV Receivers |

| TDA | 1035  | Sound Channel IC for TV Receivers                                                             |

| TDA | 1044  | Frame Scan Circuit for TV Receivers                                                           |

| TDA | 1053  | PIN Diode π Network                                                                           |

| TDA | 9400  | Line Circuit for TV Receivers with Thyristor Line<br>Output Stage                             |

| TDA | 9500  | Line Circuit for TV Receivers with Transistor Line Output Stage                               |

# ICs for Electronic Clocks

| SAJ | 270 E | CMOS Circuit for Quartz-Controlled Wrist Watches with 32 kHz Quartz           |

|-----|-------|-------------------------------------------------------------------------------|

| SAJ | 300 N | CMOS Circuit for RF Quartz Clocks with Digital<br>Adjustment and 1 Hz Output  |

| SAJ | 300 ⊤ | CMOS Circuit for RF Quartz Clocks with Digital<br>Adjustment and 64 Hz Output |

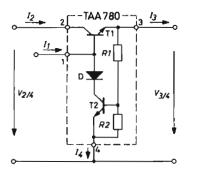

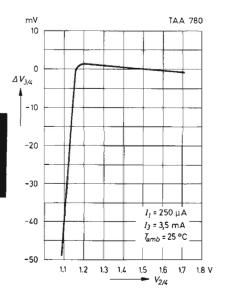

| ТАА | 780   | 1.1 V Stabilizing Circuit                                                     |

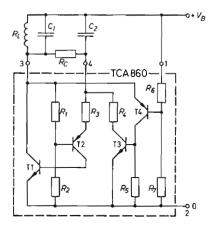

| тса | 860   | Driving Circuit for Clocks with Single Coil<br>Balance Systems                |

| UAA | 1007  | Alarm-Clock IC                                                                |

# **ICs for Motor Vehicles**

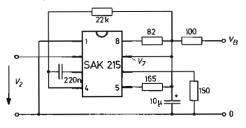

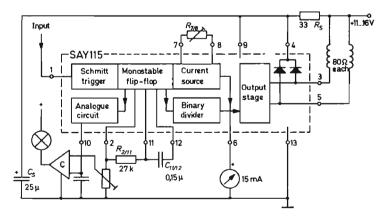

| SAK 215 | Pulse Shaper for Revolution Counters |

|---------|--------------------------------------|

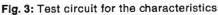

| SAY 115 | Speedometer and Mileage Indicator    |

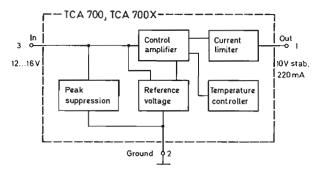

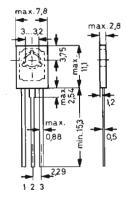

| TCA 700 | Car Voltage Stabilizer               |

# ICs for Electronic Organs

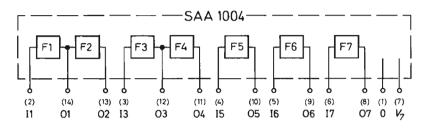

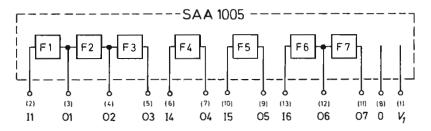

| SAA 1004   | Seven Stage Frequency Divider in I <sup>2</sup> L Technique |

|------------|-------------------------------------------------------------|

| SAA 1005   | Seven Stage Frequency Divider in I <sup>2</sup> L Technique |

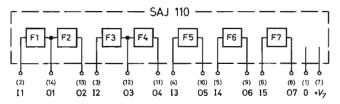

| SAJ 110    | Seven Stage Frequency Divider                               |

| TDA 0470-D | Gate for Electronic Organs                                  |

# **iCs** for Other Applications

| SAH | 215        | Telephone Push-Button IC                     |

|-----|------------|----------------------------------------------|

| TAA | 550        | Temperature-Compensated Stabilizing Circuit  |

| тса | 350 Y      | Delay Line for Analogue Signals              |

| тса | 380        | Duplex RF Delay Line                         |

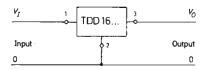

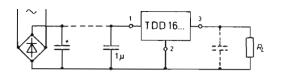

| TDD | 1605       | Voltage Stabilizers for 524 V                |

| TDD | 1624       |                                              |

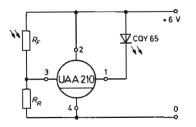

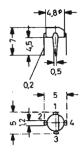

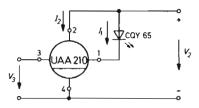

| UAA | 210        | Exposuremeter-IC                             |

| ZTE | 1.5 5.1    | Parallel Stabilizing Circuits                |

| ΖTK | 6.8 ZTK 33 | Temperature-Compensated Stabilizing Circuits |

# Characteristics and Maximum Ratings, Recommended Operating Conditions

The electrical performance of a semiconductor device is usually expressed in terms of its characteristics and maximum ratings.

Characteristics are those properties of the device which can be measured by use of suitable measuring instruments and set-ups, and provide information on the performance of the device under specified operating conditions (at a given bias, for example). Depending on requirements, they are quoted either as typical values, guaranteed values or maximum ratings.

Typical values are expressed as figures or as one or more curves, and are subject to spreads.

Guaranteed values are preceded either by the symbol > (greater than) or < (less than); sometimes the guaranteed spread limits are indicated by two numbers with three dots between them. Occasionally a typical curve is accompanied by another curve, this being a 95 %, or, in a few cases, a maximum spread limit curve.

Maximum ratings give the values which cannot be exceeded without risk of damage to the device. Changes in supply voltage and in the tolerances of other components in the circuit must be taken into consideration. No single limit should ever be exceeded, even when the device is operated well within the other maximum limits. The inclusion of the word "admissible" in a title means that the associated curve defines the maximum ratings. If characteristics and maximum ratings are listed together without a separate heading, then the maximum ratings are identified by the word "admissible".

Because the performance of complex devices such as the ICs listed in this book cannot always be fully described in terms of characteristics and maximum ratings, it is sometimes necessary to describe some performance features by reference to a test circuit, which in many instances is the same as the recommended operational circuit. For some ICs, therefore, a third set of data is included under the heading "Recommended Operating Conditions".

#### Logic Levels

The logic levels of digital circuits are denoted by the letters "H" (high = maximum positive level) and "L" (low = minimum positive level). If positive logic is used, as usual in connection with bipolar ICs, "H" corresponds to logic "1" and "L" to logic "0".

In connection with MOS circuits the electrical states sometimes are denoted by negative logic, then the state "H" corresponds to logic "0" and "L" to logic "1".

#### **Electrical Designations**

The subscripts used in conjunction with the numerous electrical IC data (V - voltage, I - current, R - resistance, f - frequency, etc.) usually denote the associated lead numbers.

If a one-number subscript is used in conjunction with a voltage (V), then this means that the voltage is referred to circuit ground (usually -  $V_B$ , 0 V). When a two-number subscript is used, the voltage concerned is that measured between the two terminals, the terminal denoted by the first number usually being positive with respect to the other. Since a dual in line package has 14 pins, the subscript numbers are usually separated by diagonal strokes to reduce the risk of error. A "0" in the third place means, as with transistors, that the other pins of the device are open circuit.

Usually only a single-number subscript is used in conjunction with current. A current indicated as positive is assumed to flow into the pin concerned unless otherwise indicated by arrows on the associated circuit diagram.

Resistors, capacitors and inductors are normally numbered consecutively (e. g. R1, R2, etc.). If there are two numbers in the subscript (e. g.  $R_{14/3}$ ), then this means that the resistor is connected between correspondingly numbered pins of the circuit.

#### **Assembly Instructions**

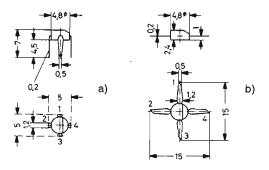

1. Plastic Encapsulation 50 B 4

a) Devices with vertical pins (suffix "A").

These ICs can be soldered to printed circuit boards so that the bottom of the package rests flat on the side of the board opposite to that carrying the copper conductors.

The pins can be either dip- or hand-soldered. At a soldering temperature of 230...260 °C the soldering time must not exceed 7 sec.

b) Devices with horizontal pins (suffix "B")

These ICs can be soldered to printed circuit boards so that the pins lie flat against the copper conductors with the plastic case projecting into a cut-out in the board.

Hand-soldering must be used. If the soldered joints are spaced more than 1.5 mm (dimension "I") from the case and a soldering temperature of 250 °C is used, then the soldering time must not exceed 8 sec.

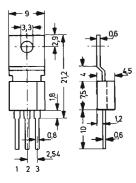

2. Plastic TO-116 Encapsulation and similar

As shown in the figure below, the device is fitted to the component side of the board, the pins being soldered to the conductors on the opposite side. A shoulder on each lead ensures that the device cannot be pressed flat against the printed circuit board.

If hand- or dip-soldering at a temperature of 250  $^{\circ}$ C is used, the soldering time must not exceed 7 sec.

3. Metal Encapsulation similar to TO-5 with 6 to 14 leads

These devices may be mounted in any position. The leads must be bent not less than 1.5 mm from the bottom of the case and then splayed out in accordance with the grid dimensions.

The leads must be cut to the required length prior to the soldering process, which may be performed either by hand- or dip-soldering. The following solder times  $t_{max}$  in accordance with the solder temperatures mus be observed.

For dip-soldering:  $t_{mox} = 5 \text{ sec}$  at 250 °C solder-bath temperature and  $t_{mox} = 4 \text{ sec}$  at 300 °C solder-bath temperature. For hand-soldering:  $t_{mox} = 15 \text{ sec}$  with a soldering-iron temperature of 250 °C  $t_{mox} = 12 \text{ sec}$  with a soldering-iron temperature of 300 °C

$t_{max} = 8$  sec with a soldering-iron temperature of 350 °C

If MOS components are soldered the soldering temperature should never exceed 300 °C. The solder-bath or soldering-iron and the printed board to be soldered should be kept at the same potential in order to avoid any harmful current flow. It is therefore recommended that the solder-bath or soldering-iron and the leads to be soldered be grounded.

### 4. Glass Encapsulation DO-35

At a recommended soldering temperature of  $\leq 245$  °C the maximum permissible soldering time must not exceed 5 sec. The minimum distance between case and solder point should be at least 4 mm when the component is mounted axis parallel to the p. c. board and 1.5 mm when mounted axis perpendicular to the p. c. board.

### Protective Measures for MOS Components

In order to avoid destruction of the components by static discharges or noise voltages, protective structures have been provided at the inputs and outputs. They consist of PN junctions to the substrate which operate in the forward direction in the case of positive voltages; in the case of negative voltages they present a defined non-destructive breakdown. In this case integrated resistors limit the current. Furthermore, in the case of a negative voltage of about -40 V, a field-effect transistor at the input becomes conductive. For higher negative voltages this field-effect transistor constitutes a short-circuit.

All these protective measures behave as RC-networks; their component values depend upon the designed operating speed of the circuit.

If MOS components are not handled in the right way, it can easily happen that static discharges of some thousands of volts from capacitances of over 100 pF reach the connection pins. Despite the above-mentioned protective structures it is suggested therefore that the following recommendations be followed: The floor, the work-benches and the chairs should be provided with a conductive layer. Only metallic transport boxes should be used.

All tools which come into contact with the connection pins (test equipment, soldering-irons, flow-soldering equipment) should be at the same potential as the MOS circuits. Voltage peaks arising from switching operations should be carefully avoided.

MOS components should remain in their original packing (e.g. conductive foam) as long as possible. Before touching MOS components, the packing or the metal container should be touched in order to equalize potentials. Before inserting MOS circuits into printed boards it is imperative to touch the printed board first. MOS circuits should be the last components to be inserted into the printed board and soldered there. The connections of the printed board should remain short circuited until the board is finally used. MOS components must not be inserted or removed from the p. c. board if supply voltage is switched on.

Following these instructions is particularly important in those cases where persons handling MOS circuits wear clothes made from synthetic fibres or wool, or where they wear shoes with non-conductive soles.

# ICs for Television and Radio Receivers

# TV Character Generator

The SAA 1008 is a monolithic integrated MOS circuit in silicon gate technique for displaying a program number  $(1 \dots 16)$  on the screen of the television receiver, especially in combination with the INTERMETALL ultrasonic remote control receiver SAA 1130.

The fading-in of the program number occurs automatically on the following occasions: with every program command, with the recall command Z1, and with the command "Sequential program change" (see SAA 1130). The duration of the display is determined by an *RC* network. The numbers are displayed, within a darkened field constituted by 7 x 9 (4 x 9) dots, in the shape of a 5 x 7 dot matrix (ones) or a 2 x 7 dot matrix (tens). Each dot is approximately square and consists of six line sections equivalent to approximately 0.45  $\mu$ s. The field area commences at a distance of 114 lines from the upper edge of the picture area and a distance of approximately 86 dots (two-digit number) or 90 dots (one-digit number) from the left margin of the picture. The formation of numbers by the 5 x 7 or 2 x 7 dot matrix can be adapted to comply with customer's wishes by varying the mask. By using appropriate external circuitry it would also be possible to display colored numbers on a field of different color.

The SAA 1008 is capable of processing signals from the ultrasonic remote-control receiver SAA 1130 directly. The control terminals of the SAA 1130 (pins 8...12) are connected to the control terminals of the SAA 1008: the SAA 1008 recognises the program command and the recall command Z1 (see table 1) from the 5-bit word supplied by the SAA 1130. The program outputs of the SAA 1130 are connected to the program inputs of the SAA 1008, and the SAA 1008 recognises the program number from the 4-bit word supplied by the SAA 1130 (see table 2).

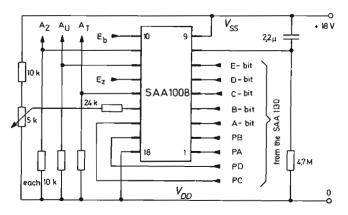

Fig. 1: Operating circuit of the SAA 1008

## Fig. 2:

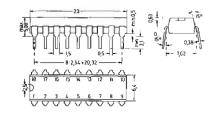

SAA 1008 in plastic package 20 A 18 according to DIN 41 866 Weight approximately 1.2 g Dimensions in mm

# Pin connections

- 1 Program input PA

- 2 Program input PB

- 3 Control input A-bit

- 4 Control input B-bit

- 5 Control input C-bit

- 6 Control input D-bit

- 7 Control input E-bit 8 Timing input Er

- 8 Timing input E<sub>K</sub>

- 9 Ground, 0, V<sub>SS</sub>

- 10 Input Eb for vert. flyback pulse

- 11 Character output Az

- 12 Field-darkening output Au

- 13 Input  $E_z$  for line flyback pulse

- 14 Clock frequency output AT

- 15 Adjustment input Ep

- 16 Program input PC

- 17 Program input PD \_

- 18 Supply voltage VDD

All voltages are referred to pin 9 (Vss).

# Maximum Ratings

| Drain voltage                       | -V <sub>DD</sub> | 20         | V  |

|-------------------------------------|------------------|------------|----|

| Voltage at the other pins           | Vn               | - 30 + 0.3 | V  |

| Drain currents, pins 11, 12 and 14  | -1 <sub>D</sub>  | 5          | mΑ |

| Ambient operating temperature range | Tomb             | - 20+65    | °C |

| Storage temperature range           | Ts               | - 55 + 125 | °C |

# **Recommended Operating Conditions**

| Supply voltage                          | -V <sub>DD</sub> | 18 (16.5 19. | .5) V |

|-----------------------------------------|------------------|--------------|-------|

| Input voltages at pins 3 7              | -VIH             | < 0.8        | v     |

|                                         | -VIL             | > 4          | V     |

| Input voltages at pins 1, 2, 10.        | -VIH             | < 0.8        | V     |

| 13, 16 and 17                           | -V/L             | > 6          | v     |

| Frequency of the internal clock         | ft               | 2.2          | MHz   |

| oscillator                              | tb               | 0.2 1        | ms    |

| Pulse duration of signal E <sub>b</sub> | tz               | 412          | μs    |

| Pulse duration of signal E <sub>z</sub> |                  |              |       |

# Characteristics at -V\_DD = 18 V, $T_{amb}$ = 25 °C

| Voltage drop across the output transistors at $-l_{O} = 1 \text{ mA}$ | ∆V               | < 1 | v  |

|-----------------------------------------------------------------------|------------------|-----|----|

| Current consumption                                                   | -1 <sub>DD</sub> | 28  | mΑ |

# SAA 1008

The table 1 has been taken from the SAA 1130 data sheet and shows the relationship between the commands and the output code at pins 8...12 of the SAA 1130. An additional column indicates which of the 31 commands in the SAA 1008 triggers the fading-in of the program number. The other commands do not affect the SAA 1008.

| Table 1: ( | Commands a    | and outpou | t code c | of the | SAA | 1130, | and | their I | recog- |

|------------|---------------|------------|----------|--------|-----|-------|-----|---------|--------|

| i          | nition by the | SAA 1008   |          |        |     |       |     |         |        |

| Command                  | Output code SAA 1130<br>at pins 812 |   |   |   |     |             |

|--------------------------|-------------------------------------|---|---|---|-----|-------------|

|                          | E                                   | Α | B | С | D   |             |

| Sequential progr. change | L                                   | н | н | Н | Н   | recognised  |

| Mains Off                | Н                                   | L | н | н | н   |             |

| Sound Off                | L                                   | L | н | н | Н   |             |

| Color saturation $+$     | н                                   | н | L | н | н   |             |

| Normalisation            | L                                   | н | L | н | н   |             |

| Color saturation –       | н                                   | L | L | Н | н   |             |

| Additional command Z1    | L                                   | L | L | н | Н   | recognised  |

| Brightness +             | н                                   | н | н | L | н   |             |

| Additional command Z2    | L                                   | н | н | L | н   |             |

| Brightness -             | н                                   | L | н | L | н   |             |

| Additional command Z3    | L                                   | L | н | L | н   |             |

| Volume +                 | н                                   | н | L | L | н   |             |

| Additional command Z4    | L                                   | н | L | L | н   |             |

| Volume –                 | Н                                   | L | L | L | н   |             |

| Additional command Z5    | L                                   | L | L | L | н   |             |

| Program 1                | н                                   | н | н | Н | L ] |             |

| Program 2                | L                                   | н | н | н | L   |             |

| Program 3                | н                                   | L | н | Н | L   |             |

| Program 4                | Ĺ                                   | L | н | Н | L   |             |

| Program 5                | н                                   | н | L | н | L   |             |

| Program 6                | L                                   | н | L | н | L   |             |

| Program 7                | Н                                   | L | L | Н | L   |             |

| Program 8                | L                                   | L | L | н | L   | recognised  |

| Program 9                | Н                                   | н | н | L | н   | looogiilood |

| Program 10               | L                                   | н | н | L | L   |             |

| Program 11               | Н                                   | L | н | L | L   |             |

| Program 12               | L                                   | L | н | L | L   |             |

| Program 13               | H                                   | н | L | L | L   |             |

| Program 14               | L                                   | н | L | L | L   |             |

| Program 15               | н                                   | L | L | L | L   |             |

| Program 16               | L                                   | L | L | L | LJ  |             |

Table 2 below has also been taken from the SAA 1130 data sheet. It shows the code in which information on the selected program is delivered at pins 6, 7, 13 and 14 of the SAA 1130. The table also applies to the program inputs of the SAA 1008, i. e. the pins 1, 2, 16 and 17.

| Program<br>number | Code<br>PA | PB | PC | PD | _ |

|-------------------|------------|----|----|----|---|

| 1                 | L          | L  | L  | L  |   |

| 2                 | н          | L  | L  | L  |   |

| 3                 | L          | н  | L  | L  |   |

| 4                 | н          | н  | L  | L  |   |

| 5                 | L          | L  | н  | L  |   |

| 6                 | н          | L  | н  | L  |   |

| 7                 | L          | н  | н  | L  |   |

| 8                 | н          | н  | н  | Ľ  |   |

| 9                 | L          | L  | L  | н  |   |

| 10                | н          | L  | L  | Н  |   |

| 11                | L          | н  | L  | Н  |   |

| 12                | н          | н  | L  | Н  |   |

| 13                | L          | L  | н  | Н  |   |

| 14                | н          | L  | н  | н  |   |

| 15                | L          | н  | н  | н  |   |

| 16                | н          | н  | н  | Н  |   |

|                   |            |    |    |    |   |

0----

ī.

### Table 2: Output code of the SAA 1130 program outputs and input code of the SAA 1008 program inputs

### Design and Operation Mode of the SAA 1008

The function of the SAA 1008 will be explained with reference to the various pins.

Pins 1, 2, 16 and 17 - program inputs PA ... PD

To these inputs, information on the selected program must be statically applied in binary-coded form. The required code is shown in table 2. This coded signal is preferably taken directly from the program outputs of the SAA 1130.

#### Pins 3 . . . 7 – A-bit . . . E-bit control inputs

By means of the signal applied to these inputs, which is to be coded according to table 1 and supplied preferably directly from the control terminals of the SAA 1130, the fading-in of the program number on the screen of the TV receiver can be triggered. As table 1 shows, the program number display occurs with every program command, with the command "Sequential program change" and with the additional command Z1. What is being displayed in each case is the program number statically applied in coded form to the program inputs.

Pin 8 – timing input  $E_K$

An *RC* network is connected to this pin, its time constant determining the duration of the program number display. The display is triggered by briefly connecting pin 8 to  $V_{SS}$ . The values entered in Fig. 1 for this *RC* network result in a duration of approximately 2 seconds.

Pin 9 – ground, 0, Vss

Positive terminal of the supply voltage, substrate, reference potential. All voltage levels are related to this potential.

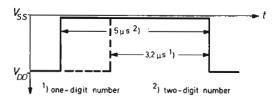

Pin 10 – input E<sub>b</sub> for the vertical flyback pulse

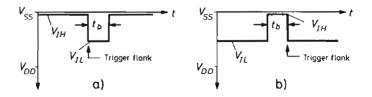

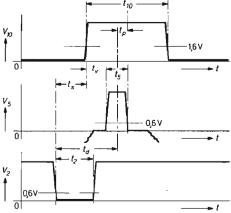

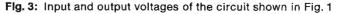

To this pin is to be applied the vertical flyback pulse in a shape shown in Fig. 3.

Fig. 3: Shape of the input signal at pin 10

- a) for negative-going pulses

- b) for positive-going pulses

Pin 11 - character output Az

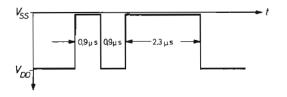

Output supplying character information. Drain terminal of an open-drain transistor. The output signal shown in Fig. 4 is obtained if a load resistance is connected between pin 11 an  $V_{DD}$  (see Fig. 1). It applies to the first line composing the number "15".

Pin 12 - field-darkening output Au

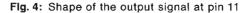

Output for the field-darkening operation. Drain terminal of an open-drain transistor. The output signal shown in Fig. 5 is obtained if a load resistance is connected between pin 12 and  $V_{DD}$  (see Fig. 1).

Fig. 5: Shape of the output signal at pin 12

Pin 13 – input  $E_z$  for the line flyback pulse To this pin is to be applied the line flyback pulse in a shape shown in Fig. 6.

Fig. 6: Shape of the input signal at pin 13

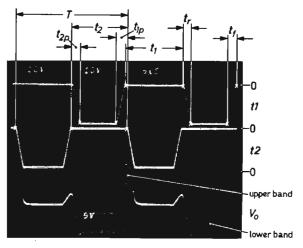

Pin 14 — clock frequency output AT

For measuring purposes, the signal of the internal clock oscillator is required externally. In normal operation this is not the case. Pin 14 is then left vacant.

### Pin 15 - adjustment input Ep

For the fine adjustment of the clock frequency, a variable direct voltage is applied to this input which is preferably obtained by means of the supply voltage potential divider shown in Fig. 1. The clock frequency determines the dot width within characters to be displayed, and the distance of the display field from the left-hand edge of the frame. Its nominal value is 2.2 MHz. If it is to be set with the aid of a frequency meter, pin 13 must be connected to  $V_{DD}$  during the trimming operation.

### Pin 18 - supply voltage VDD

Negative terminal of the supply voltage; in television receivers, usually connected to ground.

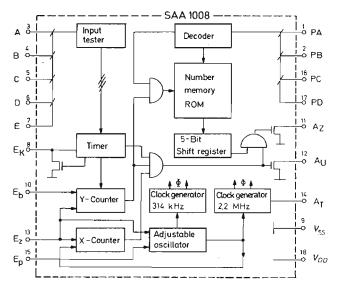

# Block Diagram of the SAA 1008

Fig. 7 shows a simplified block diagram of the SAA 1008. The frequency of the adjustable integrated oscillator (2.2 MHz) is applied to two clock generators which derive from it a two-phase clock of 2.2 MHz and 314 kHz (2.2 MHz : 7). At output A<sub>T</sub> it is possible to measure the oscillator frequency if this terminal is connected to  $V_{DD}$  through a pull-up resistor. During the frequency measurement it is also necessary to connect input E<sub>z</sub> to  $V_{DD}$ .

The input tester examines the 5-bit word supplied by the SAA 1130 to the control inputs  $A \ldots E$  and evaluates the combinations listed in table 1 as commands for fading-in the program number. The number displayed is determined by the 4-bit combination applied to the program inputs (see table 2). The appropriate number is called up in the number memory via a decoder. Data for each line are read out serially, the position of the faded-in number on the screen being determined by the X-counter and the Y-counter.

The duration of the dlsplay is determined by the integrated timer in connection with the externally connected *RC* network at pin 8 (see Fig. 1).

Fig. 7: Block diagram of the SAA 1008

# IC Set for Controlling TV Tuners

This IC set, which consists of two integrated MOS circuits, generates digitally and electronically all the data required for tuner control such as the tuning voltage, the switching voltage for band selection and the AFC fine-tuning signal.

Thanks to the extremely low current consumption of the storage IC SAA 1020, the channel data remain stored during approx. one year even when the TV receiver is switched off, provided a small 1.5 V battery. This IC set also facilitates electronic station searching to be performed, with silent tuning. All the mechanical and electronic devices hitherto required for channel selection and storage, including tuning potentiometers, have now become superfluous: in conjunction with INTERMETALL's ultrasonic remote-control system, i.e. transmitter SAA 1024 and receiver SAA 1130, and also with the character display circuit SAA 1008 – all of which fully compatible with each other – an optimum overall solution to the design complex "remote control, electronic touch-buttons, program number display, channel storage and tuner control in modern color television receivers" has now been achieved.

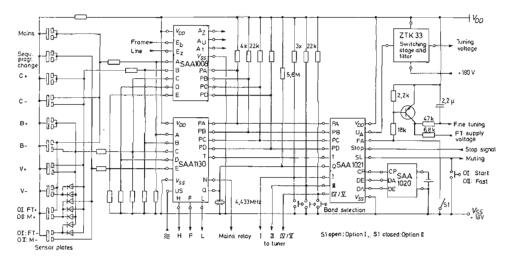

The IC set comprises the storage IC SAA 1020, which functions as a static shift register and has an extremely low current consumption, and the control IC SAA 1021, which performs the data processing duties. The block diagram of Fig. 1 illustrates the interconnection of the above-mentioned INTERMETALL-ICs into one complete remote-control/channel selection operating unit.

Fig. 1: Complete control assembly for a remote-controlled color TV receiver, with the ultrasonic remote control receiver SAA 1130, the character display circuit SAA 1008 and the tuner control and channel storage IC set SAA 1020/SAA 1021, all produced by INTER-METALL

### Control IC SAA 1021

Voltage at the other pins

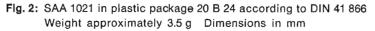

Monolithic integrated circuit in silicon gate technique

| ronuge at the enter price                         | • 11             |                        | •      |

|---------------------------------------------------|------------------|------------------------|--------|

| Output currents                                   | -1 <sub>D</sub>  | 5                      | mA     |

| Ambient operating temperature range               | Tamb             | -20+65                 | °C     |

| Storage temperature range                         | Ts               | - 55 + 125             | °C     |

| <b>Recommended Operating Conditions</b>           |                  |                        |        |

| Supply voltage                                    | -V <sub>DD</sub> | 18 (16.5 19.5)         | V      |

| Input voltages at pins 5 12,<br>14, 19, 20 and 24 | -V1H<br>-V1L     | $\leq 0.8$<br>$\geq 6$ | V<br>V |

| Quartz-controlled clock frequency<br>at pin 2     | f <sub>t</sub>   | 4.4336                 | MHz    |

|                                                   |                  |                        |        |

Vn

v

v

-30...+0.3

# SAA 1020, SAA 1021

| <b>Characteristics</b> at $-V_{DD} = 18$ V, $f_t = 4.4336$ MHz, $T_{amb} = 25$ °C                    |                          |         |    |  |  |

|------------------------------------------------------------------------------------------------------|--------------------------|---------|----|--|--|

| Current consumption                                                                                  | -1 <sub>DD</sub>         | 32      | mA |  |  |

| Voltage drop across the output transistors at $-I_D = 1$ mA, pins 912, 17, 19, 20 and 23             | ∆v                       | < 0.6   | V  |  |  |

| Output frequency pin 23                                                                              | f <sub>FA</sub>          | 19 793  | Hz |  |  |

| Pulse duty factor of the output signal at pin 23                                                     | $t_{ ho}/t_0$            | 1/7 7/1 |    |  |  |

| Storage clock output CP (pin 13) with transistor on the $V_{SS}$ side conducting at $-I_{13} = 1$ mA | ∆V13                     | < 0.4   | ٧  |  |  |

| with transistor on the $V_{DD}$ side conducting at $R_{13/1} = 1.2 \text{ k}\Omega$                  | -V <sub>13</sub>         | > 2     | V  |  |  |

| Data output DA (pin 16) with transistor on the $V_{SS}$ side conducting, at $-I_{16} = 0.2$ mA       | <b>⊿</b> V <sub>16</sub> | < 0.4   | v  |  |  |

| with transistor on the $V_{DD}$ side conducting, at $R_{16/1} = 6 \text{ k}\Omega$                   | -V16                     | > 2     | ۷  |  |  |

### Design and Operation Mode of the SAA 1021

The functioning of the SAA 1021 will be explained with reference to the various pins.

Pin 1 – ground, 0, Vss

Positive terminal of the supply voltage. All voltage levels are related to this potential.

Pin 18 — supply voltage V<sub>DD</sub> Negative terminal of the supply voltage.

Pin 17 - tuning voltage VA

Output for the digitally issued tuning information by means of which the tuning voltage for the variable capitance diodes of the tuner is generated with the aid of a switching stage and an *RC* lowpass filter. Starting with the potential  $V_{SS}$ , this voltage goes negative towards  $V_{DD}$ .

The tuning voltage can be set in 3 968 steps. It is generated by integration in the above-mentioned *RC* lowpass filter from the pulse-modulated output signal of the SAA 1021, pin 17. The modulation process is a combination of pulse duration modulation and the rate multiplier principle. The output frequency remains constant at 558.67 Hz (color sub-carrier frequency of 4.4336 MHz, divided by  $2 \times 3$  968).

Given a tuning voltage rising from zero, we have as the minimum value at the output pin 17 of the SAA 1021 a pulse of  $2 \times 0.5 \,\mu$ s duration to begin with, this duration increasing subsequently in 62 steps of 0.5  $\mu$ s each, to 32  $\mu$ s. With the 63rd step there appears at the output a pulse of 32  $\mu$ s duration, distributed over the 558 Hz period, and a second pulse of  $2 \times 0.5 \,\mu$ s duration which now increases step-wise up to a duration of 32  $\mu$ s. This is followed by two 32  $\mu$ s pulses and one pulse starting with 2 x 0.5  $\mu$ s of step-wise increased duration and so forth. The 6-bit pulse duration modulation is combined with a 6-bit rate multiplier. The advantage of this arrangement is that worst-case ripple in the output signal is reduced by a factor of approximately 16 in comparison with ordinary pulse duration modulation.

#### Pins 9, 11 and 12 - band inputs/outputs

These three outputs supply band data to the tuner and serve as inputs for manual band switching. They are connected to the drain terminals of open-drain output transistors, and the transistor which conducts is always the one whose band has been switched on.

If, for example, in the case of new-programming a channel key, the band is changed at the receiver's front panel, this is done by using the band selection key (Fig. 1) to connect the associated band output to  $V_{SS}$ . This information is at first stored in the SAA 1021 until it is taken over by the storage device SAA 1020 together with the tuning voltage data on completion of a station search or upon actuation of a fine-tuning sensor plate (FT, Fig. 1). However if an ultrasonic program command is given after a band selector key has been depressed, the band data stored in the SAA 1021 are cleared.

If a fourth band is required, e.g. for cable TV, the signal "all three band outputs blocked" may be introduced instead. For the purpose of manual band selection, all three band outputs must then be briefly connected to  $V_{DD}$ .

Pin 20 — Option I: Start of station search (operating with AFC) Option II: Fast tuning (operating without AFC)

This terminal offers two facilities (options), depending upon the design of the TV receiver in question, which are programmed from pin 23. In the case of Option I the key arranged between pin 20 and  $V_{SS}$  serves for initiating the automatic station search operation. Here, pin 23 is the output for fine-tuning data. In the case of Option II, the above-mentioned key serves to initiate a fast search in a manual station search operation. The receiver is run without fine tuning, and pin 23 must be connected to  $V_{SS}$  (Fig. 1).

Programming the channel selection keys - an operation actually to be undertaken only when using the receiver for the first time - can only be carried out at the receiver itself and, in the case of a set designed according to Option I, takes place as follows:

First, a storage location is chosen by actuating a channel key. Then, the band selection key is depressed which corresponds to the band in which the station to be stored is situated. The key "Start" is now depressed and pin 20 is thus briefly connected to  $V_{SS}$ . This initiates the automatic search operation. After this operation has been stopped by the application of a stop signal applied to pin 19, band and tuning voltage data are automatically stored in the SAA 1020, and fine tuning is effected manually by actuating the FT+ or FT- key. If, instead of the station responding first because it requires the lowtest tuning voltage, the user wishes to select a different station, the key "Start" should be actuated once more which will cause the station with the next-higher tuning voltage to be stored, and so forth.

The speed of the automatic station search run in the three bands is adapted to the slope of the tuner's voltage/frequency characteristic. The entire band IV/V is traversed in 14.2 seconds. In band III, five steps are comprised into a single step, so that the band is traversed within 2.84 seconds, while in band I ten steps are comprised into a single step, resulting in a traverse time of 1.42 seconds. Since the tuning voltage, which is integrated by means of the *RC* lowpass filter mentioned in the section "Pin 17", only becomes available after the digital information, the first stop signal appears too late, and the tuning voltage slightly overruns the station. Therefore, the stop signal is automatically followed by a correction run in the reverse sense which takes place with a speed 20 times lower than the search run, so that the discrepancy between digital information and integrated tuning voltage upon a renewed stop amounts to less than half a step. The selected station is only stored in the SAA 1020 after this second stop signal. In the case of the first stop signal, the Low to High transition.

If silent tuning (muting) is envisaged, the data required for this purpose can likewise be derived from pin 20. After the key "Start" is released, pin 20 is connected by means of an integrated transistor to  $V_{SS}$  potential for the duration of the search run.

In the case of a receiver designed according to Option II, the channel selection keys are programmed in a somewhat different manner from that described above. Pin 23 is connected to  $V_{SS}$ , and the TV receiver is not equipped with an AFC facility. At first the relevant channel selection key is operated, than the band selection key, and thereafter the search run is initiated in that the keys M+ or M- are actuated and - temporarily - pin 20 is connected to  $V_{SS}$  at the same time by depressing the "Fast" key. This results in a rate of change of the digital output signal at pin 17 of 90 steps per second. A channel interval is traversed within about two seconds, which enables the user to stop in good time. If the "Fast" button is not depressed, the tuning information varies at seven steps per second, so that fine tuning of the chosen station becomes possible.

When planning an Option II receiver, the designer can choose between various possibilities concerning the layout of the search run controls. The first alternative has been indicated in the description above. As a second alternative, four tuning keys could be provided, i. e. fast forward, slow forward, fast backward and slow backward. Even a four-function lever resembling a gear lever would be feasible.

The M+ and M – commands may be given by means of sensor plates on the receiver (Fig. 1), or ultrasonically (commands Z4 and Z5, see the SAA 1130 data sheet). If the M+ or M – plates are touched continously, the digital tuning data at pin 17 are at first varied by one step, and this is followed by a pause of about 0.6 seconds, whereupon further tuning steps are produced at intervals of about 0.14 seconds. Thus, three ways of varying the tuning voltage are feasible: a single step if the sensor plate is touched for a time under 0.6 seconds, slow variation by continuous touching of the sensor, and fast variation if the sensor M+ or M – and the "Fast" button are actuated simultaneously. The M+ command (corresponding to Z5) is transmitted by long-duration pulses (23.1 ms) from terminal T of the SAA 1130 to the input T of the SAA 1021, while the M – command (corresponding to Z4) is transmitted by short-duration pulses (21.6  $\mu$ s).

The rate of change of the tuning data is adapted to the slope of the tuner's voltage/frequency characteristic also in the Option II TV receiver in that five steps are comprised into one step in the case of band III, and ten steps of the pulse duration modulated signal are comprised into one step in the case of band I.

When used in an Option II receiver the IC set SAA 1020/SAA 1021 may also be programmed for semi-automatic station searching if an external auxiliary circuit ensures that a changeover from a fast rate of tuning data variation to a slow variation rate is triggered by some stop signal, e. g. derived from the synchronising circuit, when a receivable station synchronises deflection. In that case an automatic stop is obtained near the exact station setting, and fine tuning can then be performed manually.

#### Pin 23 – fine tuning output FA, option input

If pin 23 is taken to  $V_{SS}$  (indicated by the switch S1 in Fig. 1), then the IC set SAA 1020/SAA 1021 is programmed for the Option II mode.

In the Option I mode, pin 23 delivers fine-tuning information in the shape of a square wave voltage whose pulse duty factor is variable in seven steps and whose frequency amounts to 19 793 Hz. After amplification in a transistor, shown on the right in Fig. 1, its mean value is obtained by means of an *RC* network and fed to the retuning circuit (AFC).

The user of the TV receiver can make fine-tuning adjustments manually, either by touching the sensor plates FT+ or FT- or, ultrasonically, by the commands Z4 and Z5 (see data sheet SAA 1130). In either case, the information from the output T of the SAA 1130 is transmitted to the input T of the SAA 1021 in pulse shape, the long pulses (> 4 ms) shortening the pulse duration of the square wave voltage at pin 23 by one eighth of the pulse duration of the pin 23 output signal by 1/8 every 0.6 seconds. Altogether, therefore, the pulse duty factor of the fine tuning square wave voltage is variable between 1 :7 and 7 : 1. Manual fine tuning enables the user to deviate from the automatic tuning resulting upon the use of the automatic station searching, and possibly to receive a picture of improved definition.

In connection with the automatic station search, fine tuning fulfils the following function: When the automatic station search is started by actuating the button "Start", the fine tuning voltage is standardised — with a pulse duty factor of the output square wave voltage at pin 23 of 4:4, with a period approximating 50  $\mu$ s.

After every fine tuning step, the new information is immediately accepted by the storage device SAA 1020. If the same channel is selected at a later date, the stored fine tuning level becomes effective again.

#### Pin 24 - input T

As has already been described in connection with pin 23, the SAA 1021 receives fine tuning information via the input T in the Option I mode, and the command for slowly varying the tuning information up or down in the Option II mode.

The commands M+/M - and FT+/FT - are decoded in the ultrasonic receiver IC SAA 1130 and delivered at the T output in the shape of cyclic pulses. In the non-operative condition, the T output of the SAA 1130 is at  $V_{DD}$  potential, and while the above-mentioned commands are being issued the T output supplies High pulses at a frequency of approximately 7.2 Hz. In the case of the command Z4 (SAA 1130) which corresponds to M - or FT - in Fig. 1, the duration of these pulses is 21.6 µs. In the case of command Z5, which corresponds to M + or FT+, the duration of these pulses is 23.1 ms.

### Pin 19 – stop input

In an Option I receiver, this pin serves as input for the stop signal in connection with an automatic station searching operation. In the non-operative condition, Low-potential must be applied to pin 19 ( $V_{DD}$ ). The first stop signal briefly switches the pin 19 High ( $V_{SS}$ ). The trailing edge of the stop signal (HL) changes the direction of the search run, and the leading edge (LH) of the subsequent second stop signal terminates the search.

In an Option II receiver, pin 19 functions as an output which supplies a cyclic output signal at a frequency of 19.79 kHz – provided as a clock signal for the prospektive MNOS store.

Pins 5...8 - program inputs PA ... PD

Information as to which program has been selected is supplied statically in binary-coded form by the program outputs of the SAA 1130, and these outputs are directly connected to the program inputs of the SAA 1021. The table below shows the code. During a read or write cycle, this program information determines the address of the storage device SAA 1020.

Pins 13, 14 and 16 – connections to the storage device SAA 1020

Pin 13 is a push-pull output and supplies 288 pulses at a frequency of 138 kHz to the storage IC SAA 1020 for every write or read cycle.

Pin 14 is an input to be connected to the storage IC SAA 1020.

Pin 16 is a push-pull output, to be connected to the storage IC SAA 1020.

The two signal connections, pins 14 and 16, are closed in the SAA 1021 so as to form a loop. Every time new information is to be written into, or stored information read from, the storage device SAA 1020, the entire contents of the store are turned over once in that a packet of 288 clock pulses is applied to the clock input CP of the SAA 1020. 18-bit words are then read or written sequentially.

| Program<br>number | Code<br>PA | РВ | PC | PD |

|-------------------|------------|----|----|----|

| 1                 | L          | L  | L  | L  |

| 2 .               | н          | L  | L  | L  |

| 3                 | L          | Н  | Ļ  | L  |

| 4                 | н          | н  | L  | L  |

| 5                 | L          | L  | н  | L  |

| 6                 | н          | L  | н  | L  |

| 7                 | L          | Н  | Н  | L  |

| 8                 | н          | н  | Н  | L  |

| 9                 | L          | L  | L  | н  |

| 10                | н          | L  | L  | н  |

| . 11              | L          | н  | L  | н  |

| 12                | н          | н  | L  | н  |

| 13                | L          | L  | Н  | н  |

| 14                | н          | L  | н  | н  |

| 15                | L          | н  | н  | н  |

| 16                | н          | н  | н  | Н  |

Table 1: Input code for the program inputs PA . . . PD of the SAA 1021

### Block Diagram of the SAA 1021

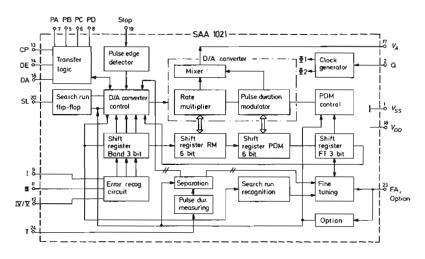

A block diagram of the SAA 1021 is shown in Fig. 3. Its inner layout will be explained below with reference to this diagram.

# SAA 1020, SAA 1021

At pin 2, the SAA 1021 receives a 4.4336 MHz clock, generated by the integrated clock oscillator of the SAA 1130 (Fig. 1). The clock generator integrated in the SAA 1021 comprises essentially a 4-by-1 divider and an 8-by-1 divider, generating a 1 MHz and a 138 kHz two-phase clock. The 138 kHz clock signal has a pulse duty factor of 3 : 5 and clocks the entire IC, except the pulse duration modulator for the tuning voltage.

The D/A converter, which generates the tuning voltage at pin 17, comprises a 6-bit pulse duration modulator and a 6-bit rate multiplier. The D/A converter control determines the rate of change of the tuning voltage in both options in dependence on the band, recognises the stop signal in Option I, generates the up and down commands in Option II (controlled by input T), recognises the start of the station search in Option I and the "Fast" command in Option II (both from pin 20).

The transfer logic effects connection to the storage IC SAA 1020 and consists mainly of a comparator and a word counter. In the comparator, the static program address PA... PD is compared with the word counter information. In this way, the address of the 18-bit word in the 16 x 18 bit shift register SAA 1020 is established and becomes effective during a transmission.

The pulse duration measuring unit connected to the T input recognises the duration of the applied signal (21.6  $\mu$ s or 23.1 ms). On the strength of this information, the fine tuning data are changed in Option I, and the direction in which the tuning information is varied is established in the Option II mode.

Any errors which may be caused in band switching by the simultaneous actuation of several band selection keys are suppressed by an error recognition circuit connected to pins 9, 11 and 12.

An internal normalisation circuit ensures that all counters and stores are set to the desired initial position, and fine tuning to mid-position, when supply voltage  $V_{DD}$  is switched on. A read cycle is automatically initiated, in order to call up the channel selected after the supply voltage has been switched on.

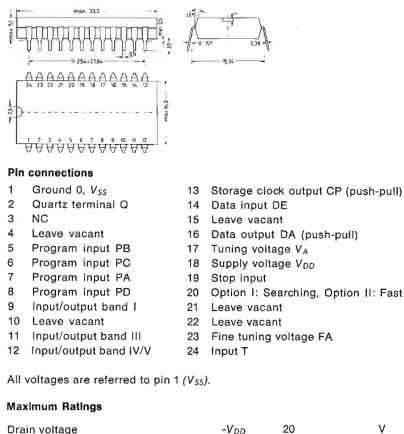

### Storage IC SAA 1020

Monolithic integrated circuit in CMOS technique with low threshold voltage, functioning as a 288-bit shift register capable of storing 16 channel data.

The SAA 1020 can be directly connected to the control IC SAA 1021, without interface. The clock input is terminated with an integrated resistor  $R_{4/1}$ , so that the device remains insensitive also in the case of failure when the supply voltage of the control IC SAA 1021 fails and the push-pull output CP therefore turns high-ohmic. The likewise integrated resistor  $R_{2/1}$  at the data input limits the voltage excursion. The drain connection of an open-drain transistor is the data output.

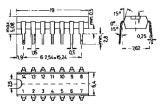

### Flg. 4:

SAA 1020 in plastic package 20 A 16 according to DIN 41 866

Weight approximately 1.2 g Dimensions in mm

### Pin connections

- 1 Ground, V<sub>SS</sub>, substrate

- 2 Data input DE

- 3 Data output DA

- 4 Clock input

- 5...15 NC

- 16 Supply voltage V<sub>B</sub>

All voltages are referred to pin 1 ( $V_{SS}$ ).

## **Maximum Ratings**

| Drain voltage                                                 | -VB              | - 3 +0.3   | V   |

|---------------------------------------------------------------|------------------|------------|-----|

| Input voltages                                                | V2, V4           | - 15 +0.3  | v   |

| Output voltage                                                | V <sub>3</sub>   | ~ 10       | v   |

| Ambient operating temperature range                           | Tomb             | -20+65     | °C  |

| Storage temperature range                                     | Ts               | - 55 + 125 | °C  |

| Recommended Operating Conditions                              |                  |            |     |

| Supply voltage                                                | -V <sub>B</sub>  | 1.2 2      | v   |

| Clock frequency                                               | f <sub>t</sub>   | 140        | kHz |

| <b>Characteristics</b> at $-V_B = 1.5$ V, $T_{amb} = 25$      | o∘C              |            |     |

| Non-operative current consumption                             | -1 <sub>B</sub>  | 10         | μA  |

| Operative current consumption                                 | -1 <sub>B</sub>  | 100        | μA  |

| Input resistances                                             | R <sub>2/1</sub> | 10         | kΩ  |

|                                                               | R4/1             | 2          | kΩ  |

| Saturation current of the output transistor at $-V_B = 1.2$ V | 13               | > 0.2      | mA  |

### Thirty Channel Ultrasonic Transmitter for Remote-Controlled TV Receivers

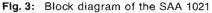

Monolithic integrated circuit in CMOS technique. The SAA 1024 is intended for remote control systems whereby 30 commands are transmitted by means of 30 different ultrasonic frequencies. The SAA 1025, produced by INTERMETALL, is recommended as a suitable receiver.

The SAA 1024 comprises an oscillator circuit, a variable and a fixed frequency divider, a decoder and a command error protection. Fig. 1 shows the circuit diagram of an ultrasonic transmitter based on the SAA 1024.

Fig. 1: Circuit diagram of an ultrasonic transmitter based on the SAA 1024

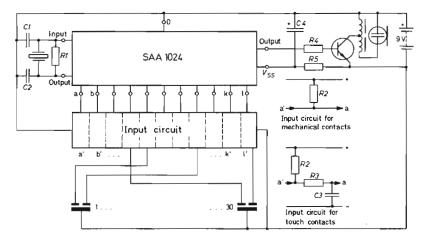

## Flg. 2:

SAA 1024 in dual in-line plastic SOT-38 package 20 A 16 according to DIN 41 866

Weight approximately 1.2 g Dimensions in mm

### Pin connections

- 1 Oscillator input

- 2 Oscillator outpout

- 3 Input a

- 4 Input b

- 5 Input c

- 6 Input d

- 7 Input e

- 8 Input f

- 9 Input g

- 10 Input h

- 11 Input i

- 12 Input k

- 13 Input I

- 14 Vss

- 15 Ultrasonic output

- 16 Ground, 0, substrate

All voltages are referred to pin 16.

## **Maximum Ratings**

| Vss<br>Vn<br> 115 <br>Tamb<br>Ts | $\begin{array}{r} + \ 0.3 \ \dots \ - \ 12 \\ + \ 0.3 \ \dots \ V_{SS} \\ 10 \\ - \ 10 \ \dots \ + \ 60 \\ - \ 30 \ \dots \ + \ 125 \end{array}$ | V<br>mA<br>°C<br>°C                                                                                                                                                                                                                                     |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                                                                                                                                  |                                                                                                                                                                                                                                                         |

| Vss                              | -79                                                                                                                                              | v                                                                                                                                                                                                                                                       |

| ft                               | 4.4336                                                                                                                                           | MHz                                                                                                                                                                                                                                                     |

| C1                               | 39                                                                                                                                               | pF                                                                                                                                                                                                                                                      |

| C2                               | 47                                                                                                                                               | рF                                                                                                                                                                                                                                                      |

| C3                               | 100                                                                                                                                              | pF                                                                                                                                                                                                                                                      |

| C4                               | 47                                                                                                                                               | μF                                                                                                                                                                                                                                                      |

| R1                               | 10 (4.7 22)                                                                                                                                      | MΩ                                                                                                                                                                                                                                                      |

| R2                               | 47                                                                                                                                               | MΩ                                                                                                                                                                                                                                                      |

| R3                               | 1                                                                                                                                                | MΩ                                                                                                                                                                                                                                                      |

| R4                               | 2.7                                                                                                                                              | kΩ                                                                                                                                                                                                                                                      |

|                                  | V <sub>n</sub><br>  1 <sub>15</sub>  <br>T <sub>amb</sub><br>Ts<br>V <sub>SS</sub><br>f <sub>t</sub><br>C1<br>C2<br>C3<br>C4<br>R1<br>R2<br>R3   | $V_n$ + 0.3V <sub>SS</sub> $ I_{15} $ 10 $T_{amb}$ -+ 10+60 $T_s$ - 30+125 $V_{SS}$ 79 $f_t$ 4.4336         C1       39         C2       47         C3       100         C4       47         R1       10 (4.722)         R2       47         R3       1 |

## Characteristics at $V_{SS}$ = -9 V, $T_{amb}$ = $25 \, {}^{\circ}C$

| Ron             | 500                                | Ω                                                                                                            |

|-----------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Rol             | 1.5                                | kΩ                                                                                                           |

| Vin             | - 4.9                              | v                                                                                                            |

| $\Delta V_{in}$ | 0.45                               | v                                                                                                            |

| I <sub>in</sub> | 10                                 | nA                                                                                                           |

| 114             | - 2                                | mA                                                                                                           |

| 114             | 10                                 | μA                                                                                                           |

| see table       | e overleaf                         |                                                                                                              |

|                 | Rol<br>Vin<br>AVin<br> Iin <br>I14 | $ \begin{array}{rcl} R_{OL} & 1.5 \\ V_{in} & -4.9 \\ \Delta V_{in} & 0.45 \\  I_{in}  & 10 \\ \end{array} $ |

R5

47

Ω

## **Table 1:** Ultrasonic Transmission Frequencies at $f_t = 4.4336$ MHz

| Key<br>No. | Fre-<br>quency | x   | a | b | с | d | е | f | g  | h | i | k | I |

|------------|----------------|-----|---|---|---|---|---|---|----|---|---|---|---|

| 1          | 33 945 Hz      | 98  | н | Н | н | н | L | н | н  | L | н | н | н |

| 2          | 34 291 Hz      | 99  | н | н | н | н | L | н | н  | н | н | н | L |

| 3          | 34 638 Hz      | 100 | н | н | н | н | L | н | L  | н | н | н | н |

| 4          | 34 984 Hz      | 101 | н | Н | н | Н | L | н | н  | н | н | Ł | н |

| 5          | 35 330 Hz      | 102 | н | Н | н | н | L | L | н  | н | н | н | н |

| 6          | 35 677 Hz      | 103 | н | н | н | н | L | н | н  | Н | L | н | н |

| 7          | 36 023 Hz      | 104 | L | н | н | н | н | L | н  | н | Н | н | н |

| 8          | 36 370 Hz      | 105 | Ł | н | н | н | н | н | н  | н | L | н | н |

| 9          | 36 716 Hz      | 106 | н | L | н | н | н | L | Н  | Н | н | н | н |

| 10         | 37 062 Hz      | 107 | н | L | н | н | н | н | н  | Н | L | н | н |

| 11         | 37 409 Hz      | 108 | н | н | L | н | Н | L | Н  | Н | Н | н | н |

| 12         | 37 755 Hz      | 109 | н | н | L | н | н | н | н  | н | L | н | н |

| 13         | 38 101 Hz      | 110 | н | н | н | L | н | L | н  | Н | н | н | н |

| 14         | 38 448 Hz      | 111 | н | н | н | L | н | н | н  | н | L | н | н |

| 15         | 38 794 Hz      | 112 | L | н | н | н | н | н | L  | н | н | н | н |

| 16         | 39 141 Hz      | 113 | L | Н | Н | Н | Н | Н | Н  | н | н | L | н |

| 17         | 39 487 Hz      | 114 | н | L | н | н | н | Н | L  | н | н | н | н |

| 18         | 39 833 Hz      | 115 | н | L | н | Н | Н | н | Н  | Н | н | L | Н |

| 19         | 40 180 Hz      | 116 | н | н | L | н | н | н | L  | н | н | н | н |

| 20         | 40 526 Hz      | 117 | н | Н | L | Н | н | Н | н  | н | н | L | н |

| 21         | 40 872 Hz      | 118 | н | н | н | L | н | Н | L  | Н | н | н | н |

| 22         | 41 219 Hz      | 119 | н | н | н | L | н | Н | Н  | н | н | L | Н |

| 23         | 41 565 Hz      | 120 | L | Н | Н | Н | н | Н | н  | L | н | н | н |

| 24         | 41 912 Hz      | 121 | L | н | н | н | Н | н | н  | н | Н | н | L |

| 25         | 42 258 Hz      | 122 | н | L | Н | Н | Н | Н | Н  | L | н | н | Н |

| 26         | 42 604 Hz      | 123 | н | L | н | Н | Н | Н | н  | Н | Н | н | L |

| 27         | 42 951 Hz      | 124 | н | Н | L | Н | н | Н | Н  | L | н | Н | Н |

| 28         | 43 297 Hz      | 125 | н | Н | L | Н | Н | Н | н  | н | Н | Н | L |

| 29         | 43 643 Hz      | 126 | н | н | н | L | н | Н | H. | L | н | Щ | Н |

| 30         | 43 990 Hz      | 127 | н | н | н | L | н | н | Н  | Н | н | н | L |

### Design and Operation Mode

The table shows the 30 ultrasonic transmission frequencies used in the wireless transmission of remote control commands to the TV receiver. These frequencies are derived from the frequency of an SC-crystal controlled oscillator with the aid of a variable frequency divider operating on the blanking principle. This is accomplished in that 1...30 pulses of every 128 out of 4.4336 MHz pulses are blanked out. The variable divider is preceded by a flip-flop which halves the SC frequency. The variable divider is followed by a fixed divider which divides by 50. It reduces the jitter, which is unavoidable when using the blanking principle, to negligible values. The expression for the ultrasonic output frequency is

$$f_u = \frac{\mathbf{x} \cdot f_t}{12\,800}$$

wherein x = 98 to 127. i. e. (128 - 30) to (128 - 1) and  $f_t = 4.4336$  MHz (sub-carrier frequency). The space between two adjacent ultrasonic frequencies is 346.4 Hz.

Upon actuation of one of the double touch contacts 1 to 30 one of the control inputs a...e and f...1 are simultaneously addressed. In the decoder these input signals are converted into 5-bit words and applied to the variable divider which will then generate the desired ultrasonic frequency.

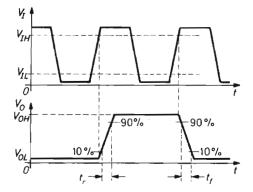

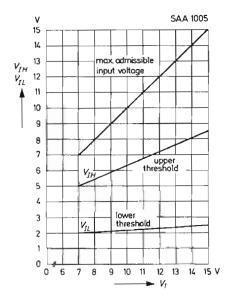

The command error protection defines any actuation whereby one of the control inputs a . . . e and f . . . I are addressed inaccurately as a command error. Under these conditions the oscillator will not start to operate, and the frequency divider is held in a defined position. The same applies when none of the touch contacts is touched. Consumption under these standby conditions is very low, so that ultrasonic transmitter need never be switched off. The selected frequency appears at the ultrasonic output when the threshold voltage is exceeded at the two control inputs. A threshold voltage hysteresis ensures that AC voltages which may be superimposed on the input voltage cannot falsify the actuation. The RC networks R3, C3 (Fig. 1) protect the inputs from interference and from damage through electrostatic discharges. These RC networks may be omitted if mechanical actuated contacts are used. In this case the value of resistor R2 should be 47 k $\Omega$ .

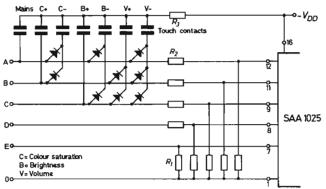

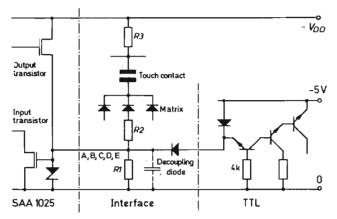

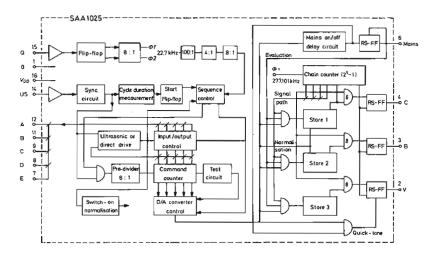

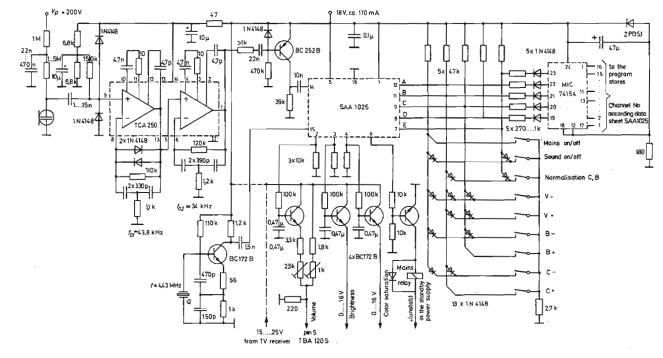

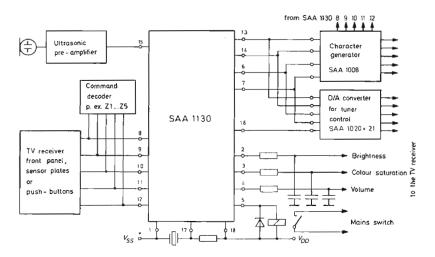

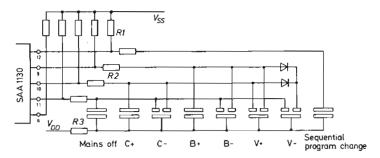

### Thirty Channel Ultrasonic Receiver for Remote-Controlled TV Receivers

Monolithic integrated MOS-circuit in silicon-gate technique. The SAA 1025 is intended for remote control systems in which 30 different ultrasonic frequencies are used to transmit 30 control commands. The recommended transmitter is the SAA 1024 produced by INTERMETALL.

The SAA 1025 measures the frequency of the arriving signal by counting the cycles during a fixed measuring time determined by crystal. Evaluation happens only if two succeeding test cycles give the same result. All ultrasonic commands are converted into a coded 5-bit output signal and issued in pulsed form. Nine of the thirty commands are used internally of the SAA 1025 and serve e.g. for controlling the D/A-converter. The further 21 commands are for free application. Sixteen different TV channels are selectable if a 1 out of 16-decoder is connected to the outputs. For storage the channel information, e.g. the integrated circuits SAS 560 S or SAS 570 S may be used.

Signals for controlling three analogue values, e.g. volume, brightness and colour saturation, are stored in the SAA 1025 and continuously delivered in the shape of square wave voltages. The pulse duty factor of these square wave voltages determines the level of the analog value.

Every control command can also be given directly into the IC.

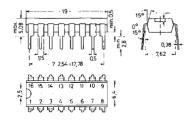

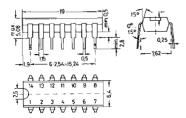

Fig. 1: SAA 1025 in dual in-line plastic SOT-38 package 20 A 16 according to DIN 41 866

Weight approximately 1.2 g Dimensions in mm

### Pin connections

- 1 Ground, 0, V<sub>SS</sub>

- 2 Volume output V

- 3 Brigthness output B

- 4 Colour saturation output C

- 5 V<sub>SS</sub>

- 6 Mains switch output

- 7 In/output E-bit

- 8 In/output D-bit

- 9 In/output C-bit

- 10 Option

- 11 In/output B-bit

- 12 In/output A-bit

- 13 Leave vacant! Test pin

- 14 Ultrasonic input

- 15 Clock input Q

- 16 Supply voltage VDD

All voltages are referred to pin 1.

## **Maximum Ratings**

| Drain voltage                  | -V <sub>DD</sub> | 20         | V  |

|--------------------------------|------------------|------------|----|

| Ciock voltage, peak-to-peak    | -Vt              | 15         | v  |

| Voltage at the other pins      | Vn               | - 30 + 0.3 | v  |

| Drain currents, pins 24, and 6 | -1 <sub>D</sub>  | 5          | mA |

| Ambient operating temp. range  | Tamb             | - 20 + 65  | °C |

| Storage temperature range      | Ts               | - 55 + 125 | °C |

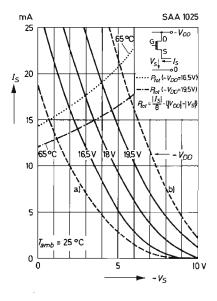

### **Recommended Operating Conditions**

| Drain voltage                           | -V <sub>DD</sub> | 18 (16.5 19.5)        | V   |

|-----------------------------------------|------------------|-----------------------|-----|

| Ultrasonic input voltage, peak-to-peak  | -V14             | 0.5 V V <sub>DD</sub> |     |

| Input voltage for direct commands       | -ViH             | < 0.8                 | V   |

| Inputs A E                              | -VIL             | > 4                   | v   |

| Clock voltage, sinusoidal, peak-to-peak | Vt               | 48                    | V   |

| Clock frequency (sub-carrier)           | . f <sub>t</sub> | 4.4336                | MHz |

## Characteristics at -V<sub>DD</sub> = 18 V, $T_{omb} = 25 \ ^{\circ}\text{C}$

| Output resistance with current<br>flowing, pins 24 and 6 | r <sub>on</sub>    | <1            | kΩ  |

|----------------------------------------------------------|--------------------|---------------|-----|

| Pulse duty factor of the output signal, pins 2 4         | $t_P/t_0$          | 1/30 30/1     |     |

| Output frequency, pins 24                                | fout               | 8.99          | kHz |

| Switching time per step                                  | ti                 | 184.8         | ms  |

| ON and OFF delay<br>in mains and sound controlling       | t <sub>mains</sub> | 66 <b>9.8</b> | ms  |

| Ultransmin imput fragmannias                             |                    | le everleef   |     |

Ultrasonic input frequencies at  $f_t = 4.4336$  MHz

see table overleaf

| Table 1: Ultrasonic I | nput Frequencies | at $f_t = 4.4336$ MHz |

|-----------------------|------------------|-----------------------|

|-----------------------|------------------|-----------------------|

| n  | Frequency    | Command          | Cod<br>E | e<br>A | в | С | D |

|----|--------------|------------------|----------|--------|---|---|---|

| 1  | 33 944,89 Hz | Mains On/Off     | н        | L      | н | н | н |

| 2  | 34 291,21 Hz | Sound Off        | L        | L      | н | н | н |

| 3  | 34 637,65 Hz | Colour+          | н        | Н      | L | Н | н |

| 4  | 34 984,02 Hz | Normalisation 1) | L        | н      | L | н | н |

| 5  | 35 330,40 Hz | Colour –         | н        | L      | L | н | Н |

| 6  | 35 676,78 Hz | Z1               | L        | L      | L | н | Н |

| 7  | 36 023,15 Hz | Brightness+      | н        | н      | н | L | н |

| 8  | 36 369,53 Hz | Z2               | L        | н      | н | L | Н |

| 9  | 36 715,91 Hz | Brightness —     | н        | L      | Н | L | Н |

| 10 | 37 062,28 Hz | Z3               | L        | L      | н | L | Н |

| 11 | 37 408,66 Hz | Volume+          | н        | н      | L | L | н |

| 12 | 37 755,03 Hz | Z4               | L        | Н      | L | L | н |

| 13 | 38 101,41 Hz | Volume           | н        | L      | L | L | Н |

| 14 | 38 447,79 Hz | Z5               | L        | L      | L | L | Н |

| 15 | 38 794,16 Hz | Channel 1        | н        | н      | н | Н | L |

| 16 | 39 140,54 Hz | Channel 2        | L        | н      | н | н | L |

| 17 | 39 486,92 Hz | Channel 3        | н        | L      | Н | н | L |

| 18 | 39 833,29 Hz | Channel 4        | L        | L      | Н | н | L |

| 19 | 40 179,67 Hz | Channel 5        | н        | н      | L | н | L |

| 20 | 40 526,05 Hz | Channel 6        | L        | Н      | L | Н | L |

| 21 | 40 872,42 Hz | Channel 7        | н        | L      | L | н | L |

| 22 | 41 218,80 Hz | Channel 8        | L        | L      | L | н | L |

| 23 | 41 565,18 Hz | Channel 9        | н        | н      | н | L | L |

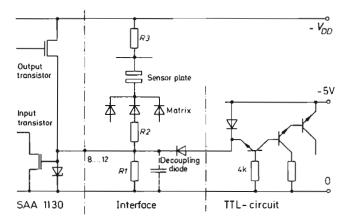

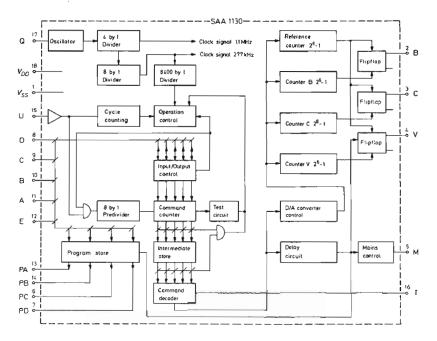

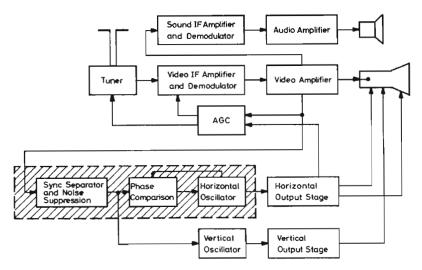

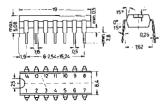

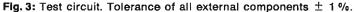

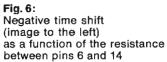

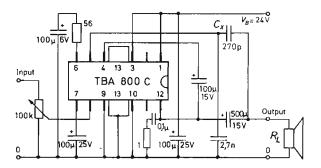

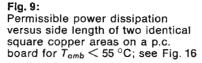

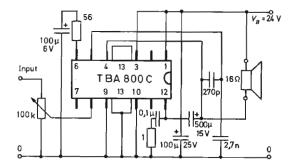

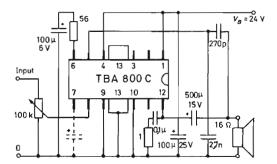

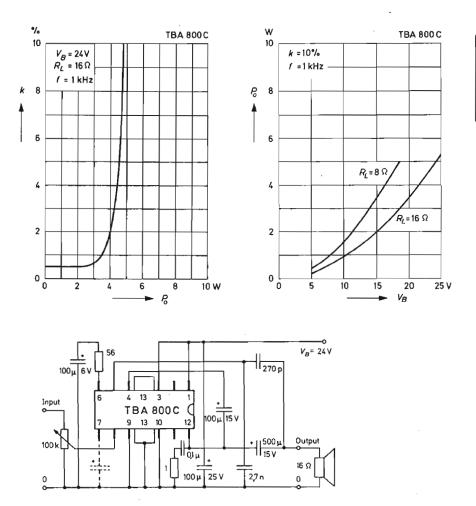

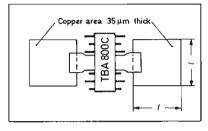

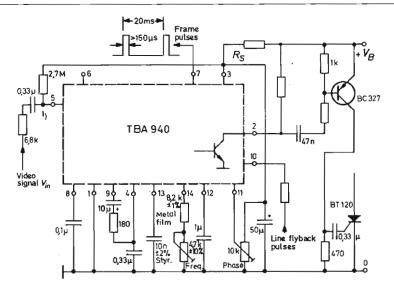

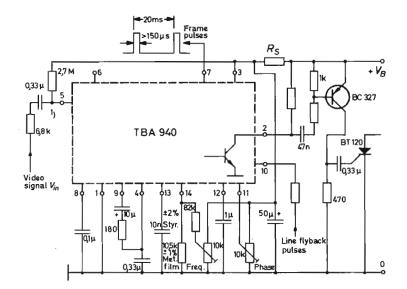

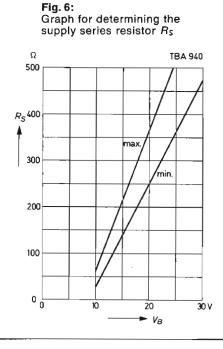

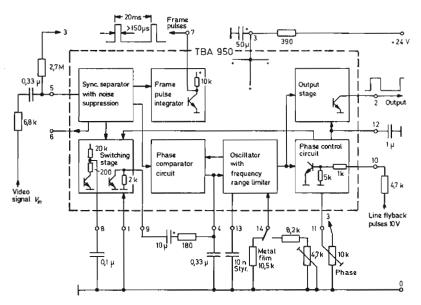

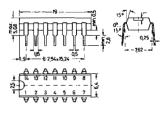

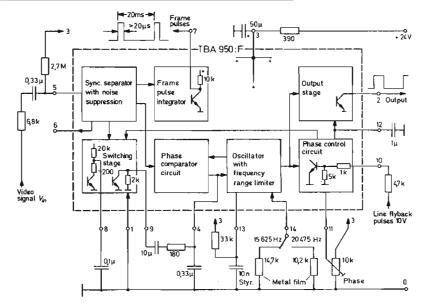

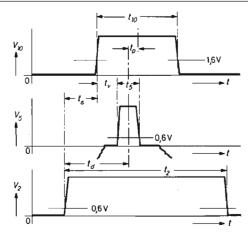

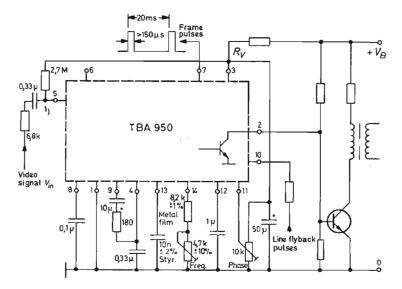

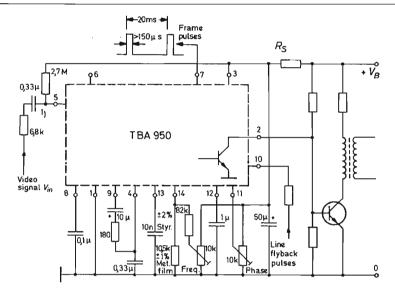

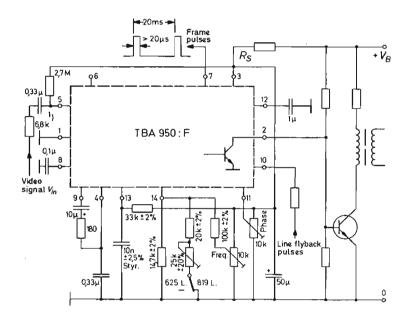

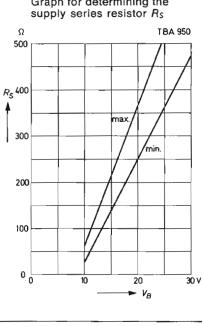

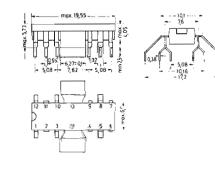

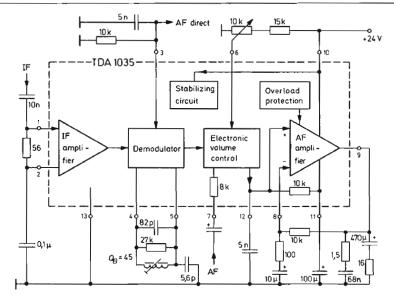

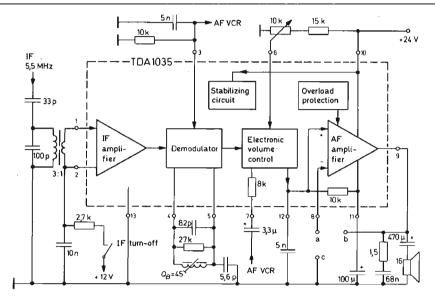

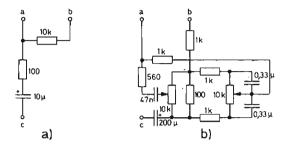

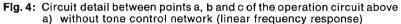

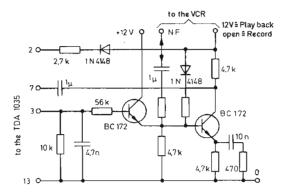

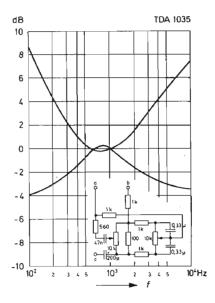

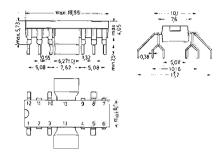

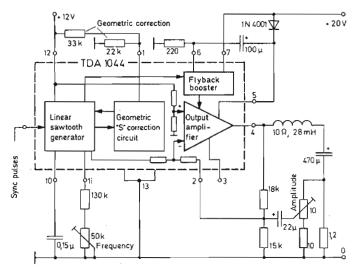

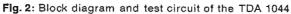

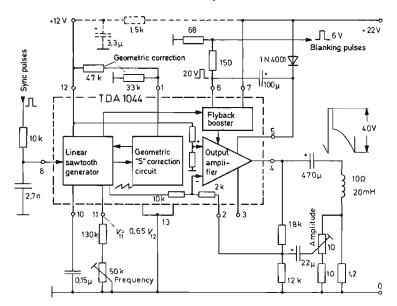

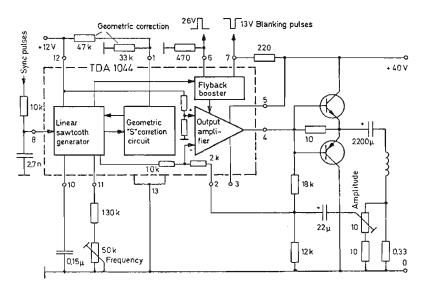

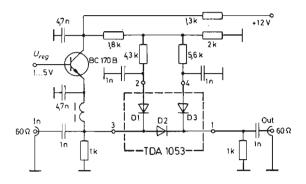

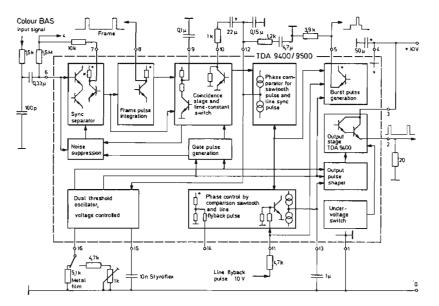

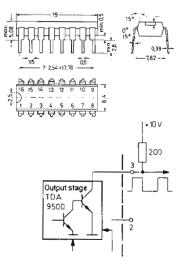

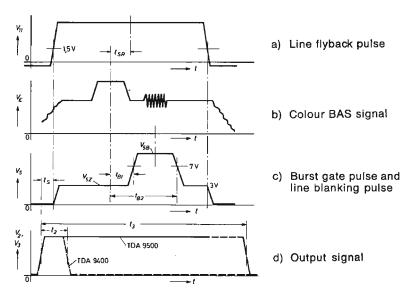

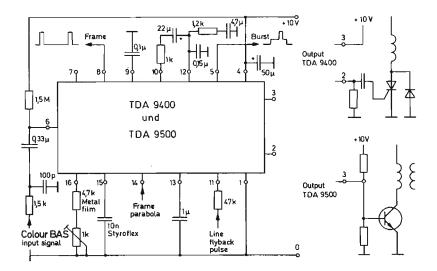

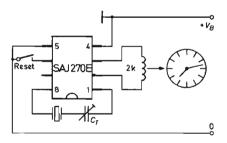

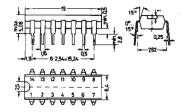

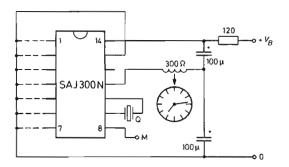

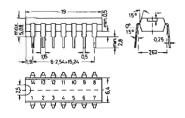

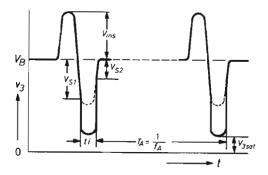

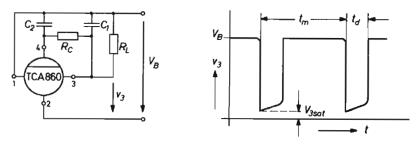

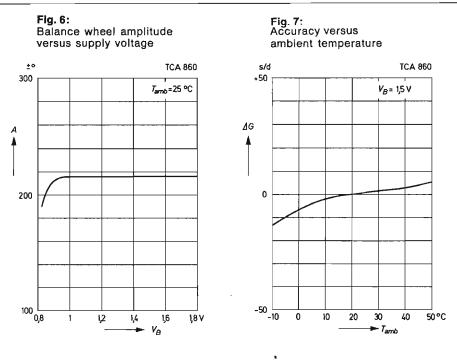

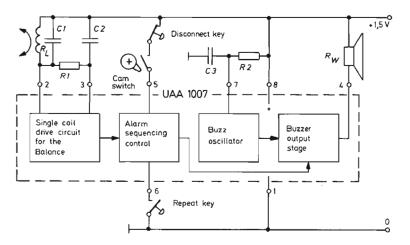

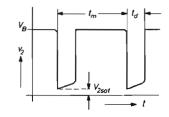

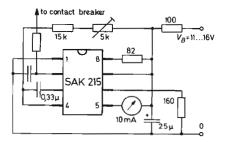

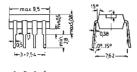

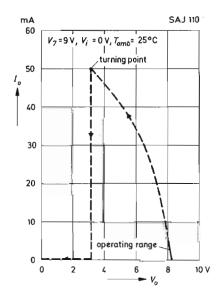

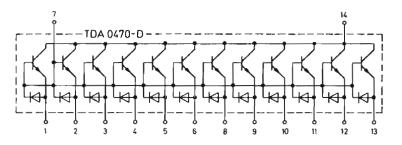

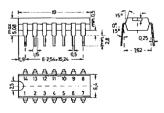

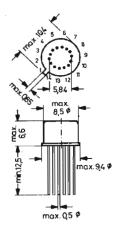

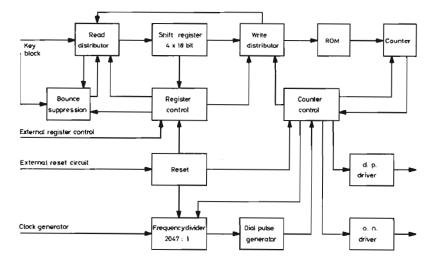

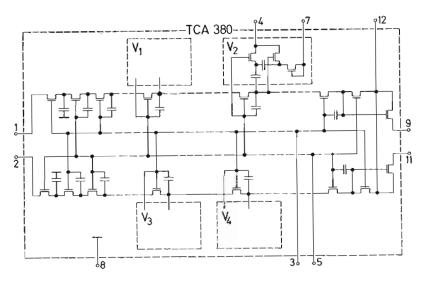

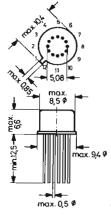

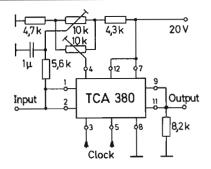

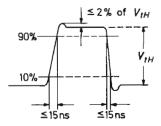

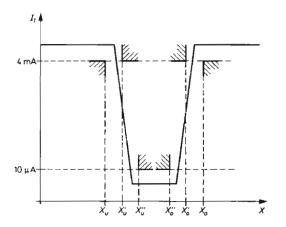

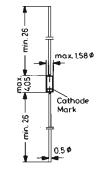

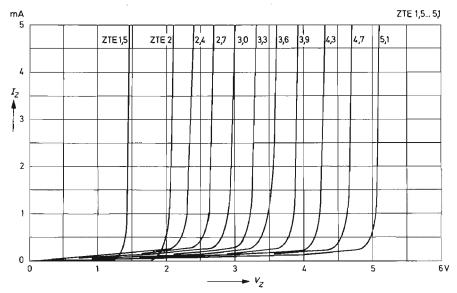

| 24 | 41 911,55 Hz | Channel 10       | L        | н      | н | L | L |