# **VIDEO PRODUCTS**

**APPLICATION MANUAL**

1st EDITION

# **VIDEO PRODUCTS**

# **APPLICATION MANUAL**

1st EDITION

**JULY 1991**

SCAN by F1CJL . January 2020.

# USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein: 1. Life support devices or systems are those which (a) are 2. A critical component is any component of a life support intended for surgical implant into the body, or (b) support device or system whose failure to perform can reasonor sustain life, and whose failure to perform, when properably be expected to cause the failure of the life support ly used in accordance with instructions for use provided device or system, or to affect its safety or effectiveness. with the product, can be reasonably expected to result in significant injury to the user.

# **TABLE OF CONTENTS**

| INTRODUCTION         | Page | 4 |

|----------------------|------|---|

| ALPHANUMERICAL INDEX |      | 5 |

| APPLICATION NOTES    |      | 7 |

|                      |      |   |

## INTRODUCTION

SGS-THOMSON's dedicated video product range is now so extensive that it has been necessary to divide the databook into two volumes: one for power devices and graphic circuits and one for signal devices. Application notes for video products have been gathered together in the video products Application Manual.

Volume 1, Signal Processing Products, covers chroma and video ICs, single-chip processors, video switch matrices and other signal level parts. In this area the company specializes in offering complete solutions all of the ICs needed for a specific TV or monitor chassis type and gives special attention to the basic solutions. Much of the knowhow in this field has been gained in the demanding Asia/Pacific market for the cost effective aspect, and in western Europe for PAL/SECAM multistandard design, placing SGS-THOMSON in a very strong position in the emergent East European market the new frontier in consumer electronics.

Volume 2, Power & Graphics Products, covers power ICs such as deflection boosters and sound channels, plus other ICs for graphics monitor deflection applications. In the monitor market SGS-THOMSON is the recognized world leader; in fact today 7 out of 10 monitors produced in the world include SGS-THOMSON ICs. Power ICs in general are a traditional specialty of the company, which began producing monolithic power amplifiers in the 60's and has remained at the forefront of power technology development ever since.

With these two volumes SGS-THOMSON Microelectronics proposes a dedicated video product range that satisfies virtually every need in television, monitor, VCR and related applications. And if you don't find the product you are looking for in these volumes contact the nearest SGS-THOMSON office; it may be that the product you want is included in other books covering micros, memories, standard ICs or discretes.

The Video Products Application Manual is part of the comprehensive technical support offered by SGS-THOMSON's Video Division to make application design fast and productive. This support also includes PC design aids and evaluation boards.

# ALPHANUMERICAL INDEX \_\_\_\_\_

| Application<br>Notes<br>Number | Description                                                 | Page<br>Number |

|--------------------------------|-------------------------------------------------------------|----------------|

| AN373                          | Vertical Delection Circuit for TV & Monitor                 | 9              |

| AN374                          | TDA8102A H/V Processor for TTL VDU                          | 33             |

| AN376                          | TEA2260/61 High Performance Driver Circuits for SMPS        | 49             |

| AN377                          | TEA5101A RGB High Voltage Switching Circuit                 | 83             |

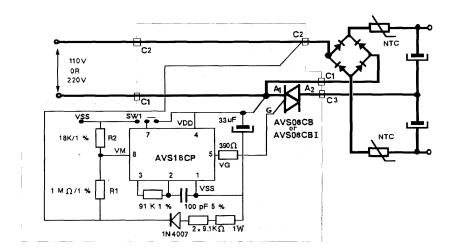

| AN389                          | AN Automatic Line Voltage Switching Circuit                 | 107            |

| AN390                          | How to USE the AVS Kit                                      | 113            |

| AN391                          | How to USE the AVS08                                        | 117            |

| AN393                          | TV E/W Correction Circuits                                  | 121            |

| AN406                          | TEA2018A/19 Flyback Switch Mode Power Supply Implementation | 157            |

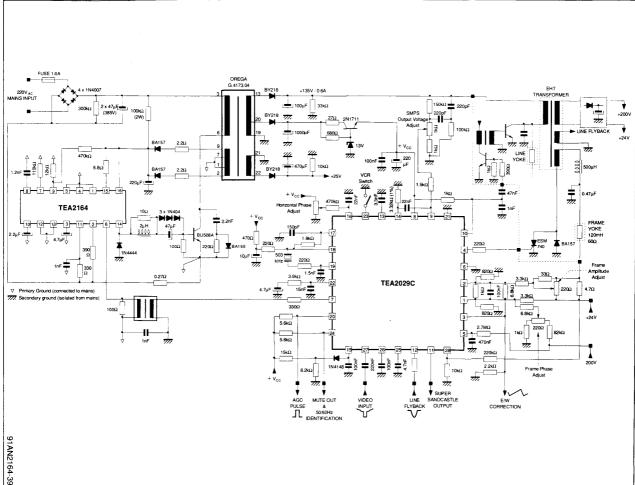

| AN407                          | TEA2028/TEA2029                                             | 195            |

| AN408                          | TEA5170 Secondary Controller for Master - Slave Structure   | 251            |

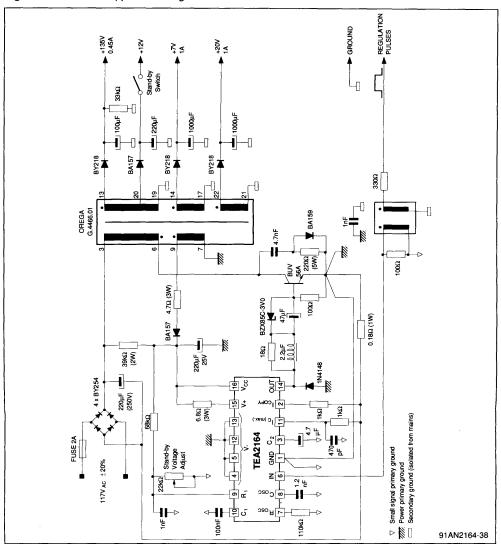

| AN409                          | TEA2164 Master - Slave SMPS for TV & Video Application      | 265            |

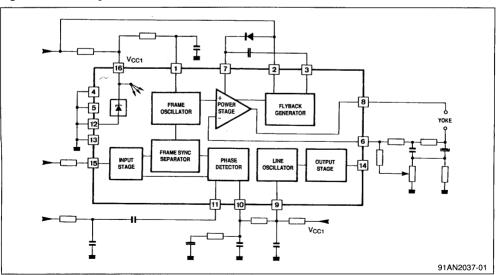

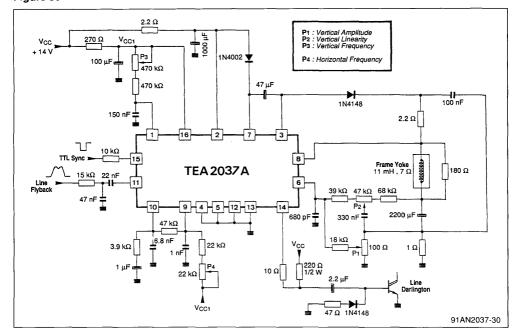

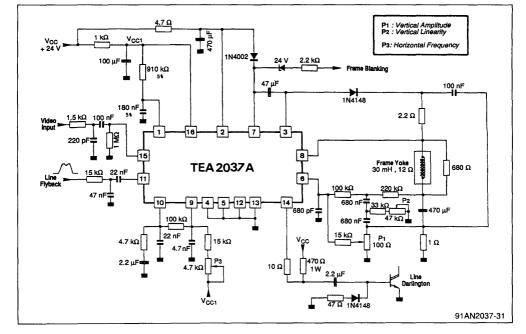

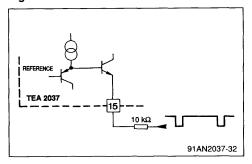

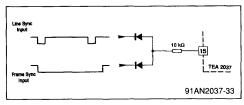

| AN410                          | TEA2037 Horizontal & Vertical Deflection Circuit            | 295            |

# **APPLICATION NOTES**

## **APPLICATION NOTE**

# **VERTICAL DEFLECTION CIRCUITS FOR TV & MONITOR**

by Alessandro MESSI

#### INDEX

| 1.   | Introduction                                                  | 1/24  |

|------|---------------------------------------------------------------|-------|

| 2.   | Oscillator                                                    | 2/24  |

| 3.   | Ramp Generator                                                | 3/24  |

| 4.   | Blanking Generator and CRT Protection                         | 4/24  |

|      | Power Amplifier Stage                                         |       |

| 6.   | Thermal Protection                                            | 5/24  |

| 7.   | Flyback Behaviour                                             | 5/24  |

| 8.   | Current - Voltage Characteristics of the Recirculating Diodes | 11/24 |

| 9.   | Calculation Procedure of the Flyback Duration                 | 12/24 |

| 10.  | Application Information                                       | 12/24 |

| 11.  | Supply Voltage Calculation                                    | 14/24 |

| 12.  | Calculation of Midpoint and Gain                              | 17/24 |

| 13.  | Monitor Applications                                          | 20/24 |

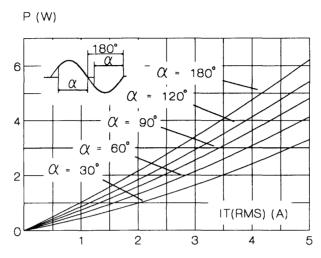

| 14.  | Power Dissipation                                             | 20/24 |

| 1.5. | Blanking Pulse Duration Adjustment                            | 22/24 |

| 16.  | Linearity Adjustment                                          | 22/24 |

| 17.  | Facilities and Improvements                                   | 23/24 |

| 18.  | General Application and Layout Hints                          | 24/24 |

| 19.  | References                                                    | 24/24 |

## 1. INTRODUCTION

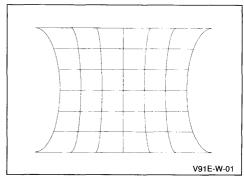

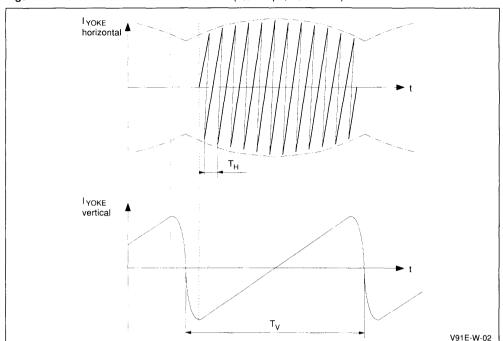

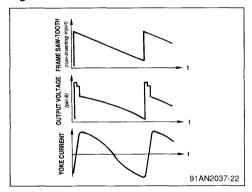

In a general way we can define vertical stages circuits able to deliver a current ramp suitable to drive the vertical deflection yoke.

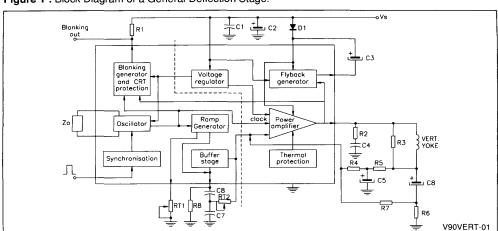

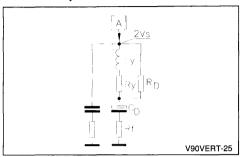

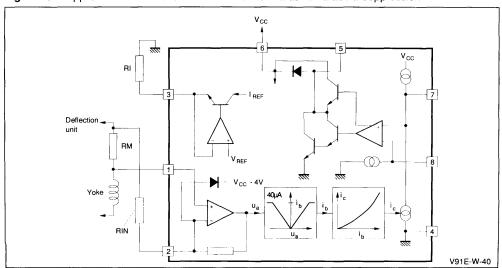

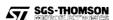

In Figure 1 is represented the more general possible block diagram of a device performing the vertical deflection.

Figure 1: Block Diagram of a General Deflection Stage.

Such a device will be called "complete vertical stage" because it can be simply driven by a synchronization pulse and it comprises all the circuitry necessary to perform the vertical deflection that is: oscillator, voltage ramp generator, blanking genetor, output power and flyback generator.

At the right side of the dotted line in Figure 1 is represented the circuitry characterizing a "vertical output stage". This kind of device comprises only the power stages and it has to be driven by a voltage sawtooth generated by a previous circuit (for example a horizontal and vertical synchronization stage.

In the first class there are the following devices: TDA1170D, TDA1170N, TDA1170S, TDA1175, TDA1670A, TDA1675, TDA1670A, TDA1872A, TDA8176.

In the second class there are: TDA2170, TDA2270, TDA8170, TDA8172, TDA8173, TDA8175,

TDA8178, TDA8179.

There is also a third class of vertical stages comprising the voltage ramp generator but without the oscillator; these circuits must be driven by an already synchronized pulse. In this third class there are: TDA1771 and TDA8174.

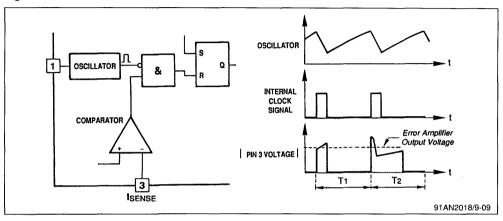

#### 2. OSCILLATOR

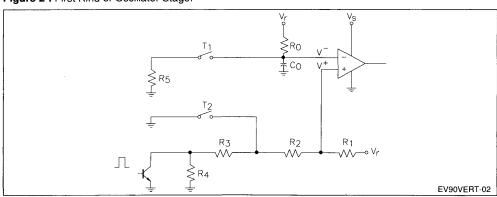

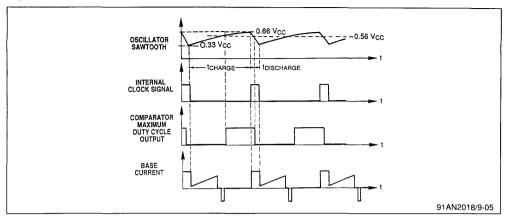

There are two different kinds of oscillator stages used in SGS-THOMSON complete vertical deflections, one is used in TDA1170D, TDA1170N, TDA1170S, TDA1175 and TDA8176, the other in TDA1670A, TDA1675, TDA1170A and TDA1872A. The principle of the first kind of oscillator is represented in Figure 2.

The following explanations will be the more general possible; we shall inform the reader when we refer to a particular device.

Figure 2: First Kind of Oscillator Stage.

When the switches  $T_1$  and  $T_2$  are opened the  $C_0$  capacitor charges exponentially through  $R_0$  to the value  $V^+_{(MAX)}$  determined by the integrated resistors  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$ . At this point the switches are closed, short-circuiting  $R_3$  and  $R_4$ , so the volt-

age at the non-inverting input becomes  $V^{+}_{(\text{MIN})}.$  The capacitor  $C_{O}$  discharges to this value through the integrated resistor  $R_{5}.$

The free running frequency can be easily calculated resulting in :

$$T_{O} = R_{O} \cdot C_{O} \cdot log \frac{V_{R} - V^{+}_{(MIN)}}{V_{R} - V^{+}_{(MAX)}} + R_{5} \cdot C_{O} \cdot log \frac{V^{+}_{(MAX)}}{V^{+}_{(MIN)}}$$

(1)

$$f_{O} = \frac{1}{T_{O}}$$

with  $R_O$  = 360  $k\Omega$  and  $C_O$  = 100 nF, it results in 43.7 Hz.

The oscillator synchronization is obtained reducing the superior threshold  $V^{+}_{(MAX)}$  short-circuiting the

R<sub>4</sub> resistor when a vertical synchronization pulse occurs.

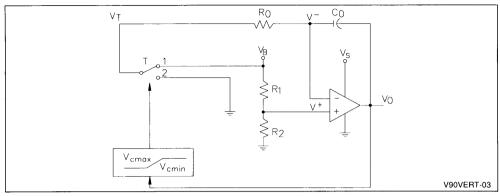

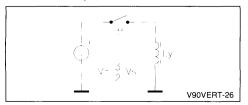

The second kind of oscillator is represented in Figure 3.

Figure 3: Second Kind of Oscillator Stage.

When the switch T is in position 2, a constant current  $I_{CO} = V^{\top}/R_O$  flows through  $C_O$  charging it with a voltage ramp. When the voltage  $V_O$  reaches  $V_{O(MAX)}$ , T passes in position 1, so a constant current  $I_{CO} = (V_B \cdot V^{\top})/R_O$  discharges the capacitor causing the inversion of the voltage ramp slope

at the output  $V_O$  ( t ). The discharges stops when  $V_O$  reaches the value  $V_{O(MIN)}$  and the cycle takes place again.

It is possible to calculate the free running frequency  $f_{\text{O}}$  with the following formula :

$$T_{O} = \frac{(V_{O(MAX)} - V_{O(MIN)}) \cdot R_{O} \cdot C_{O}}{V^{-}} + \frac{(V_{O(MAX)} - V_{O(MIN)}) \cdot R_{O} \cdot C_{O}}{V_{B} - V^{-}}$$

(2)

with  $V_{O(MAX)}$  -  $V_{O(MiN)}$  = 3.9V,  $V_B$  = 6.5V,  $V_C$  = 0.445V,  $R_O$  = 7.5k $\Omega$  and  $C_O$  = 330nF it results in :  $f_O$  = 43.8Hz.

The oscillator synchronization is still obtained in the above mentioned way.

In order to guarantee a minimum pull-in range of 14Hz the threshold value has been chosen in  $V_P = 4.3V$ .

The spread of the free running frequency in this

kind of oscillator is very low because it mainly depends from the threshold values  $V_{O(MAX)}$ ,  $V_{O(MIN)}$  and V that are determined by resistor rates that can be done very precise.

#### 3. RAMP GENERATOR

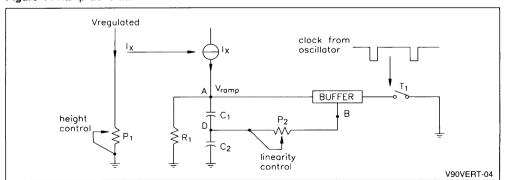

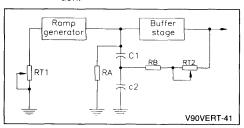

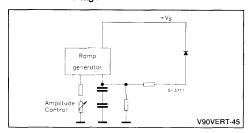

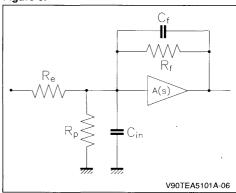

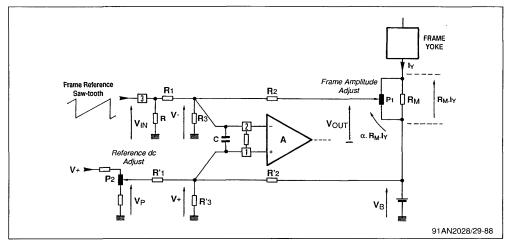

The ramp generator is conceptually represented in Figure 4.

Figure 4: Ramp Generator.

The Voltage ramp is obtained charging the group  $R_1$ ,  $C_1$  and  $C_2$  with a constant current  $I_X$ .

It is easy to calculate the voltage  $V_{\mbox{\scriptsize RAMP}}$  That results in :

$$V_{RAMP}(t) = (V_{(MIN)} - R_1 \cdot I_X) e^{-\frac{t}{R_1 \cdot C}} + R_1 \cdot I_X$$

(3)

where  $V_{(MIN)}$  is the voltage in A when the charge starts and C is the series of  $C_1$  and  $C_2$ .

The resistor  $R_1$  is necessary to give a "C correction" to the voltage ramp. The ramp amplitude is determined by  $I_X = V_{REG} / P_1$ , so the potentiometer  $P_1$  is necessary to perform the height control.

The voltage ramp is then transferred on a low impedence in B through a buffer stage.

Te P2 potentiometer connected between D and B performs the ramp linearity control or "S correction" that is necessary to have a correct reproduction of the images on the TV set.

The voltage ramp in B grows up until the switch  $T_1$  is closed by a clock pulse coming from the oscillator; in this way the capacitors discharge fastly to  $V_{(\text{MIN})}$  that is dependent upon the saturation voltage of the transistor that realizes the switch.

At this point the exponential charge takes place again.

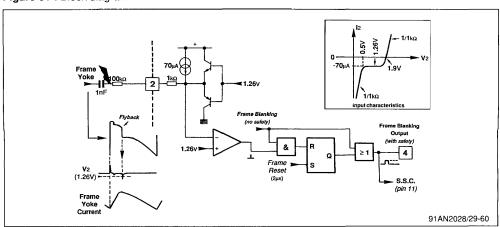

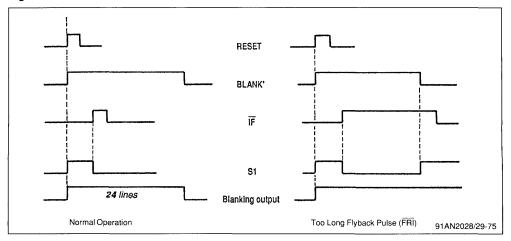

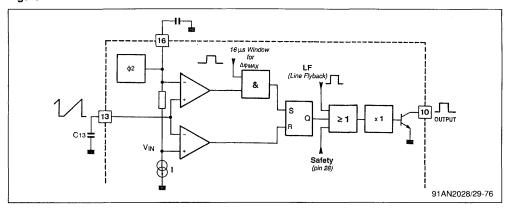

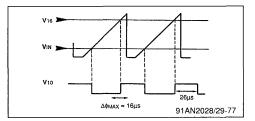

# 4. BLANKING GENERATOR AND CRT PROTECTION

This circuit senses the presence of the clock pulse **Figure 5**: Amplifier Stage.

coming from the oscillator stage and the flyback pulse on the yoke. If both of them are present a blanking pulse is generated able to blank the CRT during the retrace period. The duration of this pulse is the same of the one coming from the oscillator. If for any reason the vertical deflection would fail, for instance for a short circuit or an open circuit of the yoke, the absence of the flyback pulse puts the circuit in such a condition that a continuous vertical blanking is generated in order to protect the CRT against eventual damages.

This circuit is available only in the following devices: TDA1670A, TDA1675, TDA1770A and TDA1872A.

The stages we will consider starting from this point are common both to complete vertical stages and vertical output stages.

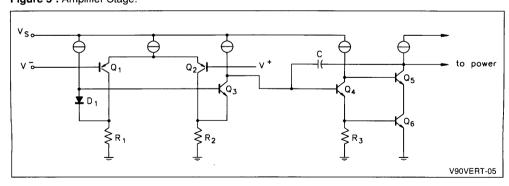

#### 5. POWER AMPLIFIER STAGE

This stage can be divided into two distinct parts: the amplifier circuit and the output power.

The amplifier is realized with a differential circuit; a schematic diagram is represented in Figure 5.

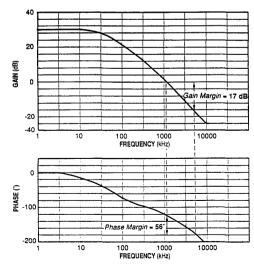

The open-loop gain of the circuit is variable from 60dB to 90dB for the different integrated circuits. The compensation capacitor C determines the dominant pole of the amplifier. In order to obtain a dominant pole in the range of 400Hz, the capacitor

must be of about 10pF.

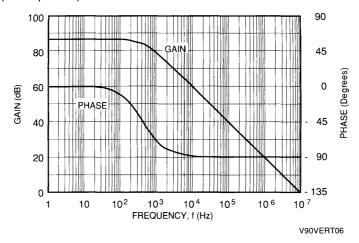

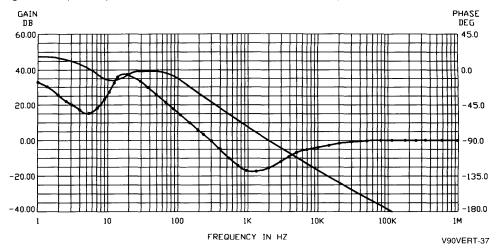

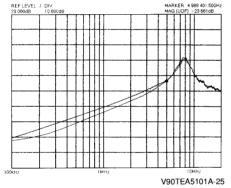

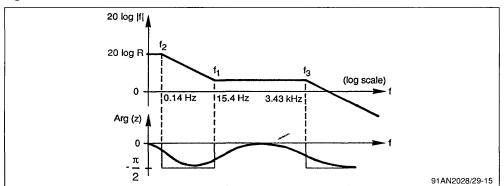

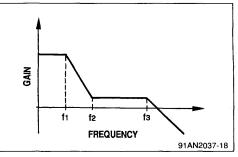

As an example in Figure 6 is represented the boole diagram of the amplifier open loop gain for TDA8172.

Figure 6: Amplifier Open Loop Gain and Phase.

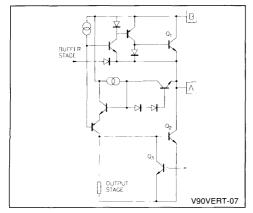

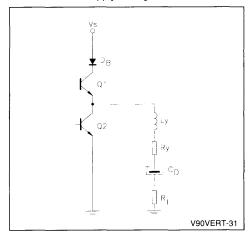

The output power stage is designed in order to deliver to the yoke a vertical deflection current from 1 to 2 Apeak, depending upon the different devices, and able to support flyback voltages up to 60V. A typical output stage is depicted in Figure 7.

Figure 7: Power Stage.

The upper power transistor  $Q_1$  conducts during the first part of the scanning period when the vertical deflection current is flowing from the supply voltage into the yoke; when the current becomes negative, that is it comes out of the yoke, it flows through the lower power transistor  $Q_2$ . The circuit connected between the two output transistors is necessary to avoid distortion of the current at the crossing of

zero, when  $Q_1$  is turned off and  $Q_2$  is turned on. When the flyback begins,  $Q_2$  is switched-off by  $Q_3$  in order to make it able to support the high voltage of the flyback pulse.

The circuit behaviour during flyback is explained in chapter 7.

#### 6. THERMAL PROTECTION

The thermal protection is available in all the devices except the TDA1170 family and the TDA8176.

This circuit is usefull to avoid damages at the integrated circuit due to a too high junction temperature caused by an incorrect working condition.

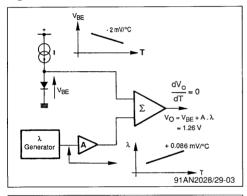

It is possible to sense the silicon temperature because the transistor  $V_{BE}$  varies of - 2 mV/  $^{\circ}$ C, so a temperature variation can be reconducted to a voltage variation.

If the temperature increases and it is reaching 150°C, the integrated circuit output is shut down by putting off the current sources of the power stage.

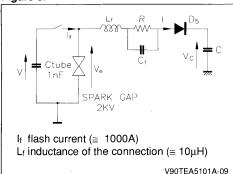

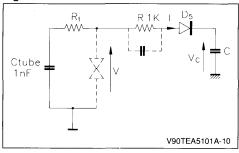

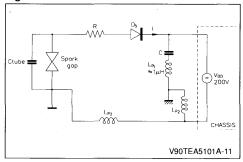

#### 7. FLYBACK BEHAVIOUR

In order to obtain sufficiently short flyback times, a voltage greather than the scanning voltage must be applied to the deflection yoke.

By using a flyback generator, the yoke is only supplied with a voltage close to double the supply during flyback.

Thus, the power dissipated is reduced to approximately one third and the flyback time is halfed.

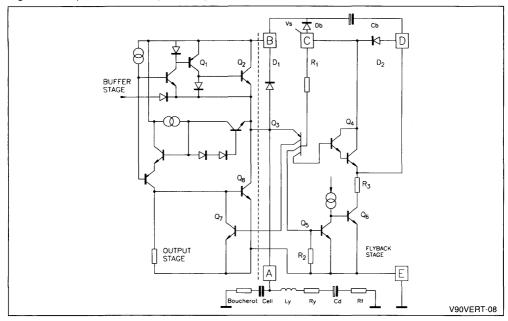

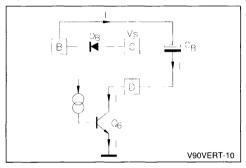

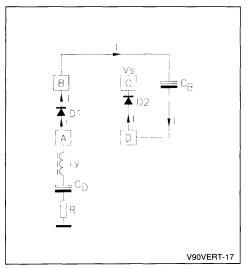

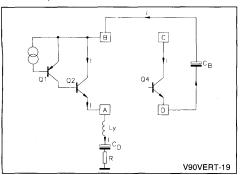

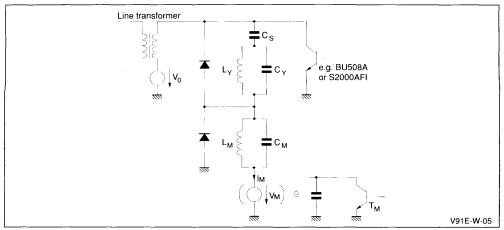

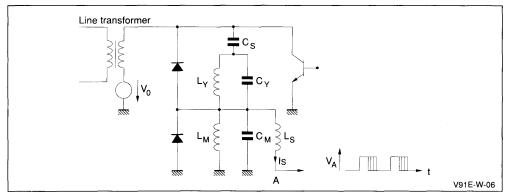

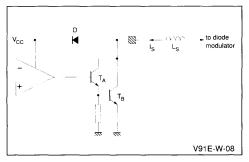

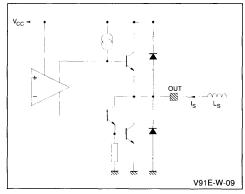

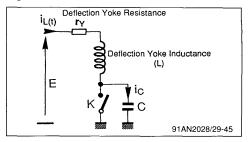

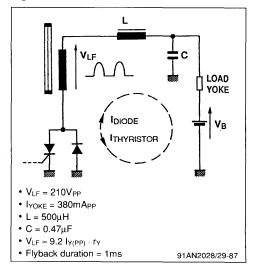

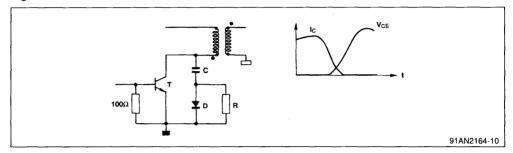

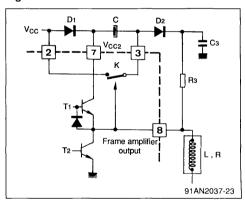

The flyback circuit is shown in Figure 8 together with the power stage.

Figure 8: Output Power and Flyback stages.

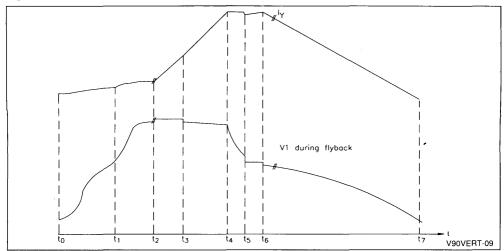

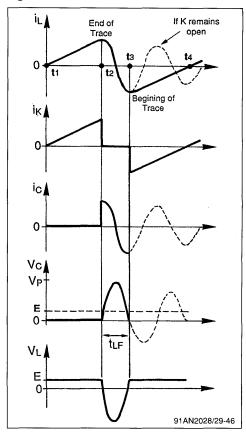

Figure 9 shows the circuit behaviour, to show operation clearly. The graphs are not drawn to scale. Certain approximations are made in the analysis in

order to eliminate electrical parameters that do not significantly influence circuit operations.

Figure 9: Current in the Yoke and Voltage Drop on the Yoke during Vertical Deflection.

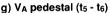

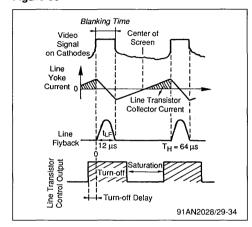

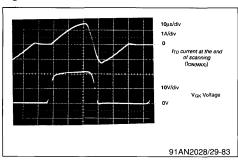

#### a) Scan period (t<sub>6</sub> - t<sub>7</sub>): Figure 10

During scanning  $Q_3$ ,  $Q_4$  and  $Q_5$  are off and this causes  $Q_6$  to saturate.

A current from the voltage supply to ground flows through  $D_B$ ,  $C_B$  and  $Q_6$  charging the  $C_B$  capacitor up to :

$$VC_B = V_S - VD_B - VQ_{6SAT}$$

(4)

At the end of this period the scan current has reached its peak value (IP) and it is flowing from the yoke to the device. At the same time  $V_A$  has reached its minimum value.

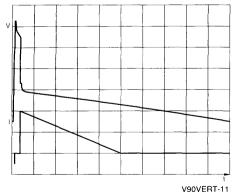

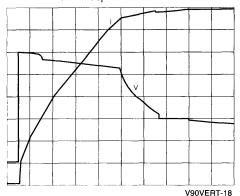

In Figures 11 and 12 are depicted the voltage drop on the yoke and the currents flowing through D<sub>B</sub> and the yoke.

Figure 10 : Circuit Involved during Scan Period.

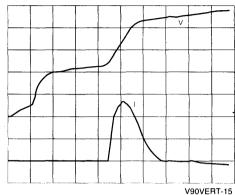

Figure 11: Voltage Drop on the Yoke and Current Flowing through D<sub>B</sub>.

V = 10V/div.

I = 0.5A/div.

t = 2ms/div.

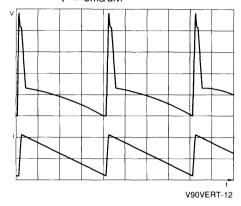

Figure 12: Voltage Drop on the Yoke and Current Flowing through the Yoke.

V = 10V/div.

I = 1A/div

t = 5ms/div.

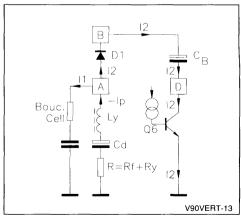

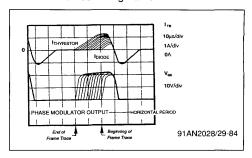

## b) Flyback starting (t<sub>0</sub> - t<sub>1</sub>): Figure 13

$Q_{\text{B}},$  that was conducting the -  $\mbox{\rm IP}$  current, is turned off by the buffer stage.

The yoke, charged to I<sub>P</sub>, now forces this current to flow partially through the Boucherot cell (I<sub>1</sub>) and partially through D<sub>1</sub>, C<sub>B</sub> and Q<sub>6</sub> (I<sub>2</sub>).

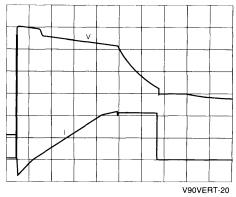

In Figures 14, 15 and 16 are represented the currents flowing through the yoke, the Boucherot cell and  $D_1$ .

Figure 13 : Circuit Involved during Flyback Starting.

#### c) Flyback starting (t<sub>1</sub> - t<sub>2</sub>)

When the voltage drop at pin A rises over Vs,  $Q_3$  turns on and this causes  $Q_4$  and  $Q_5$  to saturate. Consequently  $Q_6$  turns off.

During this period the voltage at pin D is forced to:

$$V_D = V_S - VQ_{4SAT}$$

(5)

Therefore the voltage at pin B becomes:

$$V_B = V_{CB} + V_D \tag{6}$$

The yoke current flows in the Boucherot cell added to another current peak flowing from  $V_S$  via  $Q_4$  and  $C_B$  (Figures 14 and 15).

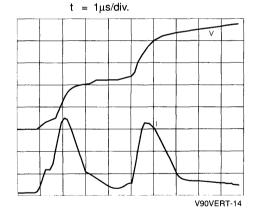

Figure 14: Voltage Drop on the Yoke and Cur-

Cell. V = 10V/div.

I = 1A/div

rent Flowing through the Boucherot

$\begin{tabular}{ll} \textbf{Figure 15}: Voltage Drop on the Yoke and Current Flowing through $D_1$. \end{tabular}$

V = 10V/div.

I = 1A/div

$t = 1\mu s/div.$

Vadventila

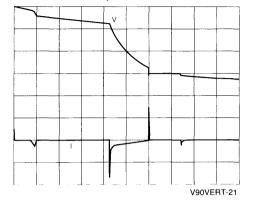

Figure 16: Voltage Drop on the Yoke and Current Flowing through the Yoke.

V = 10V/div.

I = 100 mA/div.

$t = 1\mu s/div.$

#### d) Negative current rise (t2 - t3): Figure 17

Figure 17 : Circuit Involved during the Negative Current Rise.

During this period, the voltage applied at pin A is:

It is possible to calculate the current solving the following equation:

$$V_A = L_Y \frac{di}{dt} + \frac{1}{C_D} \int i \cdot dt + R \cdot i$$

(8)

where  $R = R_F + R_Y$

Because the voltage at pin A is approximatively constant (error less than 2%) we can simplify the (8) in the following equation:

$$\frac{d^2i}{dt^2} + \frac{R}{L_Y}\frac{di}{dt} + \frac{1}{L_YC_D}i = 0 \qquad (9)$$

It results in:

$$i(t) = \frac{I_{P}}{e^{2\beta \Delta T_{1}} - 1} e^{(-\alpha + \beta)t} - \frac{I_{P}}{1 - e^{-2\beta \Delta T_{1}}} e^{(-\alpha - \beta)t}$$

(10)

where:

Because of  $\Delta T_1$  is two orders of magnitude lower than the scan time, we can apply an exponential sum to obtain the following equation :

$$i(t) = I_{P} \frac{\alpha \cosh(2\beta \Delta T_{1}) + \beta \sinh(2\beta \Delta T_{1}) - \alpha}{\cosh(2\beta \Delta T_{1}) - 1} t - I_{P}$$

(11)

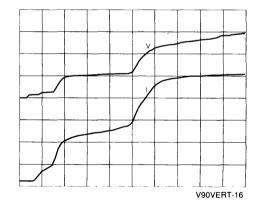

**Figure 18 :** Voltage Drop on the Yoke and Current Flowing through the Yoke.

V = 10V/div.

I = 250 mA/div.

$t = 100 \mu s/div$ .

Simplifying:

$$i(t) = I_P \left(\alpha + \frac{1}{\Delta T_1}\right) t - I_P$$

(12)

The slope of the current is therefore:

$$\frac{di}{dt} = \left(\frac{R}{2 L_Y} + \frac{1}{\Delta T_1}\right) I_P \quad (A/s) \tag{13}$$

The current flows from the yoke to  $V_S$  through  $D_1$ ,  $C_B$  and  $D_2$ , and it is depicted in Figure 18.

## e) Positive current rise (t<sub>3</sub> - t<sub>4</sub>): Figure 19

Figure 19 : Circuit Involved during the Positive Current Rise.

When the current becomes zero,  $D_1$  turns off and  $Q_2$  saturates; so the pin A voltage becames:

$$V_A = V_B - V_{Q2SAT}$$

$$V_A = 2 \cdot V_S - V_{DB} - V_{Q6SAT}$$

$$- V_{Q4SAT} - V_{Q2SAT}$$

(14)

The current flows from  $+V_S$  into the yoke through  $Q_4$ ,  $C_B$  and  $Q_2$  and rises from zero to  $I_P$  as it can be seen in Figure 18.

By using the previous procedure explained in section d), we can obtain the slope of the current:

$$\frac{di}{dt} = \left(\frac{R}{2L_Y} + \frac{1}{\Delta T_2}\right) I_P \quad (A/s) \tag{15}$$

where  $\Delta T_2 = t_4 - t_3$

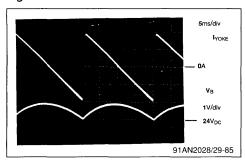

#### f) Flyback decay (t<sub>4</sub> - t<sub>5</sub>)

When the yoke current reaches its maximum peak,  $Q_2$  desaturates and conducts the maximum peak current flowing from  $V_S$  via  $Q_4$  and  $C_B$  into  $L_Y$ ; the current flowing through  $C_B$  is depicted in Figure 20.

Figure 20: Voltage Drop on the Yoke and Current Flowing through C<sub>B</sub>.

V = 10V/div

I = 0.5A/div.

$t = 100 \mu s/div.$

An eventual antiringing parallel resistor modify the linear decay slope in an exponential one, as it can be seen in Figure 22.

This continues until the buffer stage turns  $Q_2$  on. The effect of the Boucherot cell during this periode is negligible (see Figure 21).

Figure 21: Voltage Drop on the Yoke and Current Flowing through the Boucherot Cell.

V = 10V/div.

I = 100 mA/div.

$t = 100 \mu s/div.$

When  $V_A$  reaches the value  $V_S$  of the supply voltage, the flyback generator stops its function.  $Q_3$  is turned off and turns off  $Q_4$  that open the

Figure 22 : Effect of the Resistor in Parallel connected to the yoke.

V = 10V/div.

connection between pin D and Vs.

Therefore  $V_B$  drops to  $V_S$  -  $V_{DB}$  while :

$V_A = V_S - V_{DB} - V_{Q2CE on}$

At this point the normal scan takes place.

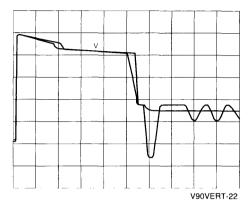

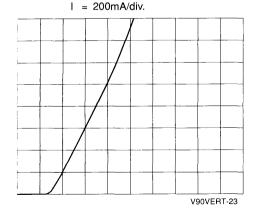

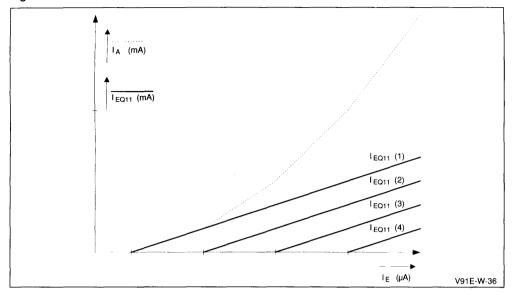

#### 8. CURRENT-VOLTAGE CHARACTERISTICS OF THE RECIRCULATING DIODES.

The following Figures 23 and 24 reproduce the I - V characteristics of the integrated recirculating di-

Figure 23: I - V Characteristic of the Diode D<sub>1</sub>.

V = 500 mV/div.

These characteristics are useful in order to calculate the maximum voltage reached at pin A with the

odes  $D_1$  and  $D_2$  (see Figure 8).

Figure 24: I - V Characteristic of the Diode D2.

V = 500 mV/div.

I = 200 mA/div

formula (7) explained in chapter 7.

#### 9. CALCULATION PROCEDURE OF THE FLY-BACK DURATION

The flyback duration can be calculated using the following procedure (referring to Figure 25).

Figure 25 : Circuit Involved in the Calculation of Flyback Duration.

During the flyback period the voltage applied at pin A is about 2 Vs, as previously explained in chapter 7. The voltage drop across  $C_D$  is approximatively a constant voltage little less than  $V_S \ / 2.$  The voltage on the feedback resistor  $R_F$  is :

$$VR_F(t) = R_F I_Y(t)$$

so in the period which we are considering it is negligible respect to  $V_{\text{S}}/2$ .

The effect of the Boucherot cell during this period is not sensible as it can be seen in Figure 21; while  $R_D$  acts principally during the flyback decay time (Figure 9:  $t_4$ - $t_5$ ) reducing its slope and the resulting oscillations but doesn't influence the total flyback time as shown in Figure 22. So their influences are also negligible.

Now the effective voltage drop across the yoke can be approximated to :

$$2 \cdot V_S - \frac{V_S}{2} = \frac{3}{2} V_S$$

Figure 25 can be simplified as shown in Figure 26.

Figure 26 : Simplified Circuit for the Calculation of Flyback Duration.

The voltage charges the coil with a linear current that can be calculated in the following way:

$$i(t) = \frac{1}{L_Y} \int V \cdot dt = \frac{1}{L_Y} \int \frac{3}{2} V_S \cdot dt$$

(16)

$i(t) = \frac{1}{L_Y} \frac{3}{2} V_S \cdot t + K$

K is calculated imposing that the current at the beginning of the flyback is - Ip.

$$i(0) = -I_P$$

$K = -I_P$

$i(t) = \frac{3}{2} \frac{V_S}{L_Y} t - I_P$  (17)

At the end of the flyback period the current will be + I<sub>P</sub>, so we can write:

$$I_P = \frac{3}{2} \frac{V_S}{L_Y} t_F - I_P$$

The duration of the flyback period is then:

$$t_F = \frac{4}{3} \frac{I_P L_Y}{V_S} = \frac{2}{3} \frac{I_Y L_Y}{V_S}$$

(18)

#### 10. APPLICATION INFORMATION

The vertical deflection stages producted by SGS-THOMSON are able to cover the complete range of applications that the market need for color television and high/very high resolution monitors.

Television and monitor applications are not very different but in monitor field, in addition to the linearity and interlacing problems, we have to pay attention to the flyback time that must be very short for very high resolution models.

In television applications the most important requirement is to choose the lowest supply voltage possible in order to minimize the power dissipation in the integrated circuit, reducing the dimension of the heatsink, and the power dissipation from the voltage supplier.

These results can be reached very easily with SGS-THOMSON deflection stages because of the high efficiency of the flyback generator circuit used. In high resolution monitors one of the main problems is to reach the very short flyback time requested; the flyback generator, together with the high current and power dissipation capabilities, solve all the problems in a simple way.

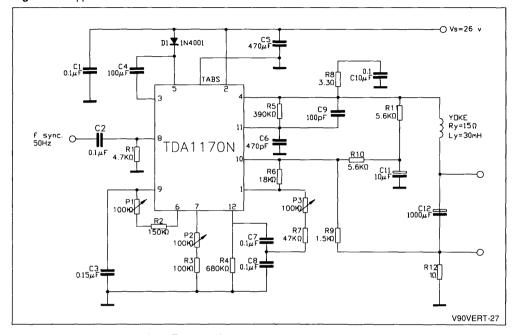

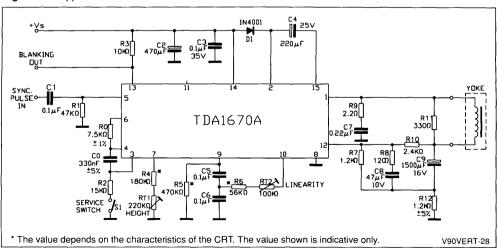

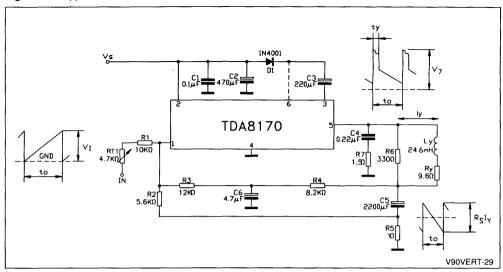

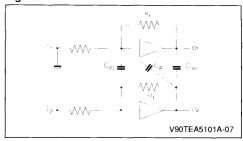

In Figures 27, 28 and 29 are depicted three typical application circuits for the different kinds of integrated circuits available.

Figure 27: Application Circuit for TDA1170.

Figure 28: Application Circuit for TDA1670A.

Figure 29: Application Circuit for TDA8170.

In the following chapters we shall do the calculation for television and monitor in order to choose the right voltage supply and external network for the yoke used and the current requirements.

## 11. SUPPLY VOLTAGE CALCULATION

For television applications we shall calculate the

minimum supply voltage necessary to have vertical scanning knowing the yoke characteristics and the current required for the given application.

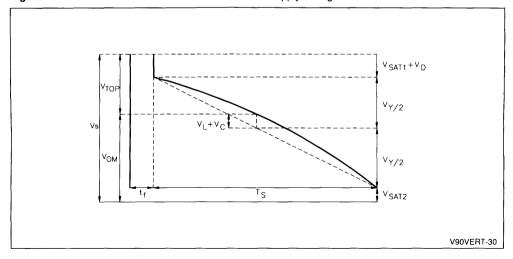

Figure 30 shows the terms used in this section, while the circuit part involved in the following calculations is depicted in Figure 31.

Figure 30: Parameters Used in the Calculation of the Supply Voltage.

Figure 31 : Circuit Involved in the Calculation of the Supply Voltage.

Vs = supply voltage.

Vy = nominal voltage required to produce the scanning current including the feedback resistance and the 20% increasing for temperature variations in the yoke current;

$$V_Y = (1.2 R_Y + R_F) I_Y$$

(19)

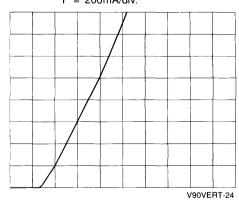

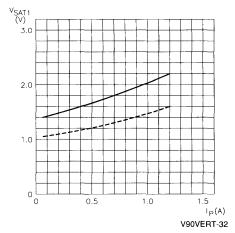

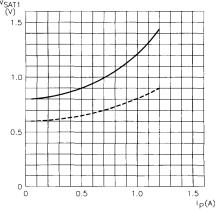

V<sub>SAT1</sub> = nominal output saturation voltage due to the upper power transistor Q<sub>1</sub> (see Figure 32);

V<sub>SAT2</sub> = nominal output saturation voltage due to the lower power transistor Q<sub>2</sub> (see Figure 33);

V<sub>OM</sub> = nominal quiescent voltage (midpoint) on the output power transistors;

V<sub>C</sub> = voltage peak due to the charge of C<sub>D</sub> capacitor;

$$V_C = \frac{I_Y \cdot t_S}{8 \cdot C_D} \tag{20}$$

V<sub>L</sub> = voltage drop due to the yoke inductance L<sub>Y</sub>;

$$V_L = \frac{L_Y - I_Y}{t_S} \tag{21}$$

**Figure 32 :** Saturation characteristic of the Upper Power Transistor.

**Figure 33 :** Saturation characteristic of the Lower Power Transistor.

V90VERT-33

V<sub>D</sub> = nominal voltage drop on D<sub>B</sub> diode in series with the supply:

T = vertical scan period;

t<sub>F</sub> = flyback time;

$$t_F = \frac{2}{3} \frac{I_Y \cdot L_Y}{V_S}$$

ts = scanning time;

$$t_S = T - t_F$$

ly = peak to peak deflection current;

Ry = nominal yoke resistance;

Ly = nominal yoke inductance;

R<sub>F</sub> = feedback resistor.

Referring to Figure 30 it is easy to see that the minimum supply voltage is given by:

$$V_S = V_{OM} + V_{TOP}$$

(22)

where:

$$V_{OM} = \frac{V_Y}{2} + V_{SAT2} + V_C + V_L \qquad (23)$$

and:

$$V_{TOP} = \frac{V_Y}{2} + V_D + V_{SAT1} - V_L - V_C$$

(24)

So we obtain:

$$V_S = V_Y + V_D + V_{SAT1} + V_{SAT2}$$

(25)

The (25) gives the minimum voltage supply if we do not consider the tolerances of the integrated circuit and of the external components, but the calculation, even if it was not realistic, it was useful in order to understand the procedure.

Now we shall do the same thing considering all the possible spreads; we can in this way obtain the real minimum supply voltage.

We shall follow the statistical composition of spreads because it is never possible that all of them are present at the same time with the same sign.

We must consider the following spreads:

ΔVγ due to the variation of yoke and feedback resistance and yoke current, supposing a 10% of regulation range in scanning current and a precision of 7% for resistors;

$$\Delta V_Y = (\ 1.2 \ R_Y + \ R_F \ ) \ 1.07 \ (\ 1.1 \ I_Y \ ) - \ V_Y \ (26)$$

•  $\Delta V_C$  due to the tolerance of  $C_D$  and yoke current regulation;

$$\Delta V_C = \frac{1.1 \text{ ly ts}}{8 \text{ C}_{D(MIN)}} - V_C$$

(27)

ΔV<sub>L</sub> due to the tolerance of L<sub>Y</sub> (± 10%) and yoke current regulation;

$$\Delta V_L = \frac{1.1 \text{ ly } 1.1 \text{ Ly}}{\text{ts}} - V_L$$

(28)

For each parameter, it is necessary to calculate the factor  $\rho$ , expressing the percentual influence of every parameter variation on the nominal supply voltage, with the following formulas:

for Vom:

$$\rho = \frac{\Delta V}{V_{OM}}$$

for V<sub>TOP</sub>:

$$\rho = \frac{\Delta V}{V_{TOP}}$$

We have then to calculate the square mean root of the spreads expressed as:

$$\sqrt{\sum_{\rho^2}}$$

So if we call:

$$V_{OM1} = V_{OM} \left( 1 + \sqrt{\sum \rho^2} \right)$$

and:

$$V_{TOP1} = V_{TOP} \left( 1 + \sqrt{\sum \rho^2} \right)$$

We can write:

$$V_S = V_{OM1} + V_{TOP1}$$

(29)

An example of calculation will better explain the procedure. We shall consider a 26", 110°, neck 29.1mm tube whose characteristics are:  $I_Y = 1.2 \text{ App}$ ;

$R_{Y} = 9.6\Omega \pm 7\%$ :  $L_Y = 24.6 \text{mH} \pm 10\%$ .

We shall use a coupling capacitance CD of 1500µF with + 50% and - 10% tolerance and a feedback resistance R<sub>F</sub> of  $1.2\Omega$ .

#### a) Nominal minimum supply voltage:

We obtain:  $V_S = 18.2V$

#### b) Statistical minimum supply voltage:

$V_S = V_{OM1} + V_{TOP1} = 21.2 V$

This is a real value for the minimum supply voltage needed by the above mentioned application.

In this case we obtain a flyback duration of about:

$$t_F = \frac{2}{3} \frac{I_Y \cdot L_Y}{V_S} \approx 900 \,\mu s$$

#### 12. CALCULATION OF MIDPOINT AND GAIN

For the calculation of the output midpoint voltage, it is necessary to consider the different feedback network for the applications of the various integrated circuits.

We shall first consider the TDA1170 family, the TDA1175, TDA2170, TDA2270, TDA8170, TDA8172, TDA8173, TDA8175 and TDA8176.

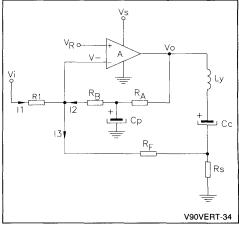

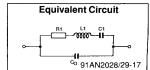

The equivalent circuit of the output stage is represented in Figure 34.

Figure 34: Circuit Utilized for the Calculation of midpoint and gain for TDA1170. TDA1175, TDA8176, TDA2170, TDA2270, TDA8170, TDA8172, TDA8173 and TDA8175.

For DC considerations we shall consider the two capacitors as open circuits. Because of the very high gain of the amplifier we can suppose :

$$V^- = V_R$$

.

We can so write:

$$I_1 + I_2 = I_3$$

(30)

where:

$$I_1 \, = \, \frac{V_i \, - \, V_R}{R_1} \qquad \quad I_2 \, = \, \frac{V_O \, - \, V_R}{R_A \, + \, R_B} \qquad \quad I_3 \, = \, \frac{V_R}{R_F \, + \, R_S}$$

Substituting into the (30) we obtain:

$$V_O = V_R \left( 1 + \frac{R_A + R_B}{R_F + R_S} \right) - (V_i - V_R) \frac{R_A + R_B}{R_1}$$

(31)

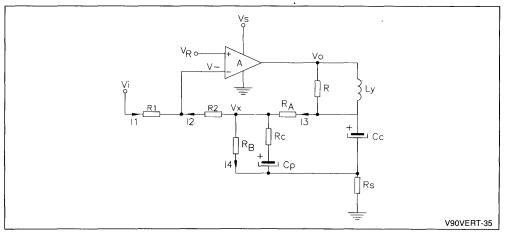

Let's consider now TDA1670A, TDA1675, TDA1770A, TDA1771, TDA1872A and TDA8174.

The equivalent output circuit is depicted in Figure 35.

Figure 35 :Circuit Utilized for the Calculation of Midpoint and Gain for TDA1670A, TDA1675,TDA1770A, TDA1771, TDA1872A and TDA8174.

We can write:

$$l_1 = l_2$$

(32)

$$l_2 + l_3 = l_4$$

(33)

where:

$$I_1 \; = \; \frac{V_i \; - \; V_R}{R_1} \qquad \quad I_2 \; = \; \frac{V_R \; - \; V_X}{R_2} \qquad \quad I_3 \; = \; \frac{V_O \; - \; V_X}{R_A} \qquad \quad I_4 \; = \; \frac{V_X}{R_B \; + \; R_S}$$

with the (32) and (33) we can calculate the DC output voltage. It results in :

$$V_{O} = V_{R} \left( 1 + \frac{R_{A} + R_{2}}{R_{1}} + \frac{R_{A} (R_{1} + R_{2})}{R_{1} (R_{B} + R_{S})} \right) - V_{i} \left( \frac{R_{A} + R_{2}}{R_{1}} + \frac{R_{A} \cdot R_{2}}{R_{1} (R_{B} + R_{S})} \right)$$

(34)

Referring to Figures 34 and 35, it is possible to calculate the transconductance gain of the power amplifier. For this calculation we shall do the follow-

ing approximations:

- the capacitors are practically short circuits;

- the gain A of the amplifier is very high  $(A \rightarrow \infty)$ .

For the circuit represented in Figure 34 we obtain :

$$I_Y = \frac{R_F}{R_1 \cdot R_S} V_i \qquad (36)$$

Using the (31), (34), (35) and (36) it is possible to calculate the external feedback network for every

while for the application in Figure 35 the yoke current results in :

$$I_{Y} = \frac{R_{2} + R_{A} / / R_{B} / / R_{C}}{R_{1} \cdot R_{S}} V_{i}$$

(37)

different yoke known the scanning current and the midpoint output voltage.

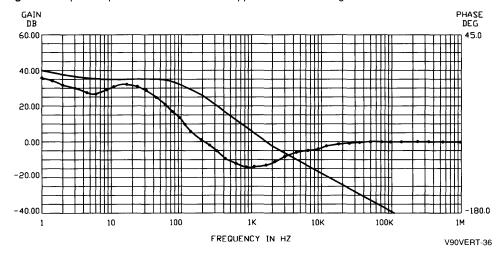

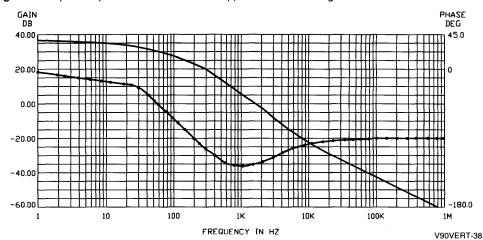

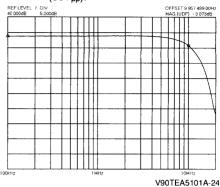

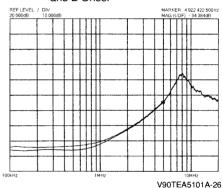

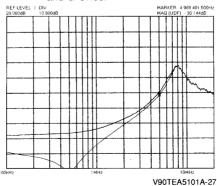

Figure 36: Open Loop Gain and Phase for the Application Circuit in Figure 27.

Figure 37: Open Loop Gain and Phase for the Application Circuit in Figure 28.

We can now consider the open loop gain of the whole system amplifier plus external feedback net-

work. This calculation is useful in order to verify that no oscillations can occur at any frequency.

Figure 38: Open Loop Gain and Phase for the Application Circuit in Figure 29.

We shall consider some typical applications; the results are reported in Figures 36, 37 and 38. It is easy to verify that in all cases, when the gain reaches 0dB, the phase margin is about 60°, so the stability of the system is assured.

#### 13. MONITOR APPLICATIONS

In monitor applications the flyback time needed could be very smaller than the one we get using the minimum supply voltage calculation.

It is possible to reduce the flyback time in two different ways:

- a) increasing the supply voltage, when the nominal value calculated is lower than the integrated circuit limit;

- b) choosing a yoke with lower values in inductance and resistance and by supplying the circuit with the voltage needed for getting the right flyback time.

In both cases we have to calculate the biasing and the gain conditions using the nominal voltage and then we fix the supply voltage for the flyback time requested with the formula (18):

$$V_S = \frac{2}{3} \frac{I_Y \cdot L_Y}{t_F}$$

The calculation procedure for monitors is so the

same as the one we have explained in the previous chapters for television applications.

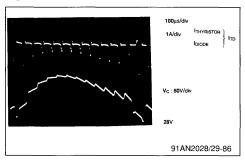

#### 14. POWER DISSIPATION

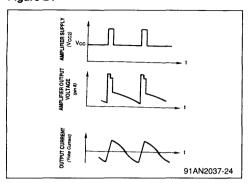

We shall now examine the power dissipation of the integrated circuit and the dimensions of the heatsink.

To calculate the power dissipated we must consider the maximum scanning current required to drive the yoke  $I_{Y(MAX)}$  and the maximum supply voltage  $V_{S(MAX)}$  because we have to dimension the heatsink for the worst case.

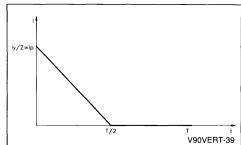

The current absorbed from the power supply is depicted in Figure 39.

Figure 39 : Current Absorbed from the Power Supply during Scanning.

The equation of the curve is:

$$i(t) = \frac{l_Y}{2} - \frac{l_Y}{T} t \qquad \text{for } 0 < t \le T/2$$

$$i(t) = 0 \qquad \text{for } T/2 < t \le T$$

(37)

To the previous one we have to sum the DC current necessary to supply the other parts of the circuit (quiescent current). The power absorbed by the deflection circuit is then:

$$\begin{aligned} P_{A} &= \int_{0}^{T/2} V_{S(MAX)} \cdot i(t) \cdot dt + V_{S(MAX)} \cdot I_{DC} \\ &= V_{S(MAX)} \int_{0}^{T/2} \left( \frac{I_{Y(MAX)}}{2} - \frac{I_{Y(MAX)}}{T} t \right) dt + V_{S(MAX)} \cdot I_{DC} \end{aligned}$$

The solution is:

$$P_{A} = V_{S(MAX)} \left( \frac{I_{Y(MAX)}}{8} + I_{DC} \right)$$

(38)

The power dissipated outside the integrated circuit is formed by the three following fundamental components: the scanning power dissipated in the yoke for which the minimum resistance of yoke RY(MIN) and the maximum scanning current IY(MAX)

must be considered, the power dissipated in the feedback resistance R<sub>F</sub> and that one dissipated in the diode for recovery of flyback.

The power dissipated outside the integrated circuit is then:

$$\begin{array}{lll} P_{Y} & = \int_{0}^{T} \left( \, R_{Y(MIN)} + \, R_{f} \, \right) \, i^{2} \left( \, t \, \right) \cdot \, dt + \int_{0}^{T/2} \, V_{D} \, \, i \left( \, t \, \right) \cdot \, dt \\ \\ & = \, \left( \, R_{Y(MIN)} + \, R_{f} \, \right) \, \int_{0}^{T} \left( \, \frac{I_{Y(MAX)}}{2} - \, \frac{I_{Y(MAX)}}{T} \, t \, \right)^{2} \, dt \, + \, V_{D} \, \int_{0}^{T/2} \left( \, \frac{I_{Y(MAX)}}{2} - \, \frac{I_{Y(MAX)}}{T} \, t \, \right) dt \end{array}$$

The solution is:

$$P_{Y} = \frac{I^{2}_{Y(MAX)} (R_{Y(MIN)} + R_{f})}{12} + \frac{I_{Y(MAX)} \cdot V_{D}}{8}$$

(39)

The power dissipated inside the integrated circuit is:

$$P_D = P_A - P_Y \qquad (40)$$

The thermal resistance of the heatsink to be used with the integrated circuit depends upon the maximum junction temperature  $T_{J(MAX)}$ , the maximum ambient temperature  $T_{AMB}$  and the thermal resis-

tance between junction and tab  $R_{TH\ (J-TAB)}$  that is different for the various packages used. The thermal resistance of the heatsink is expressed by the following formula :

$$R_{TH\ J-AMB}\ =\ \frac{T_{J(MAX)}-\ T_{AMB(MAX)}}{P_{D(MAX)}}-\ R_{TH\ J-TAB} \eqno(41)$$

As an example we can calculate the dissipated power and the thermal resistance of the heatsink for the 26", 110°, neck 29.1mm tube for which we calculated the minimum supply voltage in chapter 11.

We shall consider the integrated circuit TDA1670A and we can suppose a maximum supply voltage of 25V.

The power absorbed from the supply is:

$$P_A = 25 \left( \frac{1.2}{8} + 0.04 \right) = 4.75 W$$

The power dissipated outside the integrated circuit is:

$$P_Y = \frac{1.2^2 (9.6 \cdot 0.93 + 1.2)}{12} + \frac{1.21}{8} = 1.37 \, W$$

therefore the power dissipated by the integrated circuit is:

$$P_D = 4.75 - 1.37 = 3.38 W$$

The thermal resistance of the heatsink, considering the R<sub>TH</sub> <sub>J-TAB</sub> for the multiwatt package of 3°C/W, a maximum junction temperature of 120°C and a maximum ambient temperature of 60°C is:

$$R_{TH H-AMB} = \frac{120 - 60}{3.38} - 3 = 15^{\circ}C/W$$

For the same application with TDA1170S we have a thermal resistance for the heatsink of about 8°C/W.

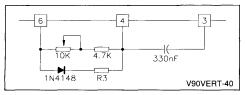

#### 15. BLANKING PULSE DURATION ADJUST-MENT

For the devices that have the blanking generator it is possible to adjust the blanking pulse duration. We shall consider as an example the TDA1670A; the circuit arrangement is depicted in Figure 40.

Figure 40: Circuit Arrangement for Blanking Pulse Duration Adjustment.

By adjusting  $R_3$  the blanking pulse duration will be adapted to the flyback time used and the picture tube protection will be ready to work properly.

When necessary, it is possible to use a trimmer system to adjust it very carefully.

#### 16. LINEARITY ADJUSTMENT

The complete vertical stages have the possibility to control the linearity of the vertical deflection ramp. There are two different methods to obtain the above mentioned performance.

# a) For the first method we shall refer to Figure 41.

Figure 41: Circuitry for Ramp Linearity Regulation.

The linearity regulation is obtained by means of  $R_{A}$ ,  $R_{B}$  and  $R_{T2}$ .

In order to choose the right values of this components we suggest to follow the following procedure:

- 1 Set the amplitude regulation potentiometer  $R_{T1}$  for the nominal raster size;

- 2 Disconnect the R<sub>A</sub> resistance;

- 3 Adjust the linearity control potentiometer  $R_{T2}$  in order to obtain the top and the bottom of the raster with the same amplitude;

- 4 In this condiction the center of the raster must be narrower then the top and the bottom. If with  $R_{\text{A}}$

disconnected the center is larger than the top and the bottom it is necessary to act on the feedback network. Referring to Figures 27, 28 and 29 it is necessary to increase the capacitors C<sub>11</sub>, C<sub>8</sub> or C<sub>6</sub>; 5 - After increasing the capacitors it is necessary to repeat the linearity adjustment (R<sub>12</sub> potentiometer) in order to get the top and the bottom with the same amplitude again:

- 6 Connect the R<sub>A</sub> resistor and repeat the linearity adjustment (point 3 regulation);

- 7 Check the top and the bottom amplitude comparing it with the center. If the center amplitude is still narrower it is necessary to reduce R<sub>A</sub>. If the center amplitude becomes larger it is necessary to increase R<sub>A</sub>.

Note: Every time the linearity conditions are changed (for adjusting or setting) before checking the linearity status, the point 3 adjustment must be repeated.

# b) For the second method we shall refer to Figure 28.

In this case the linearity regulation is obtained acting directly on the feedback network, that is substituting the  $R_{\rm B}$  resistance with a potentiometer. This solution is cheaper than the first one, because it is possible to save the resistors  $R_{\rm A},\ R_{\rm B}$  (see Figure 41), the potentiometer  $R_{\rm T2}$  and to use only a capacitor instead of the series  $C_1$  and  $C_2$ .

On the other hand a disadvantage is due to the fact that the resistance  $R_8$  influences not only the linearity of the ramp but also the gain of the amplifier, as it can be seen in the equation (36). So to perform a linearity adjustment it is necessary to act at the same time on the potentiometer in the feedback loop and on the potentiometer  $R_{T1}$  (see Figure 41) in order to correct the vertical amplitude variations. On the contrary, in the method a) the linearity control network doesn't influence any other parameters. this is the reason why the a) method is generally adopted by all television set producers.

#### 17. FACILITIES AND IMPROVEMENTS

In this section we shall briefly examine some facilities which may be useful to improve operations of the television set.

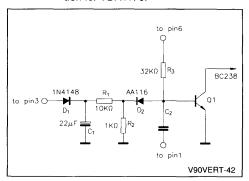

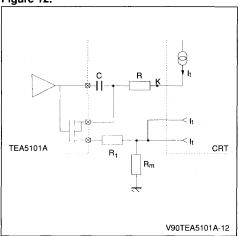

### a) Blanking generator and CRT protection for TDA1170 family.

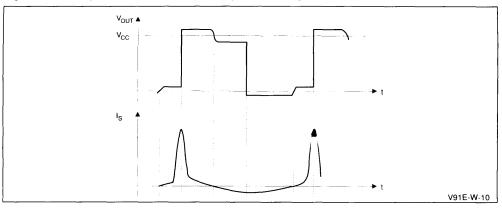

At pin 3 a pulse is available which has the same duration and phase as the flyback and amplitude

equal to the supply voltage.

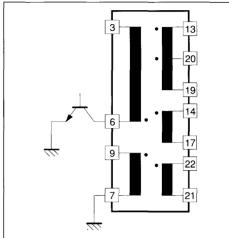

If the retrace duration is not sufficient for carrying out correct vertical blanking, for instance in the presence of text and teletext signals the circuit of Figure 42 can be used.

The true blanking generator is formed by  $Q_1, R_3$  and  $C_2$  and the blanking duration is dependent upon the values of  $R_3$  and  $C_2$ . The other components are used for picture tube protection in the event of loss of vertical deflection current. If for any reason there is no flyback, the transistor  $Q_1$  is permanently inhibited and provides continuous switch off which eliminates the white line at the center of the screen. Thermal stability and stability with the supply voltage is good in relation to the simplicity of the application.

Figure 42: Blanking Generator and CRT Protection for TDA1170.

b) Vertical deflection current compensation to maintain picture size with beam current variations.

Changes in the supply voltage or the brightness and contrast controls will bring out changes of the beam current, thus causing EHT and picture size variations.

The rate of change of the picture size is mainly dependent upon the EHT internal resistance.

In order to avoid variations of the vertical picture size it is necessary to track the scanning current to the beam current. Because the tracking ratio:

$$\frac{\Delta \text{ IYOKE}}{\Delta \text{ IBEAM}} \cdot 100$$

(42)

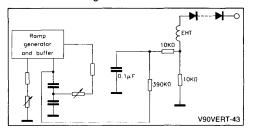

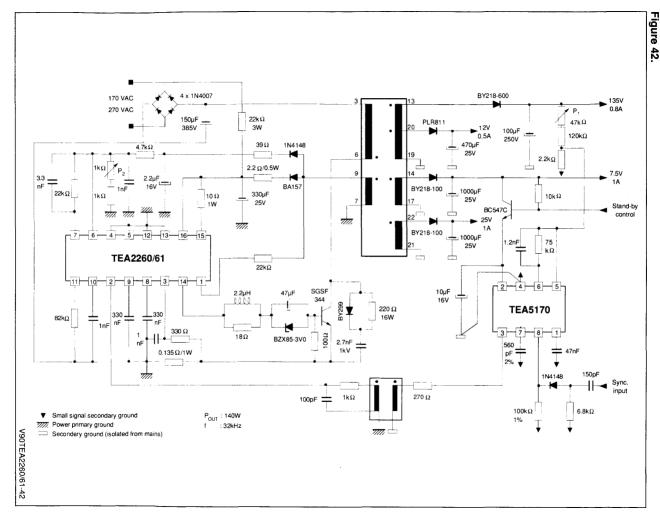

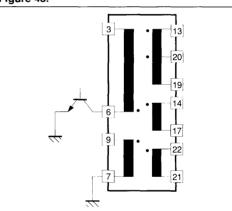

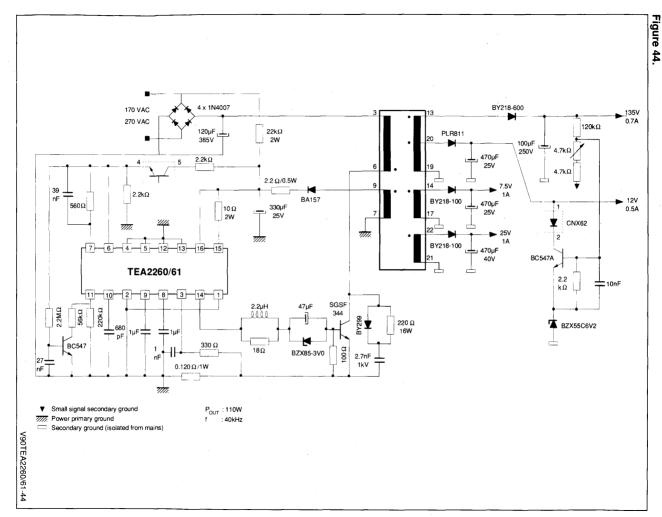

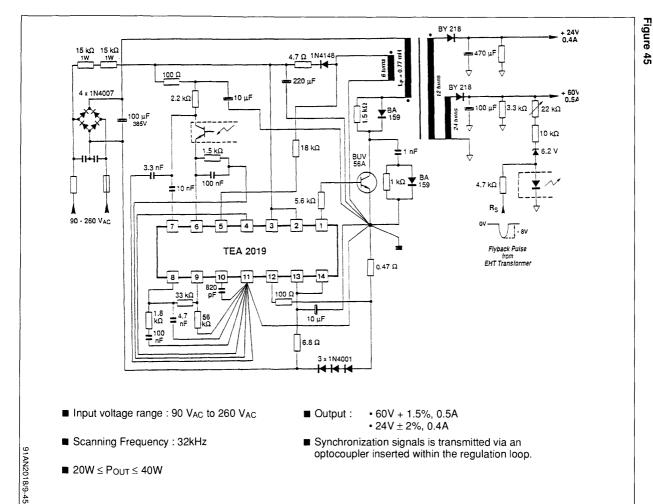

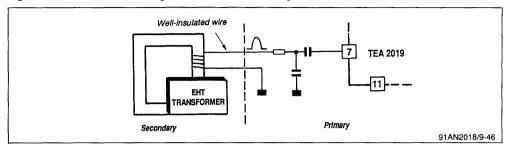

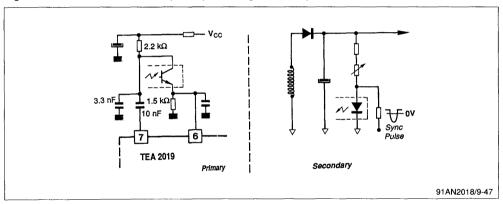

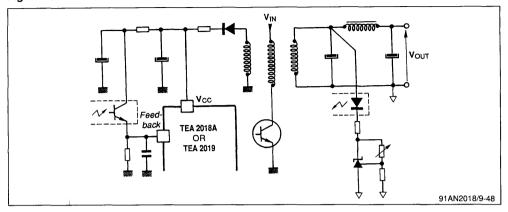

varies from one chassis design to another, three suggested tracking circuits are shown in Figures 43, 44 and 45.

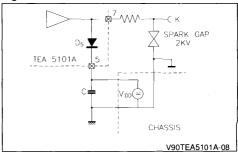

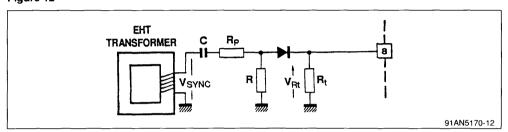

The circuit in Figure 43 adopts the straight forward technique of linking the vertical scanning current directly to the beam current .lts drawback lies in the fact that a long wire connection is required between the EHT transformer and the vertical circuit, and the layout of this connection could be critical for flashover.

Figure 43: Circuit for Vertical Scanning Current Variation according with the Beam Current.

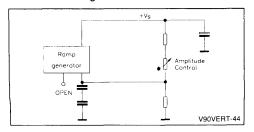

The circuit of Figure 44, which links the vertical scanning current directly to the supply voltage, is the simplest one. Its drawback could be incorrect tracking ratio and ripple on the supply voltage. To overcome the drawbacks of the preceding circuit it is usefull to filter out the supply voltage ripple and adjust the tracking ratio by transferring the supply voltage to a lower level by means of a Zener diode as shown in Figure 45. Tracking ratio is adjusted by choosing a suitable Zener voltage value.

Figure 44: Circuit for Vertical Scanning Current Variation according with the Supply Voltage.

Figure 45 : Circuit for Vertical Scanning Current Variation according with the Supply Voltage.

# 18. GENERAL APPLICATION AND LAYOUT HINTS

In order to avoid possible oscillations induced by the layout it is very important to do a good choice of the Boucherot cell position and ground placing. The Boucherot cell must be placed the most possible closed to the vertical deflection output of the integrated circuit, while the ground of the sensing resistor in series connected with the yoke must be the same as the one of the integrated circuit and different from the one of other power stages. Particular care must be taken in the layout design in order to protect the integrated circuit against flashover of the CRT. For instance the ground of the filter capacitor connected to the power supply must be near the integrated circuit ground.

#### 19. REFERENCES

- Television Deflection Systems A. Boekhorst,

J. Stolk Philips Technical library.

- TV Vertical Deflection System TDA1170S -SGS-THOMSON Application Notes.

- TDA1670A Technical Note SGS-THOMSON Technical Note.

- TV and Monitor Vertical Deflection using TDA1670A - O. Cossutta, F. Gatti SGS-THOMSON Application Notes.

- TDA1670A Flyback Stage Behaviour A. Messi, G. Nardini - SGS-THOMSON Application Notes.

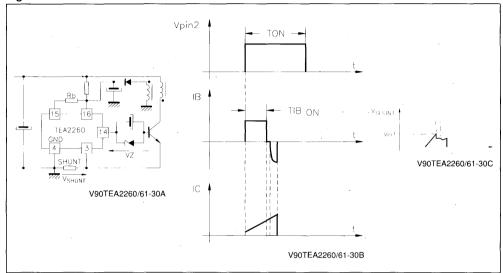

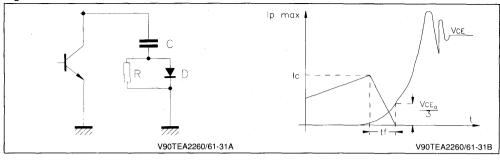

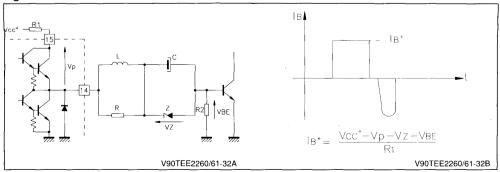

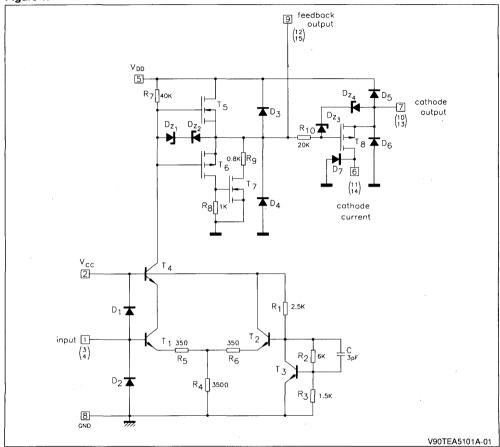

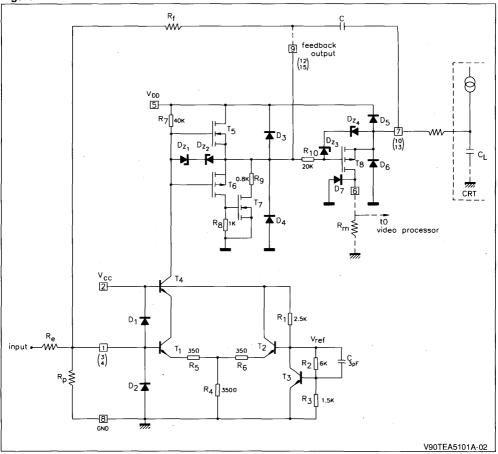

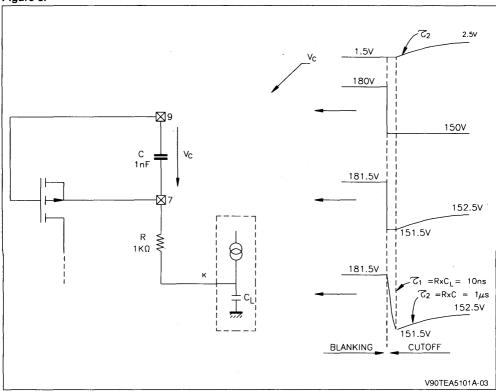

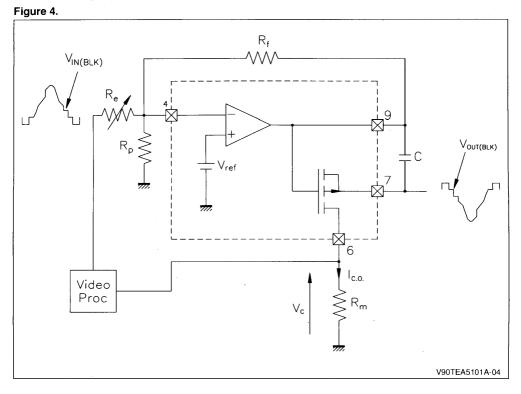

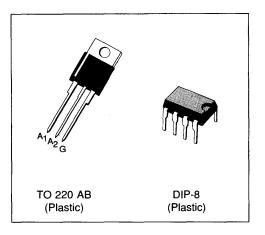

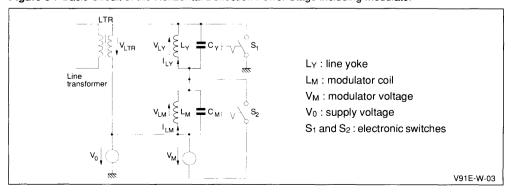

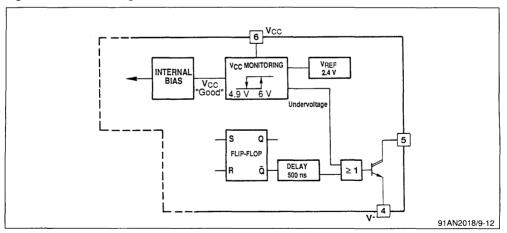

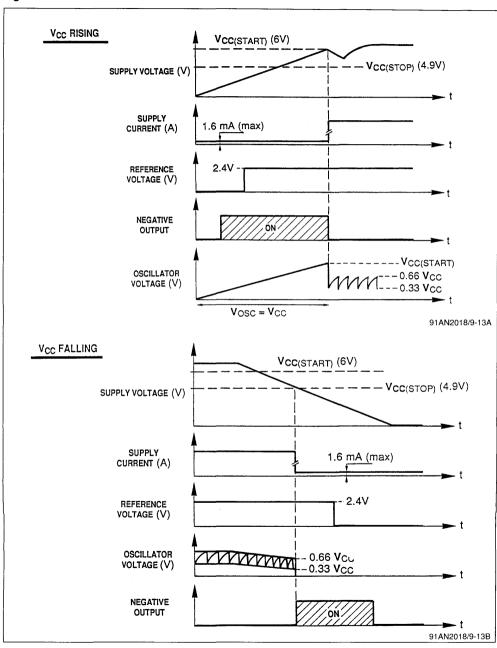

## **APPLICATION NOTE**

## TDA8102A

by Fabio GRILLI

| TECHNICAL INFORMATION                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| 1. A                                                                                                            | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                          |  |

| 2. II                                                                                                           | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                          |  |

| 3.1 H<br>3.2 H<br>3.3 F<br>3.4 S<br>3.5 F<br>3.6 V<br>3.7 V<br>3.8 S<br>3.9 V                                   | FUNCTIONAL DESCRIPTION  Horizontal oscillator  Horizontal synchronism shaper circuit  First phase comparator (φ 1) and phase adjustment interface circuit  Second phase comparator (φ 2) between flyback and oscillator  Phase shifter, output stage and start up circuit  Voltage regulator 8V  Vertical oscillator  S Correction circuit and DC linearity adjustment  Vertical amplitude regulation circuit  CONCLUSION | 3<br>3<br>4<br>4<br>5<br>5<br>6<br>7<br>8                                  |  |

| APPLI                                                                                                           | ICATION INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                       |  |

| 5.1 F<br>5.2 F<br>5.3 Ir<br>5.4 F<br>5.5 F<br>6. V<br>6.1 F<br>6.2 P<br>6.3 A<br>6.4 V<br>6.5 L<br>7. L<br>8. A | HORIZONTAL SECTION Frequency Pull-in range nternal sync width Phase adjustment range Flyback input VERTICAL SECTION Frequency Pull-in range Amplitude adjustment range Vertical DC reference Linearity correction LAY-OUT HINTS ADJUSTING PROCEDURE Horizontal frequency                                                                                                                                                  | 10<br>10<br>10<br>10<br>10<br>11<br>11<br>11<br>12<br>12<br>12<br>13<br>13 |  |

| 8.2 V<br>8.3 V<br>8.4 V                                                                                         | /ertical frequency /ertical amplitude and horizontal phase /ertical linearity                                                                                                                                                                                                                                                                                                                                             | 13<br>13<br>13<br>14                                                       |  |

#### **TECHNICAL INFORMATION**

#### 1. ABSTRACT

The system evolution in the monitor field leads to develop suitable I.C.'s whose performances and characteristics are mainly monitors oriented rather than TV oriented. The automatic frequencies raster preset of the monitor by computer and optical equipments leads to the adoption of Digital to Analog converters in order to set the different parameters, and consequently all regulation must be DC compatible.

High scanning frequency and low litter are additional factors that characterize the quality and the resolution of the monitor. In this note new circuit solutions on silicon, concerning the monitor field, are described. In a single I.C., making use of TTL compatible synchro pulses, horizontal and vertical processing functions and vertical ramp generation are implemented.

#### INTRODUCTION

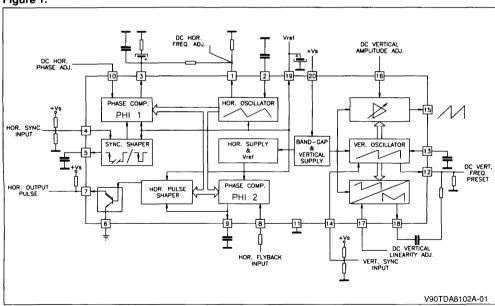

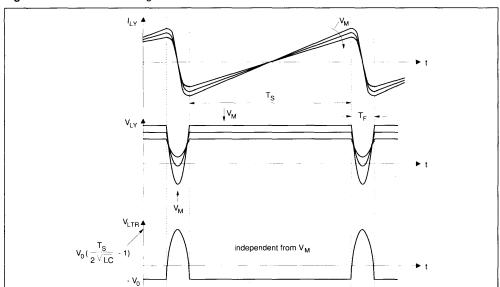

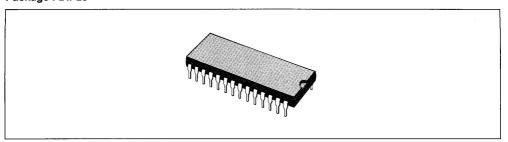

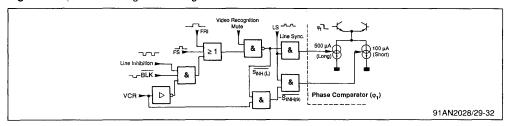

In Fig.1 is shown the block diagram of TDA8102A. Horizontal frequency and phase as well as vertical frequency, amplitude and linearity are all DC adjustable on different terminals. The horizontal phase adjustment within ± 45° is implemented on first PLL (sync-oscillator) rather than on the second PLL (flyback-oscillator) allowing the raster to be centered in case of no standard phase sync position.

An additional feature makes the raster phase independent by the duty-cycle of the input synchronizing pulse thanks to an internal shaper circuit generating a standard sync pulse starting from the leading edge of input signal.

The vertical amplitude changes depending on a voltage amplifier whose gain is set on Pin 16; the peak to peak voltage of the sawtooth does not influence its average value which is maintained constant.

The current capability of the horizontal output stage (Pin 7) is such to directly drive an external darlington used as line power switch.

Since part of the litter effect is due to the internal voltage reference circuits, an external pin connected to the V<sub>CO</sub> supply voltage is got available for noise filtering (Pin 19).

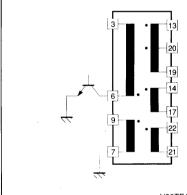

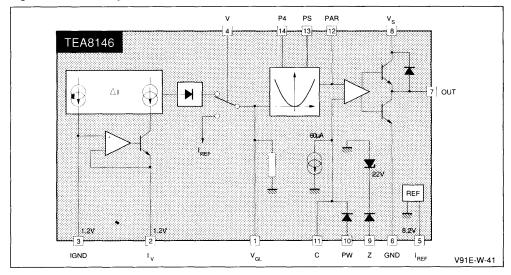

Figure 1.

#### 3. FUNCTIONAL DESCRIPTION

Here following are briefly described all the functional blocks of TDA8102A.

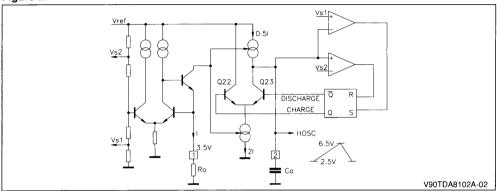

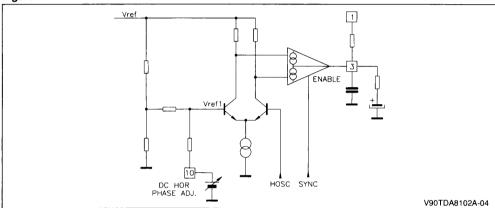

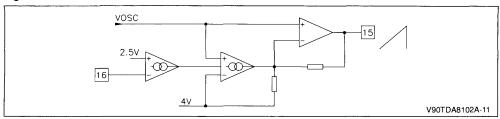

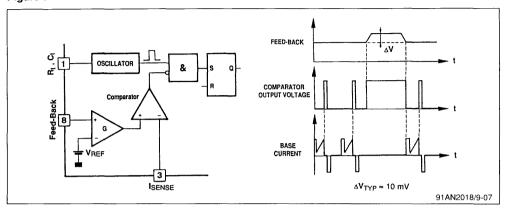

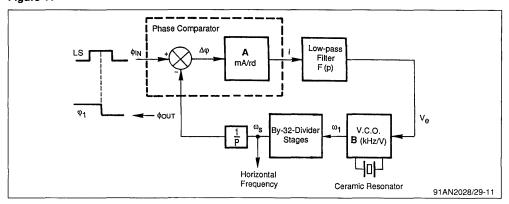

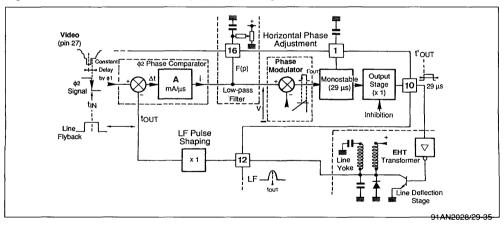

#### 3.1 Horizontal oscillator

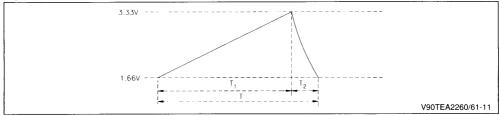

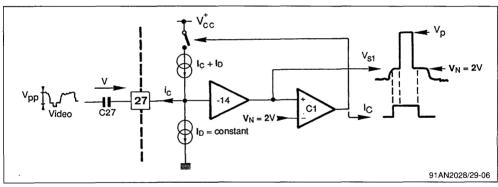

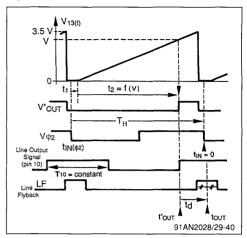

The circuit in Fig.2 is a Current Controlled Oscillator, it works charging and discharging the capacitor at pin 2 between two thresholds  $V_{S1}=2.5V$  and  $V_{S2}=6.5V$  coming from an internal resistor divider. This one is also used to provide a voltage reference at pin 1 ( $V_1=3.5V$ ) by means of a unity gain amplifier.

An external resistor connected between Pin 1 and around sets the current reference.

This current is mirrored with 0.5:1 ratio to charge the capacitor  $C_O$  at Pin 2, and with 2:1 ratio to discharge  $C_O$ .

The charging and discharging time ratio will result in 3:1.

The differential switch  $Q_{22}$ - $Q_{23}$  is driven by a S-R flip-flop, which changes its state every time that the peak of the triangular waveform reaches one of the two thresholds  $V_{S1}$  or  $V_{S2}$ .

Figure 2.

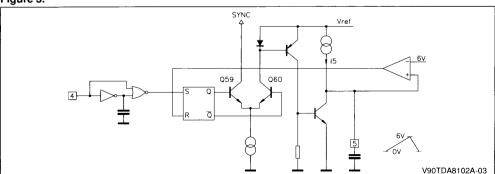

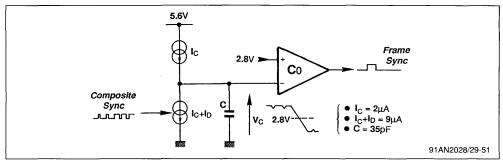

## 3.2 Horizontal synchronism shaper circuit

The electric diagram shown in Fig.3 can be divided in three stages. The first of which is a negative edge detector able to set the S-R flip-flop each time that a negative edge of the sync pulse is applied to the input (Pin 4).

The second one is a differential stage that feeds the first phase comparator ( $\phi$  1).

The third stage uses an external capacitor to produce a ramp on the Pin 5. As soon as the peak of the ramp reaches the internal threshold (6V) the external capacitor is suddenly discharged and the flip-flop is reset.

The horizonal sync pulse width on the collector of  $Q_{59}$  will depend on the value of the capacitor at Pin 5.

Figure 3.

# 3.3 First phase comparator ( $\phi$ 1) and phase adjustment interface circuit

In the circuit of Fig.4, a comparator squares the horizontal waveform using as voltage reference Vref1 which represents the output of the phase adjustment interface circuit.

If the voltage at Pin 10 changes in the range from 0.5V to 4.5V, the phase will shift of  $\pm\,45^\circ$  between the sync and the flyback pulse.

The rectangular waveforms that are the outputs of first differential amplifier are applied to another differential stage which is activated only during the horizontal sync pulse coming from the horizontal sync shaper circuit.

The product in terms of current of the sync signal and the oscillator signal is available at Pin 3.

Two clamp limit the maximum voltage range of Pin 3 (from 1V to 6V) and consequently the hold in range of the CCO.

Figure 4.

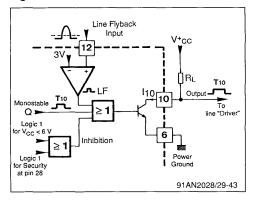

# 3.4 Second phase comparator ( $\phi$ 2) between flyback and oscillator

This circuit recovers dynamically the deflection delay of line output transistor.

The flyback pulse applied to Pin 8 (see Fig.5) is detected and clamped at a voltage level of 0.7V.

This circuit is similar to  $\phi$  1, the substantial differences are two, the input pulse is the flyback pulse instead of sync pulse and the first differential stage is activated by S-R flip-flop of horizontal oscillator.

The  $\phi$  2 output acts on the horizontal output stage in order to shift the output pulse to recover the deflection delay.

Figure 5.

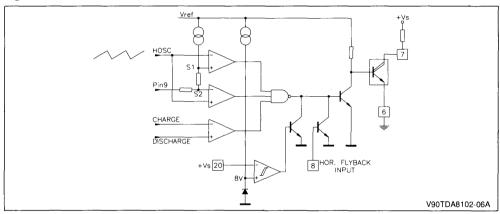

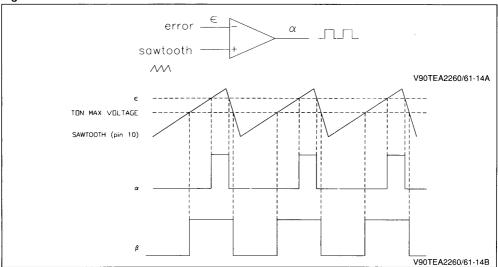

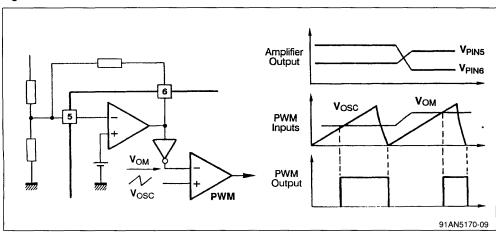

# 3.5 Phase shifter, output stage and start up circuit

The storage time ts of the line output transistor is recovered by advancing the leading edge of the output pulse of ts with respect to the phase of the sync reference.

The triangular oscillator waveform (Fig.6a) is compared with internal threshold  $S_1$  and  $S_2$  whose voltages depend upon the voltage level present at the output of phase comparator  $\phi$  2.

The voltage difference  $S_1$ - $S_2$  is constant and this value fixes the duty-cycle of the horizontal output pulse present at Pin 7.

During the positive slope of the oscillator the output pulse (Pin 7) is low when the triangular waveform voltage is in the voltage range established by  $S_1$  and  $S_2$ ; whereas during the negative slope of the oscillator the output pulse is always at high level thanks to a comparator drived by S-R flip-flop of horizontal oscillator.

As shown in Fig.6a, a transistor insures that the output pulse is low when the flyback pulse is present

At the switch on, the horizontal output stage (Pin 7) is inhibited until the power supply does not overcome 8 V

Figure 6a.

Figure 6b.

About the maximun allowable delay, it depends on the flyback time and the working frequency (see Fig.6b).

The PLL2 works in such a way to maintain the middle of the flyback exactly in correspondence between the crossing of the  $V_{REF} = 4.5V$  and the oscillator ramp.

Then if you suppose to have zero delay time, the switch-off edge of the output pulse will rise at point "A" now if the delay time increases the switch-off edge will move to point "B" to recover the delay.

The equation to calculate the  $\ensuremath{t_{D}}$  with a good approximation is the following :

$$t_D = \frac{t_r}{2} \, - \, \frac{t_{FLY}}{2}$$

where  $t_R$  is the rise time of the horizontal ramp = 3/4 T and  $t_{FLY}$  is the flyback time.

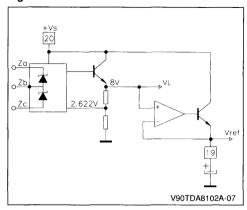

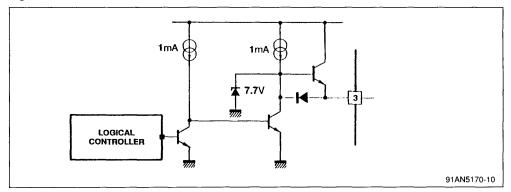

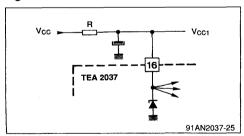

# 3.6 Voltage regulator 8 V

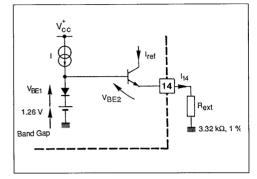

The voltage reference, Fig.7, is a band-gap circuit that allows on the output a voltage reference equal to 2.622V that means a voltage  $V_L = 8V$ .

By means of zener zap is possible to adjust, during the testing, the voltage reference from  $\pm$  6% into a  $\pm$  2% range.

$V_L$  feeds all the circuits of the vertical side and, by means of a unity gain amplifier, provides a voltage reference ( $V_{REF}$ ) at Pin 19 to supply all the circuits of the horizontal side.

The unity gain amplifier is necessary to avoid all the possible interactions between the horizontal and vertical sections.

Moreover, to minimize jitter on the horizontal oscillator, is possible to connect an external capacitor between Pin 19 and ground.

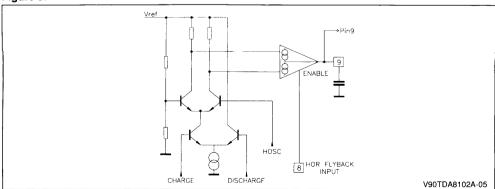

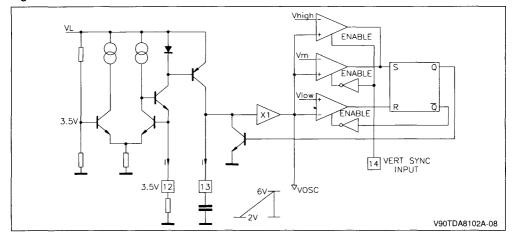

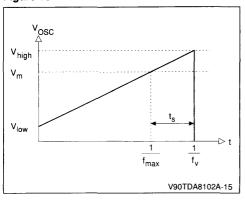

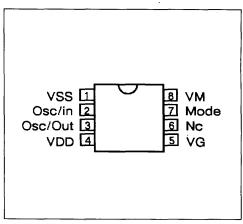

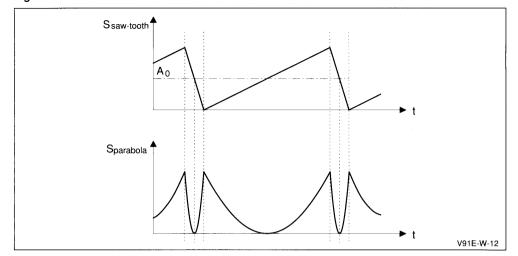

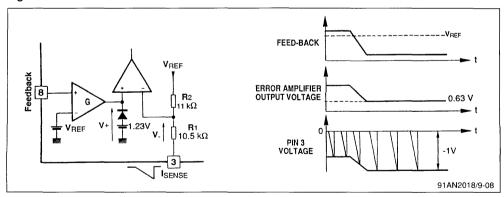

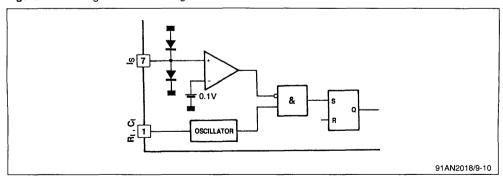

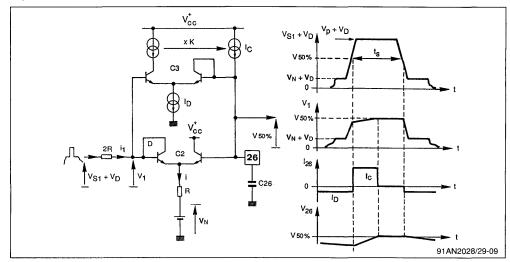

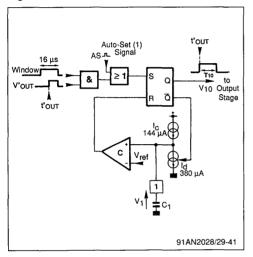

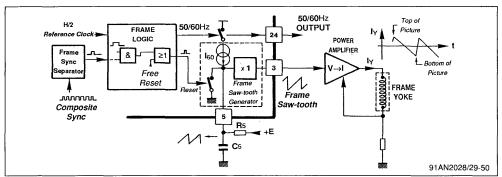

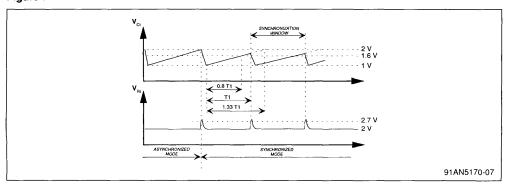

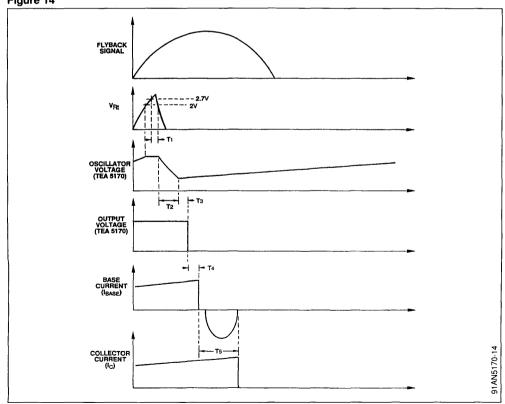

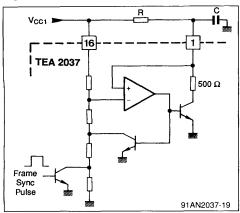

#### 3.7 Vertical oscillator

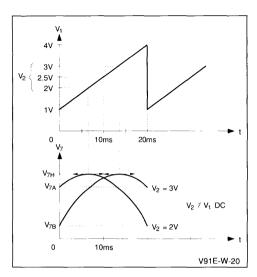

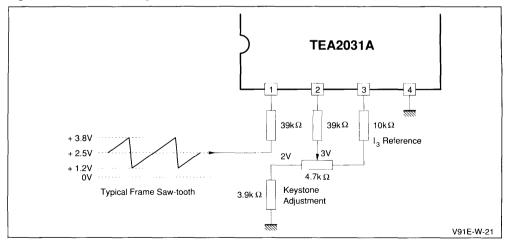

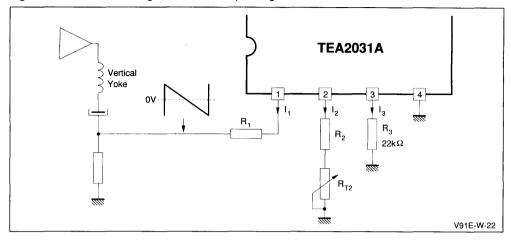

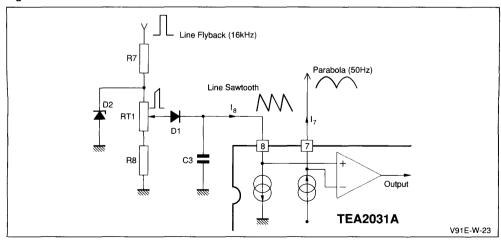

A new concept of vertical oscillator is implemented in this I.C. whose resistor divider, used to set the lower and higher thresholds ( $V_{low}=2V$ ;  $V_{high}=6.8V$ ), is not commutated .

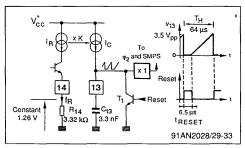

The circuit shown in Fig.8 works charging an external capacitor connected at Pin 13 with a current set at Pin 12 and reflectd to Pin 13 through a current mirror.

As soon as the ramp gets  $V_m$  or  $V_{high}$  the capacitor is quickly discharged by a darlington, the voltage on the capacitor will fall down till to get the lower threshold; at this point the darlington will be driven off and the current will charge again the capacitor. A buffer is used to decouple the ramp generator from other circuits (like linearity correction and amplitude regulation circuits).

The lower threshold is detected by a differential stage whose current generator is only activated during the discharge phase.

A comparator detects the higher threshold corresponding to the free running frequency; if no sync

Figure 7.

pulse (negative edge) is applied on Pin 14, this stage is continually fed and the capacitor at Pin 13 is discharged when the vertical ramp reaches  $V_{\text{high}}$ . If the sync pulse is present the previous comparator will be inhibited and another comparator, which has the threshold at 5.2V  $(V_m)$ , will be activated.

This last comparator, when it is set going, is able to cause the discharge of the capacitor at Pin 13 if the vertical ramp is between the thresholds Vm and  $V_{high}$ .

In this way the vertical synchronization is established.

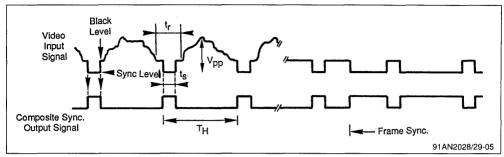

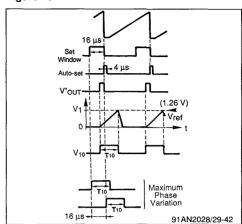

To guarantee that the vertical oscillator is locked in the middle of the pull-in range is necessary to adjust the current at Pin 12 until the peak of the vertical sawtooth, in locking condition, reaches the voltage equal to:

$$V_P = \frac{V_m + V_{high}}{2} = 6 \text{ V}$$

that means  $V_{pp} = 4V$ .

Figure 8.

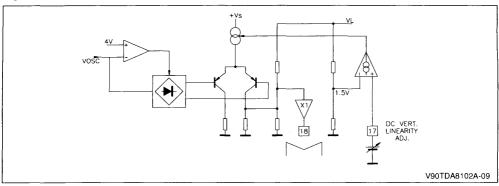

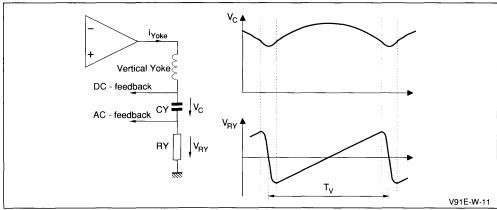

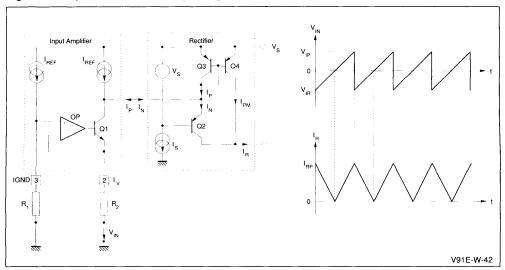

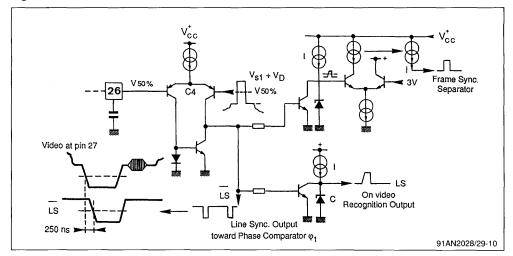

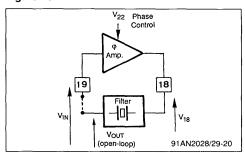

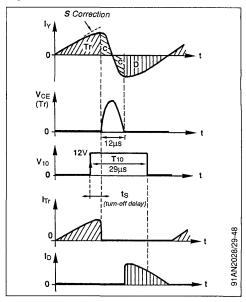

# 3.8 S Correction circuit and DC linearity adjustment

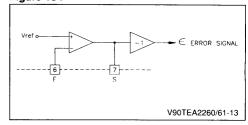

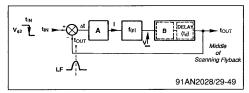

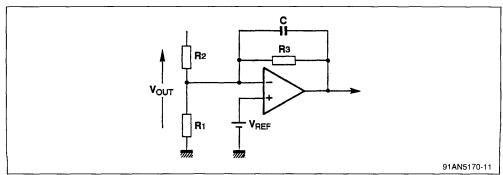

The circuit which is used to realize a new concept of vertical linearity regulation is shown in Fig.9.

A comparator squares the vertical sawtooth using as voltage reference a fixed value (4V) that is the average value of sawtooth.

This squared signal is used to drive a particular configuration of differential stage in order to obtain, in terms of current, a triangular waveform which

inverts its slope just when the original sawtooth crosses the voltage reference.

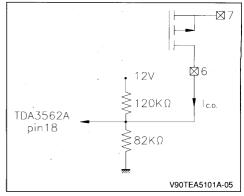

This current signal is converted in voltage by a resistor divider and transferred on Pin 18 through a buffer.

The peak to peak voltage on this pin depends on the maximum current that the output differential stage is able to handle, the value of this current can be externally regulated by means of Pin 17 through a transconductance amplifier.

Figure 9.

An external feedback resistor in series to a capacitor (to avoid any DC offset) must be connected

between Pins 18 and 12 in order to obtain the proper S correction as shown in Fig.10.

Figure 10.

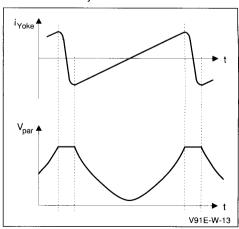

# 3.9 Vertical amplitude regulation circuit

This function has been implemented using the circuit configuration that can be seen in Fig.11.

It consists of an Op-Amp in non inverting input configuration and of a variable gain OTA whose gain can be set by means of the Pin 16 through a transconductance amplifier.

Both the inputs of the two circuit handle the vertical ramp and the output of the multiplier is fed back to the inverting input.

The control circuit is a transconductance amplifier that modulates the current of the variable gain OTA depending on the DC voltage applied on Pin 16.

This circuit guarantees a gain adjustment of  $\pm\,20\%$  around the nominal value.

# 4. CONCLUSION

This new I.C. can be considered as a first step towards a new generation of serial bus compatible LSI circuits in which additional logic function can be implemented and all the D/A converters can be included.

It is assembled in 20 pins DIL plastic package able to dissipate the 0.7W required by a typical application.

Figure 11.

# APPLICATION INFORMATION

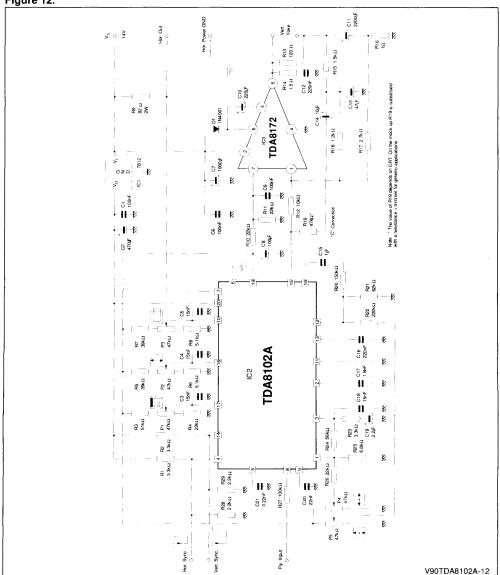

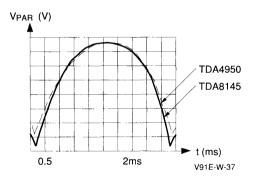

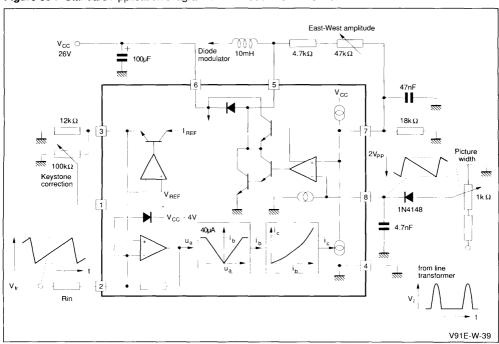

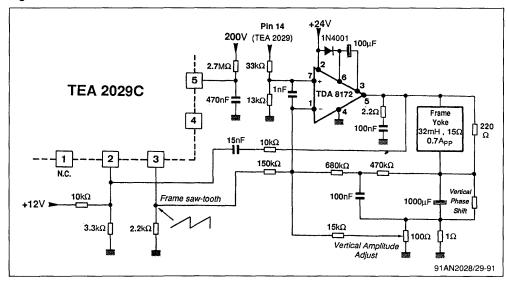

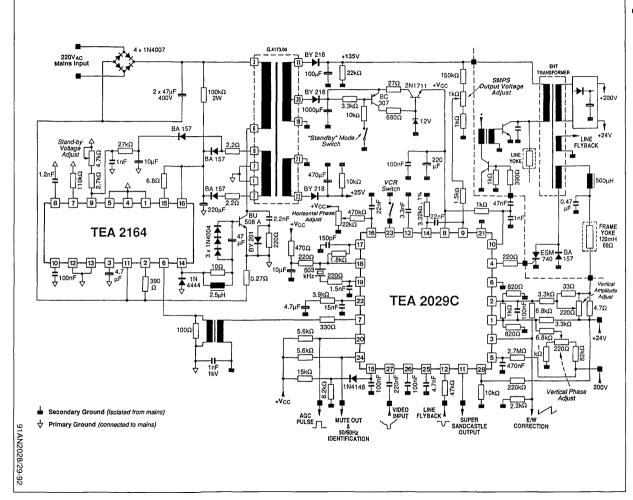

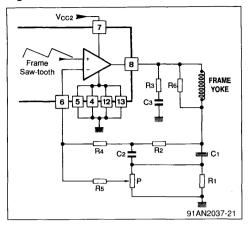

In Fig.12 is shown a typical application of the TDA8102 A with the TDA8172, which is a vertical booster; for further information regarding TDA8172 consult the note:

SGS-THOMSON "Vertical Deflection Stages for TV and Monitor" by A. MESSI

All the information is referred to the above mentioned figure.

Figure 12.

### 5. HORIZONTAL SECTION

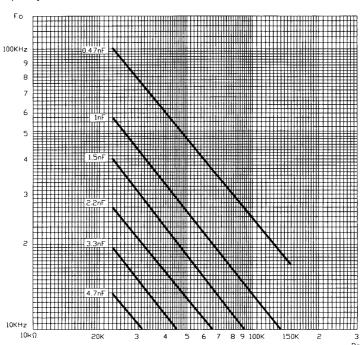

### 5.1 Frequency

The device is able to work from 15 KHz to 100 KHz. The free running frequency is fixed by the resistor at Pin 1 ( $R_{25}$ ) and by the capacitor at Pin 2 ( $C_{17}$ ) with the following formula:

$$f_O = \frac{1}{K_O \times R_{25} \times C_{17}}$$

where  $K_O$  is typically 3.0476  $\pm$  5% (see data-sheet). In the aplication of Fig.12, using  $R_{25}$  = 6.8k $\Omega$  and  $C_{17}$  = 1.8nF, we obtain:

$$f_O = \frac{10^6}{3.0476 \times 6.8 \times 1.8} = 26.808 \text{kHz}$$

The maximum available current at Pin 1 is 1mA, so it must be  $\frac{V_1}{R_{25}} \le 1$ mA.

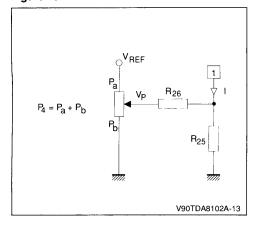

By means of trimmer P<sub>4</sub>, it is possible to adjust the horizontal free running frequency, that changes accordingly with the following formula:

$$f_H = f_O \, \Big\{ \, \, 1 - \frac{(V_p - V_1) \, / \, R_{26}}{V_1 \, / \, R_{25}} \, \Big\}$$

where  $0 \le V_p \le 8V$  is the voltage at the central point of the trimmer (see Fig.13).

Figure 13.

# 5.2 Pull-in range

This range is determined by the ability of the first comparator ( $\phi$  1) to correct the difference between the sync frequency and the free running frequency and it is set by  $R_{24}$  and  $R_{25}$ .

$$f_{pull-in} = f_O \, \frac{\mid V_3 - V_1 \mid / \, R_{24}}{V_1 \, / \, R_{25}}$$

$|V_3 - V_1|$  is typically 2.5V, while  $V_1 = 3.5V$ .

This is the theoretical value calculated if the frequency adjustment is disconnected.

In the application inf Fig.12 we have:

$$f_{pull-in} = 26808 \; \frac{2.5}{3.5} \; \frac{6800}{56000} = \pm \; 2.3 \text{kHz}$$

When the frequency adjustment is connected the pull-in range changes due to the fact that in parallel with  $R_{25}$  are connected  $R_{26}$  +  $P_b$  (see Fig.13).

When the device is synchronized and perfectly tuned,  $V_3 = V_1$  and the  $\varphi$  1 will work in the best way.

$C_{17}$ , on the contrary of  $R_{25}$ , is influential only for the free running frequency of the horizontal oscillator; it has no effect on the pull-in range, which doesn't change in percentage with respect to the free running frequency.

If you change the horizontal frequency changing  $\mathsf{R}_{25}$  the pull-in range changes accordingly with the previous formula.

# 5.3 Internal sync. width

The internal sync. pulse is made by current generator ( $I_5$ ) that charges an external capacitor at Pin 5 ( $C_{21}$ ) up to the trigger threshold  $V_5 = 6V$ .

$$t_5 = \frac{C_{21} \times V_5}{I_5}$$

$t_5 = 1 / (12 \times f_0)$  is recommended.

# 5.4 Phase adjustment range

The voltage range accepted at Pin 10 is from 0.5V to 4.5V, so the resistor divider must be dimensioned to supply these values.

In our application we have :

$$V_{10 \text{ min}} = \frac{V_{19}}{R_7 + P_3 + R_8} R_8$$

$$= \frac{8}{39 + 47 + 5.1} 5.1$$

$$= 0.447V$$

$$V_{10 \text{ max}} = \frac{V_{19}}{R_7 + P_3 + R_8} (P_3 + R_8)$$

$$= \frac{8}{39 + 47 + 5.1} 52.1$$

$$= 4.575V$$

# 5.5 Flyback input

The resistor in series at Pin 8 ( $R_{27}$ ) must be dimensioned in order to have an input current included between 0.7mA and 2mA (typ 1mA), according with the following formula:

$$R_{27} = \frac{V_{fly} - 0.6V}{1mA}$$

### 6. VERTICAL SECTION

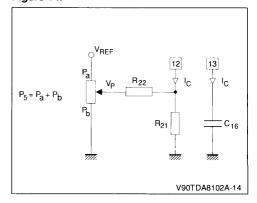

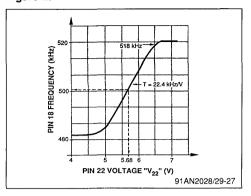

### 6.1 Frequency

The device is able to work form 30Hz to 120Hz. The free running frequency is fixed by  $R_{21}$  and  $C_{16}$ . The formula to calculate the free running frequency is the following:

$$f_v = \frac{I_C}{(V_{high} - V_{low}) \times C_{16}}$$

but

$$I_C = I = \frac{V_{12}}{R_{21}} \le 0.5 mA$$

then

$$f_v = \frac{V_{12}}{(\ V_{high} - V_{low}\ )\ x\ C_{16}\ x\ R_{21}}$$

where  $V_{12}=3.5V$ ,  $V_{high}=6.8V$  and  $V_{low}=2V$ . In the application proposed the free running frequency is:

$$f_v = \frac{3.5 \times 10^6}{(6.8 - 2) \times 220 \times 62} = 53.4 \text{Hz}$$

With the trimmer  $P_5$  is possible to change the current that charges  $C_{16}$  and consequently to change the free running frequency.

The current in C<sub>16</sub> due to this correction become:

$$I_C = \frac{V_{12}}{R_{21}} - \frac{V_P - V_{12}}{R_{22}}$$

where  $0 \le V_P \le 8V$  is the voltage at the central point of the trimmer (see Fig.14).

Figure 14.

It is easy to substitute the new  $I_C$  in the formula in order to obtain the new free running frequency.

# 6.2 Pull-in range

The vertical pull-in range is fixed by internal thresholds.

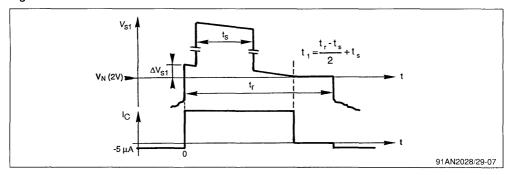

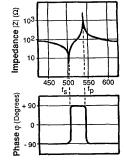

With reference to figure 15:

Figure 15.

we can write:

$$f_{pull}$$

-  $in = f_{max}$  -  $f_{v}$

$$f_{max} = \frac{1}{t_v - t_s}$$

$$t_{s} = \frac{(\ V_{high} - V_{m}\ )}{(\ V_{high} - V_{low}\ )}\ x\ t_{v} = K_{14}\ x\ t_{v}$$

the value of K<sub>14</sub> is 0.333 (see data-sheet).

# 6.3 Amplitude adjustment range

The voltage range accepted at pin 16 is from 0.5V to 4.5V.

So the resistor divider must be dimensioned to supply these values.

In our application we have:

$$V_{16min} = \frac{V_{19}}{R_5 + P_2 + R_6} R_6$$

$$= \frac{8}{39 + 47 + 5.1} 5.1$$

$$= 0.447V$$

$$V_{16\text{max}} = \frac{V_{19}}{R_5 + P_2 + R_6} (P_2 + R_6)$$

$$= \frac{8}{39 + 47 + 5.1} 52.1$$

$$= 4.575V$$

This system allows a vertical ramp amplitude variation of  $\pm$  20% around the nominal value; the value of amplitude of vertical ramp at Pin 15 can be determined with the following formula:

$$V_{15 pp} = [K_{16} (V_{16} - 2.5) + K_{15}] V_{13pp}$$

Where  $K_{15}$  is typically 1 and  $K_{16}$  is typically 0.1 (as you can see on the data-sheet).

#### 6.4 Vertical DC reference

The average value of the vertical ramp at Pin 15 is the half of  $V_{19}$ , then with a resistive divider this DC voltage can be used as reference for the vertical booster as shown in Fig.12.

For a best noise immunity we suggest to filter V<sub>19</sub> with an electrolytic capacitor.

# 6.5 Linearity correction

The "S" correction is performed with the new concept described in chapter 3.8.

The adjustment is obtained varying the DC voltage at Pin 17 from 1.5 to 4.5V, then the resistor divider (R3, P1 and R4) must be dimensioned for obtaining this range of values.

In our application we have:

$$V_{17min} = \frac{V_{19}}{R_3 + P_1 + R_4} R_4$$

$$= \frac{8}{51 + 47 + 22} 22$$

$$= 1.466V$$

$$V_{17\text{max}} = \frac{V_{19}}{R_3 + P_1 + R_4} (P_1 + R_4)$$

$$= \frac{8}{51 + 47 + 22} 69$$

$$= 4.6V$$

The "S" correction is not performed when the voltage at Pin 17 is 1.5V, while it is maximum when the Pin 17 voltage is 4.5V.

You can verify this using the following formula:

$$V_{18pp} = K_{18} (V_{17} - 1.5)$$

where K<sub>18</sub> is typically 1.

If the CRT requires a higher "S" correction, it is possible to obtain it reducing the value of  $R_{20}$ ; however take care that  $C_{15}$  in series with  $R_{20}$  is a high-pass filter with the purpose to cut only the  $D_C$ . In our application we have:

$$f_{t} = \frac{1}{6.28 \times R_{20} \times C_{15}} = \frac{10^{3}}{6.28 \times 150 \times 1} = 1.06 \text{ Hz}$$

The "C" correction is obtained with a resistor in series to a capacitor connected between Pin 15 and the central point of the vertical DC feedback of vertical booster ( $R_{19}$  and  $C_{14}$ ).

The value of  $R_{19}$  is strictly dependent on CRT used.

### 7. LAY-OUT SUGGESTIONS

It is necessary to take care not to connect the horizontal output ground (Pin 6) directly to Pin 11, to avoid horizontal interference on vertical stages. The 15nF capacitors connected on Pins 10, 16 and 17 have the only aim to filter the DC control voltage against horizontal noise, so they must be connected as close as possible to the above mentioned pins.

# 8. ADJUSTING PROCEDURE

Here following it is shortly described the procedure to adjust horizontal and vertical frequencies, verti-

cal amplitude, linearity and horizontal phase.

Before starting these operations take care that the horizontal and vertical synchronization pulses are properly applied to the device inputs.

# 8.1 Horizontal frequency

Adjust  $P_4$  in order to obtain  $V_3 = V_1$ ; in this way the horizontal synchronisation is perfect, and the pull-in range is maximum in both directions.

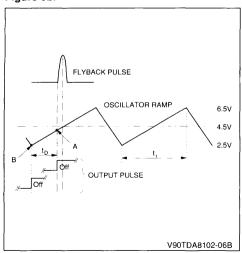

### 8.2 Vertical frequency

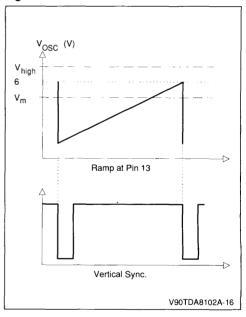

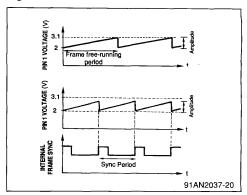

Adjust the vertical ramp amplitude using  $P_5$  in order to have  $4V_{pp}$ ; in this way the vertical frequency value is in the middle of the synchronization range; as shown in Fig.16.

Figure 16.

This operation is important because some internal circuits are dimensioned for a  $4_{Vop}$  ramp.

# 8.3 Vertical amplitude and horizontal phase

Looking at the display correct  $P_2$  for the right vertical amplitude and adjust  $P_3$  in order to have the correct horizontal phase.

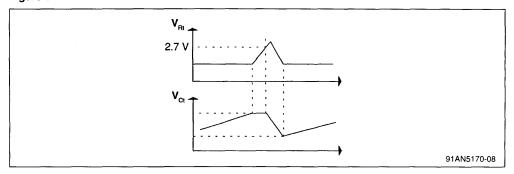

# 8.4 Vertical linearity

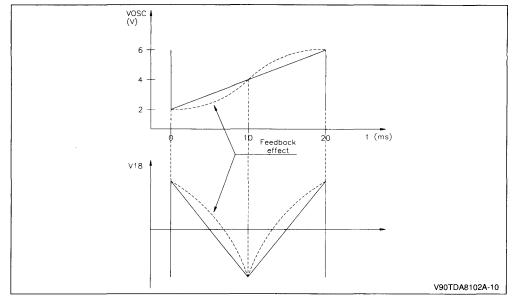

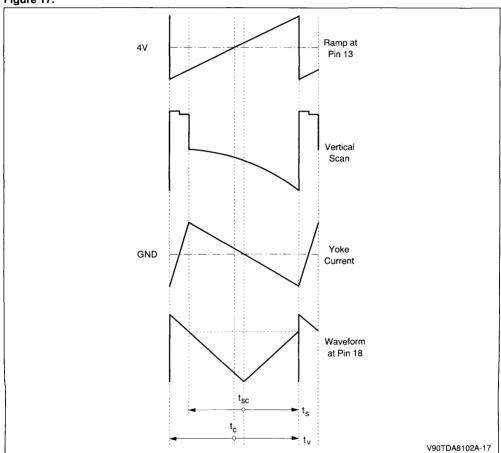

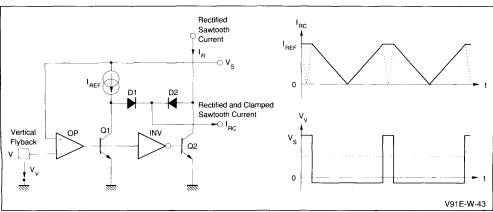

If the vertical ramp at Pin 13 is correctly set the central point of the "M" waveform at Pin 18 will be at the center of the scan; in other case, using P<sub>5</sub>, lead the central point of "M" in correspondence of the scan center (see Fig.17).

where :  $t_S$  = scan time  $t_V$  = 1/ $t_V$  = vertical period

tsc = scan centre tc = period centre

In this way the S linearity correction has a uniform behaviour on the top and bottom sides of the CRT. Now looking at the display, adjust  $P_1$  to obtain a right S correction and select  $R_{19}$  value to optimise the C correction.

Figure 17.

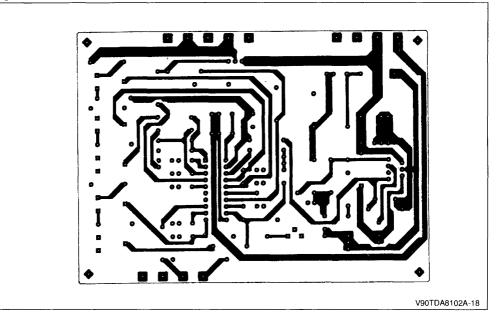

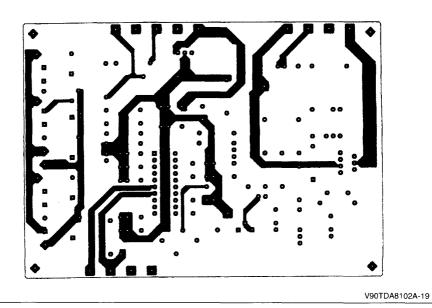

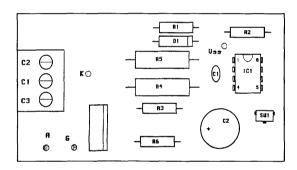

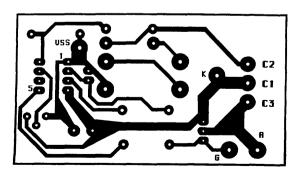

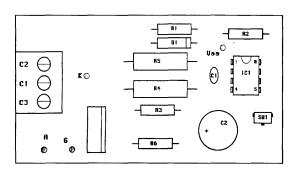

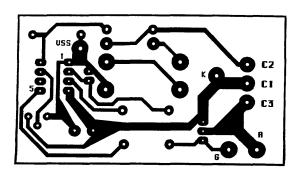

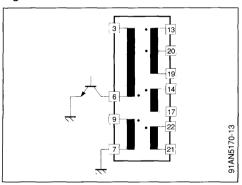

Figure 18 : Solder Side.

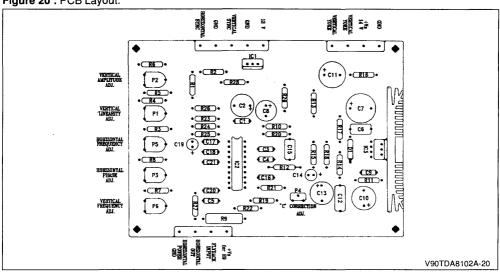

Figure 19 : Component Side.

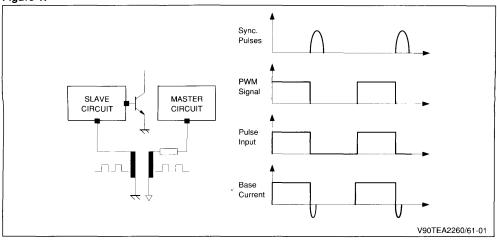

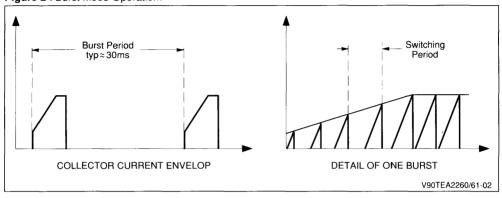

15/16

Figure 20: PCB Layout.

# 9. COMPONENT LIST

| Component                                                            | Value    | Component                                                                          | Value                | Component                         | Value        |

|----------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|----------------------|-----------------------------------|--------------|

| R <sub>1</sub> , R <sub>2</sub> , R <sub>23</sub>                    | 3.3kΩ    | R <sub>20</sub>                                                                    | 150kΩ                | C <sub>10</sub>                   | 220μF / 25V  |

| R <sub>3</sub>                                                       | 51kΩ     | R <sub>21</sub>                                                                    | 62kΩ                 | C <sub>11</sub>                   | 2200μF / 16V |

| R <sub>4</sub> , R <sub>10</sub> , R <sub>11</sub> , R <sub>26</sub> | 22kΩ     | R <sub>22</sub>                                                                    | 220kΩ                | C <sub>12</sub> , C <sub>16</sub> | 220nF        |

| R <sub>5</sub> , R <sub>7</sub>                                      | 39kΩ     | R <sub>24</sub>                                                                    | 56kΩ                 | C <sub>14</sub>                   | 10μF / 63V   |

| R <sub>6</sub> , R <sub>8</sub>                                      | 5.1kΩ    | R <sub>25</sub>                                                                    | 6.8kΩ                | C <sub>15</sub>                   | 1μF          |

| R <sub>9</sub>                                                       | 82Ω / 2W | R <sub>27</sub>                                                                    | 100kΩ                | C <sub>17</sub>                   | 1.8nF        |

| R <sub>12</sub>                                                      | 10kΩ     | R <sub>28</sub> , R <sub>29</sub>                                                  | $2.2k\Omega$         | C <sub>19</sub>                   | 2.2μF / 63V  |

| R <sub>13</sub>                                                      | 120Ω     | P <sub>1</sub> , P <sub>2</sub> , P <sub>3</sub> , P <sub>5</sub> , P <sub>6</sub> | $47$ k $\Omega$ hor. | C <sub>20</sub>                   | 22nF         |

| R <sub>14</sub>                                                      | 1.5Ω     | P <sub>4</sub>                                                                     | 47kΩ ver.            | C <sub>21</sub>                   | 220pF        |

| R <sub>15</sub>                                                      | 1.5kΩ    | C <sub>1</sub> , C <sub>6</sub> , C <sub>9</sub>                                   | 100nF                | D <sub>1</sub>                    | 1N4001       |

| R <sub>16</sub>                                                      | 1Ω       | C <sub>2</sub> , C <sub>13</sub>                                                   | 470μF / 16V          | IC <sub>1</sub>                   | L7812        |

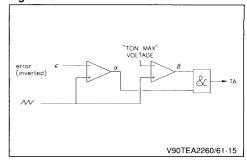

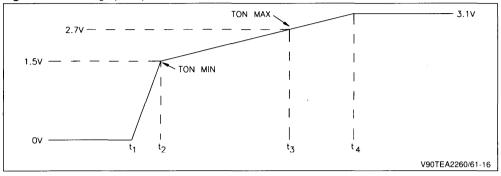

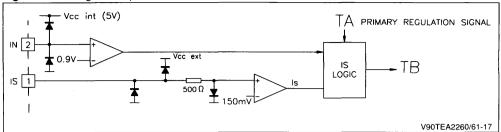

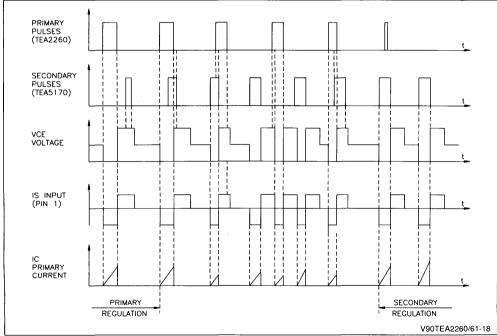

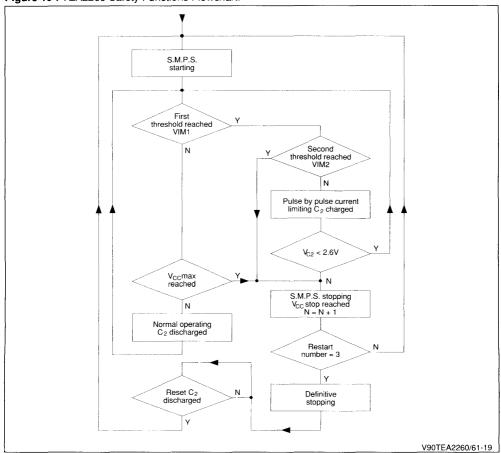

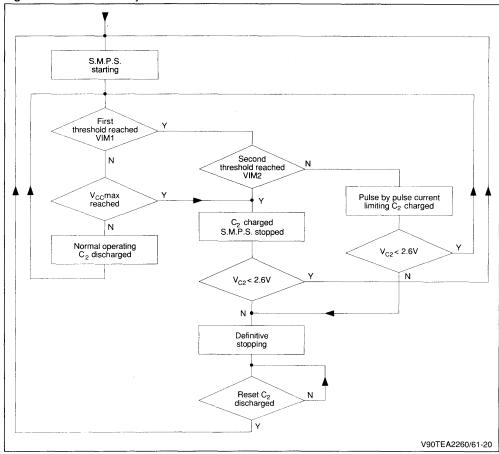

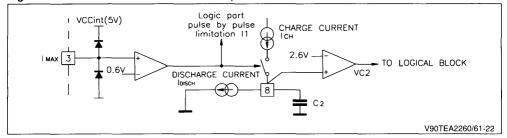

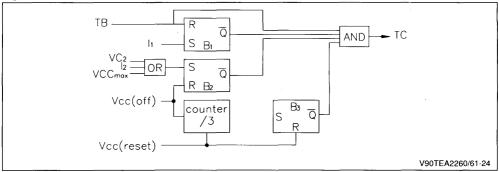

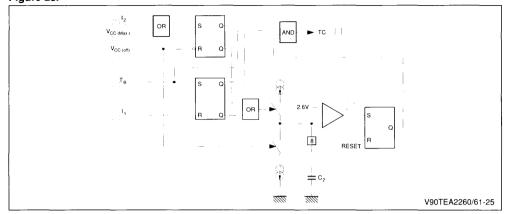

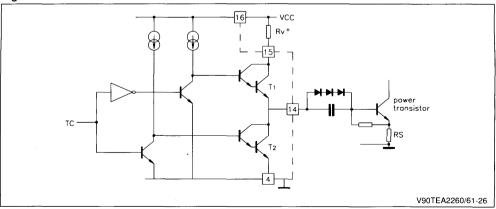

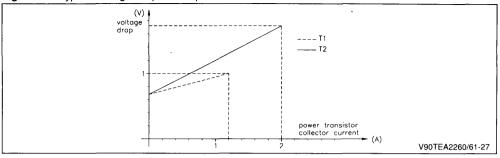

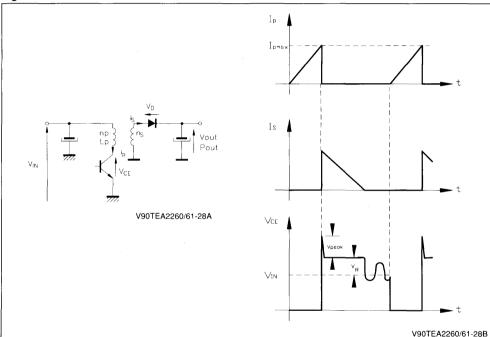

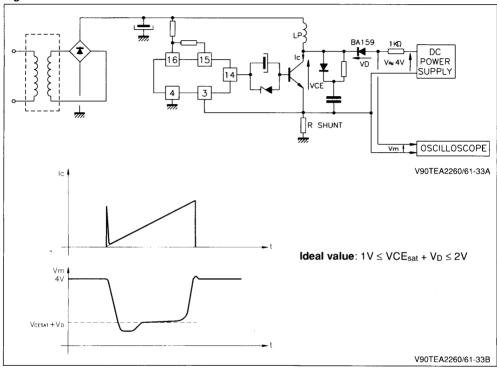

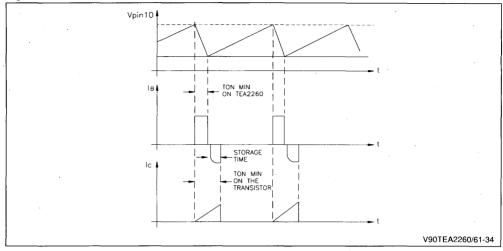

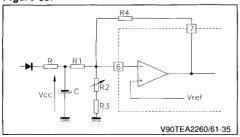

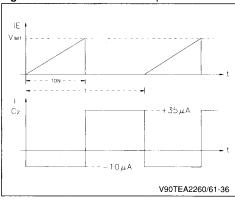

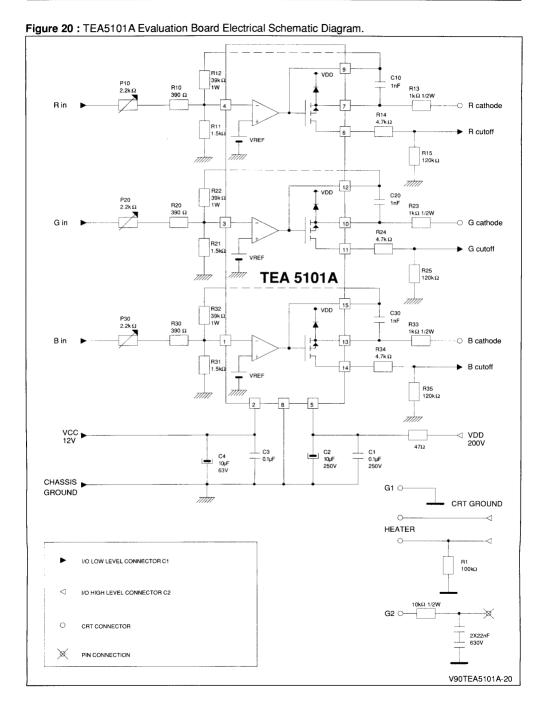

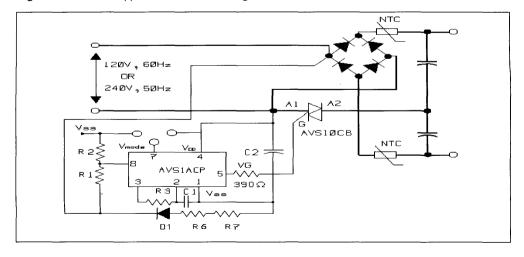

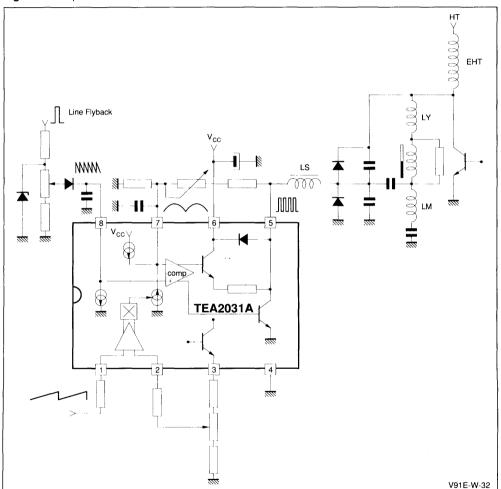

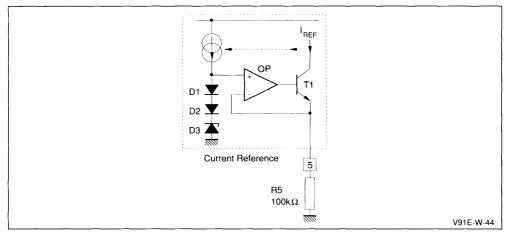

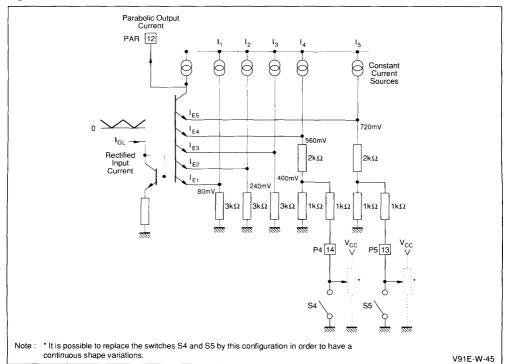

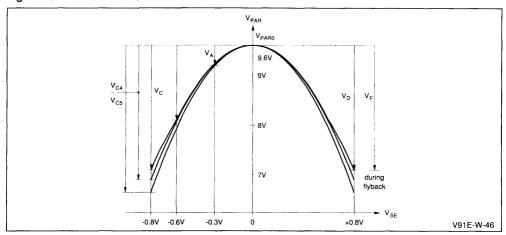

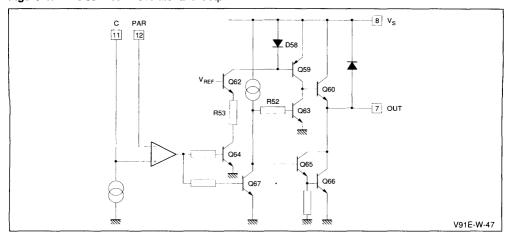

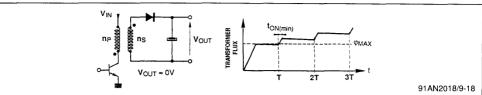

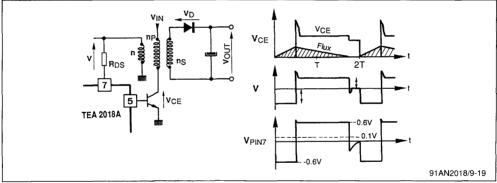

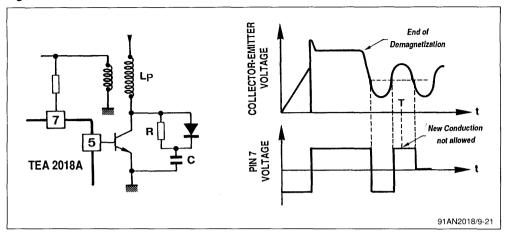

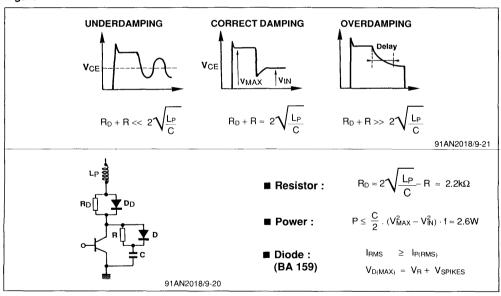

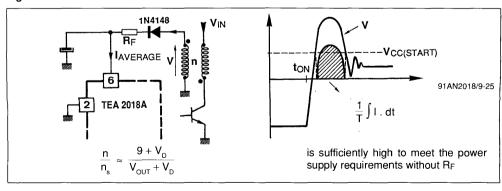

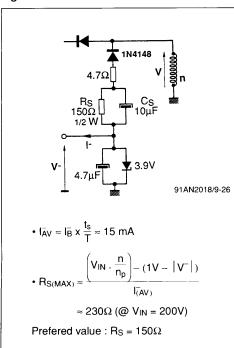

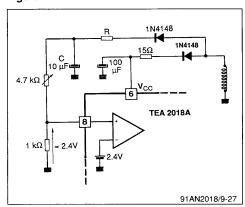

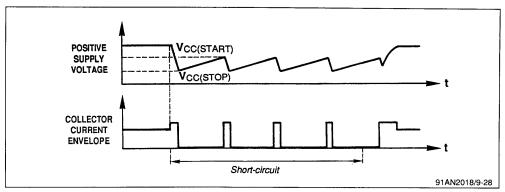

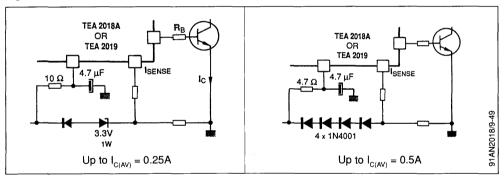

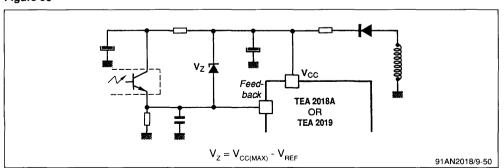

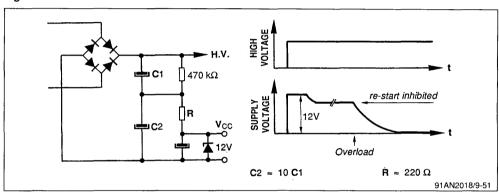

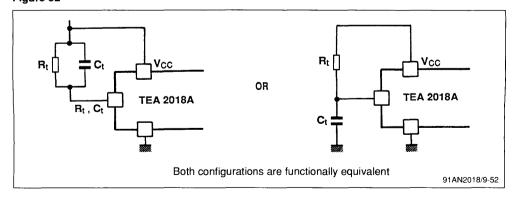

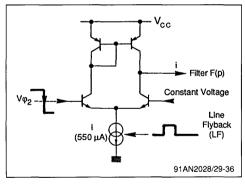

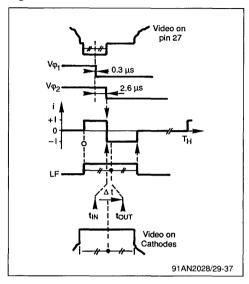

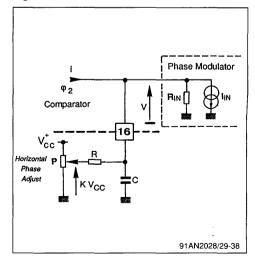

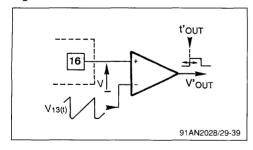

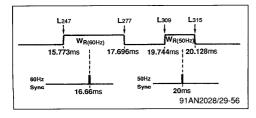

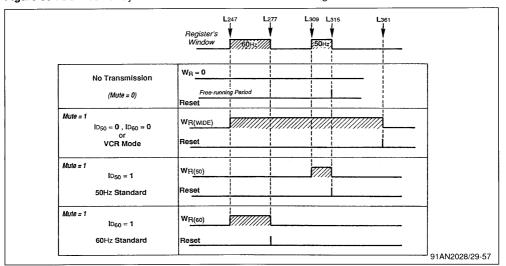

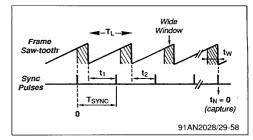

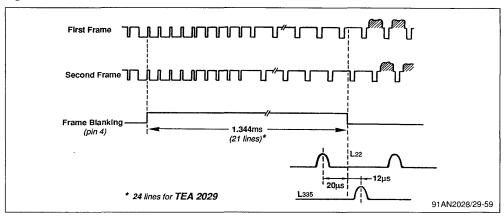

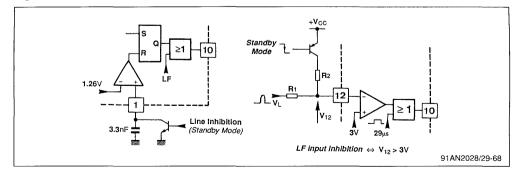

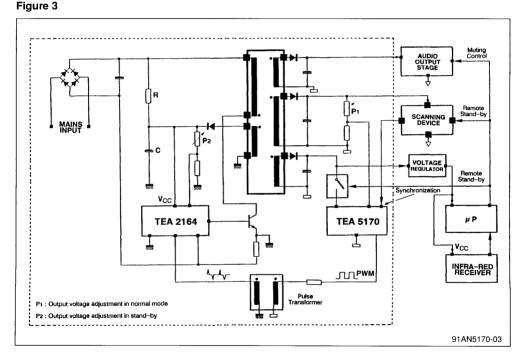

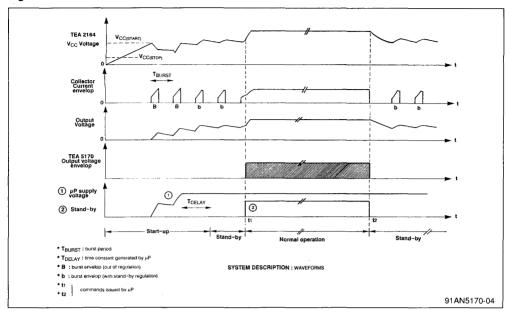

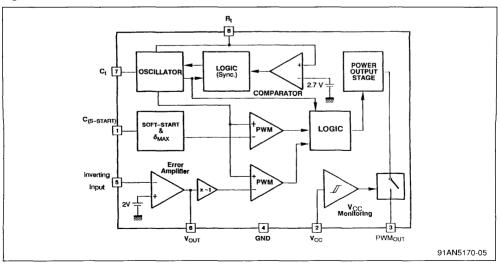

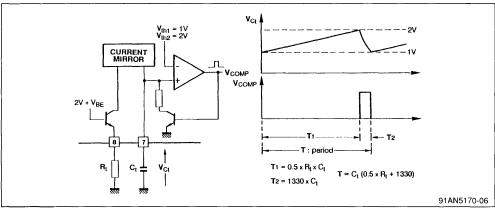

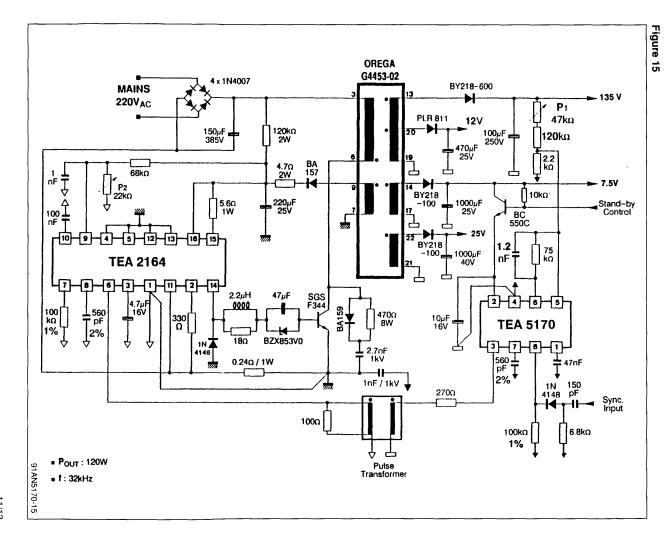

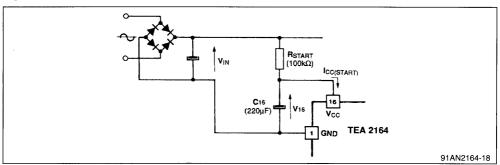

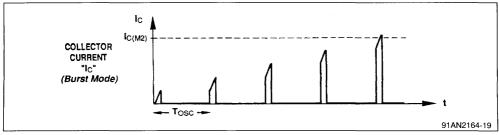

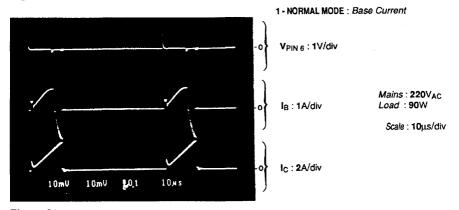

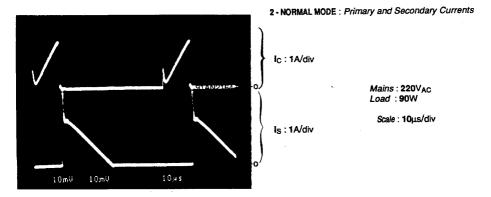

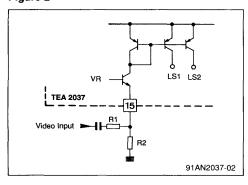

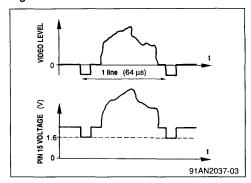

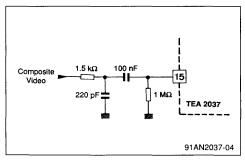

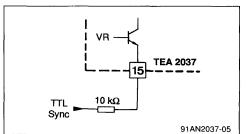

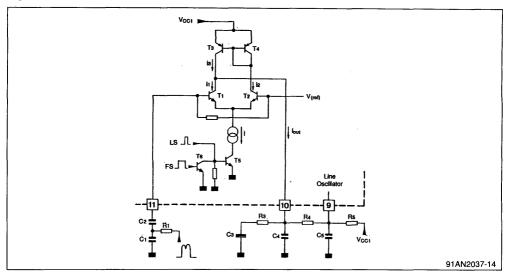

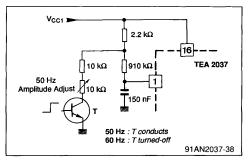

| R <sub>17</sub>                                                      | 2.7kΩ    | C <sub>3</sub> , C <sub>4</sub> , C <sub>5</sub> , C <sub>18</sub>                 | 15nF                 | IC <sub>2</sub>                   | TDA8102A     |