# VMOS Power FETs Design Catalogue

# VMOS Power FETs Design Catalog

**Siliconix** reserves the right to make changes in the circuitry or specifications in this book at any time without notice.

Siliconix assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

#### contents **Selector Guide** Index Device Types Summary Tables-RF Power FETs Process Option Flow Chart. **Data Sheets** N-Channel Enhancement Mode..... DV1210S ..... DV1220S DV1230T DV1240T **DV2820S** (formerly DV1006)...... **DV2840S** (formerly DV1007)..... DV2880T/DV2880U (formerly DV1008)..... 2-8 DV2840V DV2880V DV28120V (formerly DV1112)......2-14 VMP4 ...... 2-15 **Switching Power FETs** 2N6659/2N6660/2N6661 (Zener Protected) VK1011 ..... VN30AA/VN35AA/VN67AA/VN89AA/VN90AA VN30AB/VN35AB/VN67AB/VN89AB/VN90AB VN46AF/VN66AF/VN88AF Index 8 **Geometry Characteristics** VNK ..... **Useful Information** Index 4 **Technical Articles and Application Notes** What are VMOS Power FETs?.... AN76-3 VMOS-A Breakthrough in Power MOSFET Technology..... AR4-80 VMOS in µP Stepper Motor Control 4-19 Index 5 Mechanical Data

#### **VMOS Selector Guide**

| 2ENER 2N6658 | NON ZENER RAMA LABENV LABENV LABENV | A, J                                     |

|--------------|-------------------------------------|------------------------------------------|

| 2N6658       | LABBNV                              | A, J                                     |

|              |                                     |                                          |

|              |                                     |                                          |

|              |                                     | то-3                                     |

|              |                                     | то-3                                     |

|              |                                     | то-3                                     |

|              |                                     | TO-3                                     |

| /N90AA       | LAPPRIV                             | TO-3                                     |

| /N90AA       |                                     | TO-3                                     |

|              |                                     |                                          |

|              |                                     | B, K                                     |

|              |                                     | 1 3                                      |

|              |                                     | 19-8                                     |

|              |                                     | // \                                     |

| INICCC1      | VAIDBAK                             | 11 \                                     |

| 140001       |                                     | 11 \                                     |

| /NOOAR       | VIIISSAN                            | 11 1                                     |

| THOOLD       |                                     | TO-39                                    |

|              |                                     | F /0                                     |

|              |                                     | 41                                       |

|              |                                     |                                          |

|              |                                     | 100                                      |

|              |                                     | ///                                      |

|              |                                     | ///                                      |

|              |                                     | TO-202                                   |

|              |                                     | M                                        |

|              |                                     |                                          |

|              |                                     | la l |

|              |                                     |                                          |

| (100V)       |                                     |                                          |

|              |                                     | 1 1 1                                    |

|              |                                     | 0 0 0                                    |

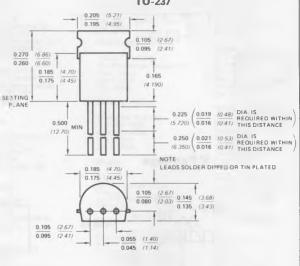

|              |                                     | TO-237                                   |

|              |                                     |                                          |

|              |                                     | -                                        |

|              |                                     | Report 1                                 |

|              |                                     |                                          |

|              |                                     |                                          |

|              |                                     | 14 pin DIP                               |

| _            | /K1010                              | VN99AK                                   |

© 1979 Siliconix incorporated

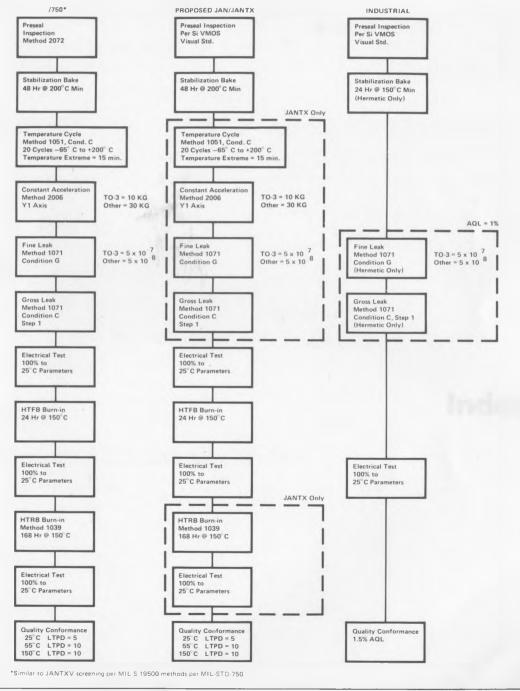

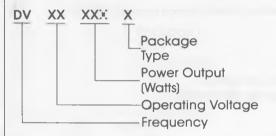

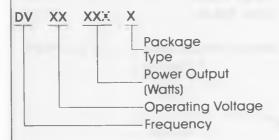

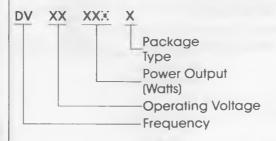

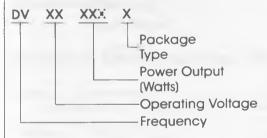

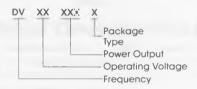

# **Process Option Flow Chart**

**Preliminary**

# n-channel enhancement-mode RF Power FETs designed for...

HF/VHF/UHF Amplifiers Class A, B, or C High Dynamic Range Amp 10 W Broadband 12.5 V 10 dB Gain 175 MHz

### **Benefits**

No Thermal Runaway

Withstands Infinite VSWR

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

# Absolute Maximum Ratings (25°C)

| Gate-Source Voltage          | 30V |

|------------------------------|-----|

| Drain-Source Voltage         | 50V |

| Drain-Gate Voltage           | 50V |

| Drain Current                | 2A  |

| Total Device Dissipation     | 40W |

| @ 25° Case                   |     |

| $\theta$ jc for .380 SOE4.4° | C/W |

Storage Temperature.... –65°C to 150°C

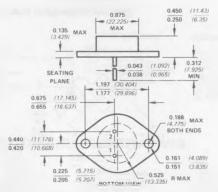

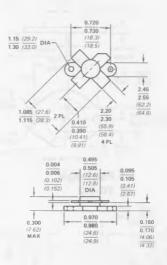

S - Package See Section 5

.380 SOE FLANGE

# Electrical Characteristics (25°C)

| Symbol                              | Characteristic                                           | Min | Тур                         | Max | Unit | Test Conditions                                                                           |

|-------------------------------------|----------------------------------------------------------|-----|-----------------------------|-----|------|-------------------------------------------------------------------------------------------|

| POUT(1)                             | Power Output                                             | 9   | 10                          |     | W    | V <sub>DD</sub> = 12.5 V, I <sub>DQ</sub> = 1 A<br>P <sub>IN</sub> = 1 W Max, F = 175 MHz |

| η(1)                                | Drain Efficiency                                         | 55  | 60                          |     | %    |                                                                                           |

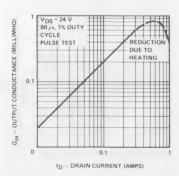

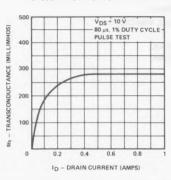

| 9m                                  | Transconductance                                         |     | 0.4                         |     | Mho  | V <sub>DS</sub> = 12.5 V, I <sub>D</sub> = 1 A                                            |

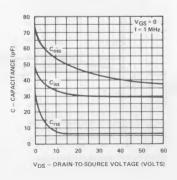

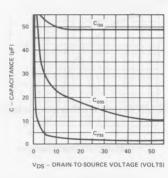

| Coss<br>Crss<br>Ciss                | Output Capacity Reverse Transfer Capacity Input Capacity |     | 49<br>7.5<br>41             |     | pF   | V <sub>DS</sub> = 12.5 V, V <sub>GS</sub> = 0 V                                           |

| Z <sub>IN</sub><br>Z <sub>OUT</sub> | Input (Series) Impedance<br>Output (Series) Impedance    |     | 3.1 + j 12.9<br>4.0 + j 4.0 |     | Ω    | V <sub>DS</sub> = 12.5 V, P <sub>IN</sub> = 1 W<br>F = 175 MHz, P <sub>OUT</sub> = 10 W   |

2-1

Note:

(1) All devices 100% power tested in Siliconix test fixture No. RF12175 [10]

©1980 Siliconix incorporated

# **Test Fixture/Applications**

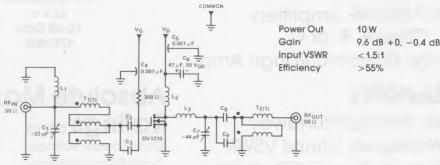

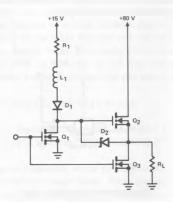

#### 135 MHz to 175 MHz, 12.5 Volt Amplifier

Notes: C<sub>1</sub>, Arco #462 trimmer capacitor, 5 to 80 pF

C7, Arco #463 trimmer capacitor, 9 to 180 pF

L<sub>1</sub>, 2 turns, \*AWG 22 on 1/4" diameter close wound

L2, 7 turns, #AWG 22 on 1/4" diameter close wound

L3, 1/2" #AWG 18 buss, 1/2-turn on 1/4" diameter

C<sub>2</sub>, C<sub>3</sub>, C<sub>8</sub>, C<sub>9</sub>, 0.01  $\mu$ F chip capacitors, Johanson P/N 201 L64 N 103 MA

$I_1$ , One turn #22 enamel wire trifilar twisted with 13 crests per inch on one Stackpole balun core #57-0973

$T_2$ , One turn  $25\,\Omega$  coax wound on two balun cores placed end on end. Stackpole balun cores #57-0973

(1) - Dot indicates winding starts

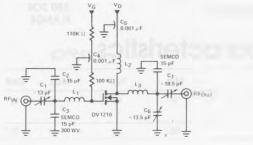

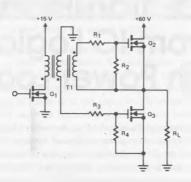

# 175 MHz, 12.5 Volt Amplifier Siliconix Test Fixture #RF12175 [10]

Power Out 10 W Gain 10 dB Efficiency >60%

Notes: C<sub>1</sub>, C<sub>2</sub>, C<sub>5</sub>, C<sub>6</sub>, Arco #462, 5 to 80 pF

L<sub>1</sub>, 2 1/2" length of #AWG 12, 1/2 turn on 1/3" diameter

L2, 8 turns #AWG 22 on 1/4" diameter, close wound

L<sub>3</sub>, 15/8" length of \*AWG 12, 1/2 turn on 1/3" diameter

Siliconix

Preliminary

# n-channel enhancement-mode RF Power FETs designed for...

HF/VHF/UHF Amplifiers

Class A, B, or C

High Dynamic Range Amp

20 W Broadband 12.5 V 10 dB Gain 175 MHz

# **Benefits**

No Thermal Runaway

Withstands Infinite VSWR

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

# Absolute Maximum Ratings (25°C)

| Gate-Source Voltage      | 30V |

|--------------------------|-----|

| Drain-Source Voltage     | 50V |

| Drain-Gate Voltage       | 50V |

| Drain Current            | 4A  |

| Total Device Dissipation | 80W |

| @ 25° Case               |     |

| $\theta$ ic for .380 SOE | C/W |

Storage Temperature.... -65°C to 150°C

S-Package see Section 5

.380 SOE FLANGE

# Electrical Characteristics (25°C)

| Symbol  | Characteristic            | Min | Тур      | Max | Unit | Test Conditions                                                                           |

|---------|---------------------------|-----|----------|-----|------|-------------------------------------------------------------------------------------------|

| POUT(1) | Power Output              | 18  | 20       |     | W    | V <sub>DD</sub> = 12.5 V, I <sub>DQ</sub> = 2 A<br>P <sub>IN</sub> = 2 W Max, F = 175 MHz |

| η(1)    | Drain Efficiency          | 55  | 60       |     | %    |                                                                                           |

| 9m      | Transconductance          |     | 0.8      |     | Mho  | V <sub>DS</sub> =12.5 V, I <sub>D</sub> =2 A                                              |

| Coss    | Output Capacity           |     | 98       |     |      |                                                                                           |

| Crss    | Reverse Transfer Capacity |     | 15       |     | pF   | $V_{DS} = 125 \text{ V}, V_{GS} = 0 \text{ V}$                                            |

| Ciss    | Input Capacity            |     | 82       |     |      |                                                                                           |

| ZIN     | Input (Series) Impedance  |     | 1.6+16.5 |     | ()   | V <sub>DS</sub> = 12.5 V, P <sub>IN</sub> = 2 W                                           |

| ZOUT    | Output (Series) Impedance |     | 2+j2     |     | 13   | F = 175 MHz, POUT = 20 W                                                                  |

|         |                           |     |          |     |      |                                                                                           |

Note: (1) All devices 100% power tested in Siliconix test fixture No. RF12175 [20]

©1980 Siliconix incorporated

**Preliminary**

# n-channel enhancement-mode RF Power FETs designed for...

HF/VHF/UHF Amplifiers Class A, B, or C High Dynamic Range Amp 30 W Broadband 12.5 V 10 dB Gain 175 MHz

### **Benefits**

No Thermal Runaway

Withstands Infinite VSWR

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

# Absolute Maximum Ratings (25°C)

| Gate-Source Voltage 30V       |

|-------------------------------|

| Drain-Source Voltage50V       |

| Drain-Gate Voltage50V         |

| Drain Current6A               |

| Total Device Dissipation 120W |

| @ 25° Case                    |

| θjc for .500 J0 1.5°C/W       |

Storage Temperature.... – 65°C to 150°C

T-Package

see Section 5

.500 JO

# Electrical Characteristics (25°C)

| Symbol                              | Characteristic                                           | Min | Тур                | Max | Unit | Test Conditions                                                                         |

|-------------------------------------|----------------------------------------------------------|-----|--------------------|-----|------|-----------------------------------------------------------------------------------------|

| POUT(1)                             | Power Output                                             | 27  | 30                 |     | W    | V <sub>DD</sub> =12.5 V, I <sub>DQ</sub> =3 A<br>P <sub>IN</sub> =3 W Max, F=175 MHz    |

| η(1)                                | Drain Efficiency                                         | 55  | 60                 |     | %    |                                                                                         |

| 9m                                  | Transconductance                                         |     | 1.2                |     | Mho  | V <sub>DS</sub> = 12.5 V, I <sub>D</sub> = 3 A                                          |

| Coss<br>Crss<br>Ciss                | Output Capacity Reverse Transfer Capacity Input Capacity |     | 147<br>22.5<br>123 |     | рF   | V <sub>DS</sub> =12.5 V, V <sub>GS</sub> =0 V                                           |

| Z <sub>IN</sub><br>Z <sub>OUT</sub> | Input (Series) Impedance<br>Output (Series) Impedance    |     | 1+j4.3<br>1.3+j1.3 |     | Ω    | V <sub>DS</sub> = 12.5 V, P <sub>IN</sub> = 3 W<br>F = 175 MHz, P <sub>OUT</sub> = 30 W |

Note: (1) All devices 100% power tested in Siliconix test fixture No. RF12175 [30]

©1980 Sillconix Incorporated

Siliconix

Preliminary

# n-channel enhancement-mode RF Power FETs designed for...

HF/VHF/UHF Amplifiers Class A, B, or C High Dynamic Range Amp 40 W Broadband 12.5 V 10 dB Gain 175 MHz

## **Benefits**

No Thermal Runaway

Withstands Infinite VSWR

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

# Absolute Maximum Ratings (25°C)

| Gate-Source Voltage 30V        |

|--------------------------------|

| Drain-Source Voltage 50V       |

| Drain-Gate Voltage50V          |

| Drain Current8A                |

| Total Device Dissipation 160W  |

| @ 25° Case                     |

| $\theta$ jc for .500 J01.1°C/W |

Storage Temperature.... -65°C to 150°C

T-Package

see Section 5

.500 J0 FLANGE

# Electrical Characteristics (25°C)

| Symbol                              | Characteristic                                           | Min | Тур                  | Max | Unit | Test Conditions                                                                      |

|-------------------------------------|----------------------------------------------------------|-----|----------------------|-----|------|--------------------------------------------------------------------------------------|

| POUT(1)                             | Power Output                                             | 36  | 40                   |     | W    | V <sub>DD</sub> =12.5 V, I <sub>DQ</sub> =4 A<br>P <sub>IN</sub> =4 W Max, F=175 MHz |

| η(1)                                | Drain Efficiency                                         | 55  | 60                   |     | %    |                                                                                      |

| 9m                                  | Transconductance                                         |     | 1.6                  |     | Mho  | V <sub>DS</sub> = 12.5 V, I <sub>D</sub> = 4.0 A                                     |

| Coss<br>Crss<br>Ciss                | Output Capacity Reverse Transfer Capacity Input Capacity |     | 196<br>30<br>164     |     | pF   | V <sub>DS</sub> =12.5 V, V <sub>GS</sub> =0 V                                        |

| Z <sub>IN</sub><br>Z <sub>OUT</sub> | Input (Series) Impedance<br>Output (Series) Impedance    |     | 0.8+j3.2<br>1.0+j1.0 |     | Ω    | V <sub>DS</sub> =12.5 V, P <sub>IN</sub> =4 W<br>F=175 MHz, P <sub>OUT</sub> =40 W   |

Note: (1) All devices 100% power tested in Siliconix test fixture No. RF12175 [40]

©1980 Siliconix incorporated

n-channel enhancement-mode RF VMOS power FET designed for...

**Preliminary**

HF/VHF/UHF Amplifiers Class A, B, or C 25 WATTS 20 W BROADBAND 28 V 10 dB GAIN 175 MHz

**High Dynamic Range Amplifier**

#### **Benefits**

Infinite VSWR

No Thermal Runaway

Broadband Capability

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

S-Parameter Design

#### ABSOLUTE MAXIMUM RATINGS (25°C)

| Gate-Source Voltage        | 40 V           |

|----------------------------|----------------|

| Drain Source Voltage       | 80 V           |

| Drain-Gate Voltage         | 80 V           |

| Drain Current              | 2 A            |

| Total Device Dissipation @ | 25° Case 40 W  |

| Storage Temperature        | -65°C to 150°C |

| θ jc S- Packag             | 4.4 °C/W       |

see Section 5

380 SOE FLANGE

# Electrical Characteristics (25°C)

| SYMBOL               | CHARACTERISTIC            | MIN | TYP          | MAX | UNIT | TEST CONDITIONS                                           |

|----------------------|---------------------------|-----|--------------|-----|------|-----------------------------------------------------------|

| P <sub>OUT</sub> (1) | POWER OUTPUT              | 20  |              |     | W    | V <sub>DD</sub> =28 V, I <sub>DQ</sub> = 100 mA           |

| 00,                  |                           |     |              |     |      | P <sub>IN</sub> = 2 W Max, F= 175 MHz                     |

| η(1)                 | DRAIN EFFICIENCY          | 60  |              |     | -%   |                                                           |

| gm                   | TRANCONDUCTANCE           |     | 0.250        |     | Mho  | V <sub>DS</sub> =28 V <sub>1</sub> I <sub>D</sub> = 1A    |

| Coss                 | OUTPUT CAPACITY           |     | 32           |     |      |                                                           |

| Crss                 | REVERSE TRANSFER CAPACITY |     | 4.0          |     | pF   | V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0               |

| Ciss                 | INPUT CAPACITY            |     | 48           |     |      |                                                           |

| Z <sub>IN</sub> (2)  | INPUT (SERIES) IMPEDANCE  |     |              |     | 0    | V <sub>DS</sub> = 28 V, P <sub>IN</sub> = 0.5 W           |

| Z <sub>OUT</sub>     | OUTPUT (SERIES) IMPEDANCE |     | 12.5 - j7.42 |     | Ω    | o = 100 MHz, P <sub>OUT</sub> = 20 W                      |

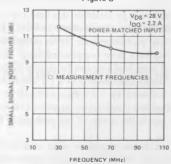

| NF <sup>(3)</sup>    | SMALL SIGNAL NOISE FIGURE |     | 4            |     | dB   | F = 175 MHz, V <sub>DS</sub> 28 V<br>I <sub>D</sub> 0.1 A |

#### NOTES:

- (1) All devices 100% power tested in Siliconix test fixture No. RF 28175 [20].

- (2) ZIN dependent on feedback network

- (3) Noise figure measured with 20 Watt power matched source and load.

**Preliminary**

n-channel enhancement-mode RF VMOS power FET designed for...

HF/VHF/UHF Amplifiers Class A, B, or C

**High Dynamic Range Amplifier**

#### **Benefits**

Infinite VSWR

No Thermal Runaway

Broadband Capability

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

S-Parameter Design

50 WATTS 40 W BROADBAND 28 V 10 dB GAIN 175 MHz

#### ABSOLUTE MAXIMUM RATINGS (25°C)

| Gate-Source Voltage                 | 40 V      |

|-------------------------------------|-----------|

| Drain-Source Voltage                | 80 V      |

| Drain-Gate Voltage                  | 80 V      |

| Drain Current                       | 4 A       |

| Total Device Dissipation @ 25° Case | 80 W      |

| φjc                                 | 2.2 °C/W  |

| Storage Temperature -65°C           | to 150° C |

S-Package see Section 5

380 SOE FLANGE

### Electrical Characteristics (25°C)

| SYMBOL               | CHARACTERISTIC                                           | MIN | TYP             | MAX | UNIT | TEST CONDITIONS                                                                                    |

|----------------------|----------------------------------------------------------|-----|-----------------|-----|------|----------------------------------------------------------------------------------------------------|

| P <sub>OUT</sub> (1) | POWER OUTPUT                                             | 40  |                 |     | w    | V <sub>DD</sub> =28 V, I <sub>DQ</sub> = 0 2 A<br>P <sub>IN</sub> = 4 W Max, F= 175 MH.            |

| η(1)                 | DRAIN EFFICIENCY                                         | 60  |                 |     | %    |                                                                                                    |

| gm                   | TRANCONDUCTANCE                                          |     | 0.5             |     | Mho  | V <sub>DS</sub> =28 V, I <sub>D</sub> = 2A                                                         |

| Coss<br>Crss<br>Ciss | OUTPUT CAPACITY REVERSE TRANSFER CAPACITY INPUT CAPACITY |     | 65<br>8.5<br>95 |     | pF   | V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0                                                        |

| Z <sub>IN</sub> (2)  | INPUT (SERIES) IMPEDANCE OUTPUT (SERIES) IMPEDANCE       |     | 6.5 - j4.2      |     | Ω    | V <sub>DS</sub> = 28 V <sub>PIN</sub> = 1,3 W<br>F <sub>O</sub> = 100 MHz, P <sub>OUT</sub> = 40 W |

| NF <sup>(3)</sup>    | SMALL SIGNAL NOISE FIGURE                                |     | 7               |     | dB   | F = 175 MHz, V <sub>DS</sub> =28 V<br>I <sub>D</sub> = 0.2 A                                       |

#### NOTES:

- (1) All devices 100% power tested in Siliconix test fixture No. RF 28175 [40].

- (2) ZIN dependent on feedback network.

- (3) Noise figure measured with 40 Watt power matched source and load.

Siliconix

n-channel enhancement-mode RF Power FETs designed for...

HF/VHF/UHF Amplifiers Class A, B, or C High Dynamic Range Amp

175 MHz 28-35 V 100 W 10 dB

### **Benefits**

Infinite VSWR No Thermal Runaway **Broadband Capability** Class A, B, or C Operation Low Noise Figure High Dynamic Range Simple Bias Circuitry S-Parameter Design

# **Absolute Maximum** Ratings (25°C)

| Gate-Source Voltage40 V                      |

|----------------------------------------------|

| Drain-Source Voltage 80 V                    |

| Drain-Gate Voltage80 V                       |

| Drain Current8 A                             |

| Total Device Dissipation 160 W<br>@ 25° Case |

| <i>θ</i> jc 1.1°C/W                          |

| Storage Temperature 65°C to 150°C            |

| Junction Temperature200°C                    |

#### T-Package

**FLANGE**

#### **U-Package**

.500 SOE **FLANGE**

see Section 5

# Electrical Characteristics (25°C)

| Symbol  | Characteristic            | Min | Тур | Max | Unit | Test Conditions                                           |

|---------|---------------------------|-----|-----|-----|------|-----------------------------------------------------------|

| POUT(1) | Power Output              | 80  |     |     | W    | V <sub>DS</sub> =28 V, I <sub>DQ</sub> =0.4 A             |

| η(1)    | Drain Efficiency          |     | 60  |     | %    | - P <sub>IN</sub> =8 W, f=175 MHz                         |

| 9m      | Transconductance          |     | 1.0 |     | Mho  | V <sub>DS</sub> =28 V, I <sub>D</sub> =4 A                |

| Coss    | Output Capacity           |     | 130 |     |      |                                                           |

| Crss    | Reverse Transfer Capacity |     | 17  |     | pF   | VDS=28 V, VGS=0 V                                         |

| Ciss    | Input Capacity            |     | 190 |     |      |                                                           |

| NF(2)   | Small Signal Noise Figure |     | 4   |     | dB   | f=175 MHz, V <sub>DS</sub> =28 \<br>I <sub>D</sub> =0.4 A |

Notes: (1) All devices 100% power tested in Siliconix test fixture No. RF28175 [80]

(2) Noise figure measured with 80 watt power matched source and load

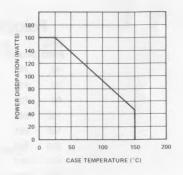

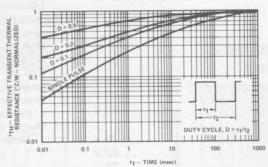

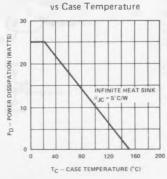

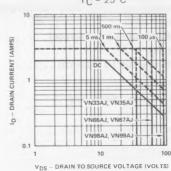

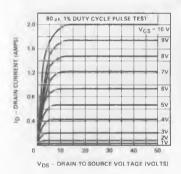

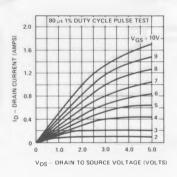

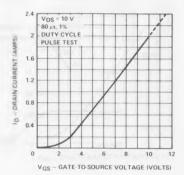

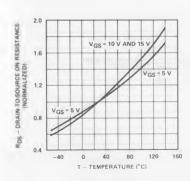

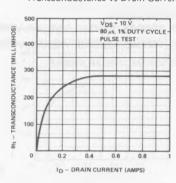

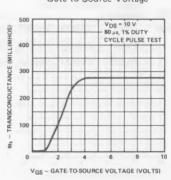

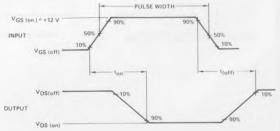

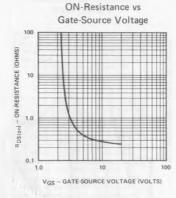

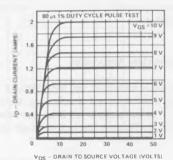

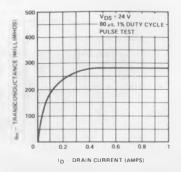

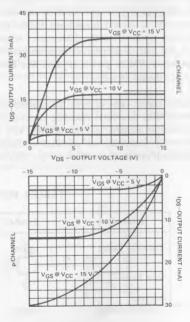

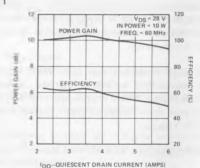

# Typical Performance Curves (25°C)

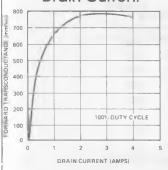

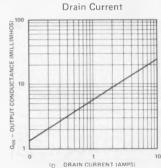

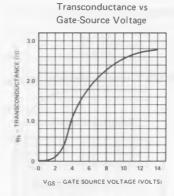

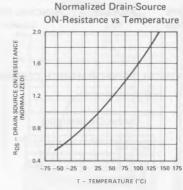

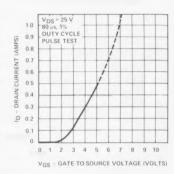

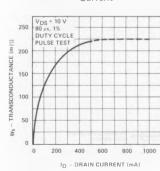

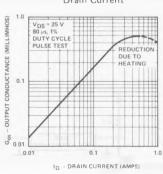

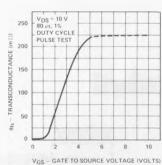

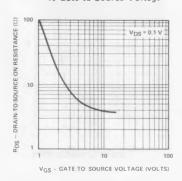

Transconductance vs Drain Current

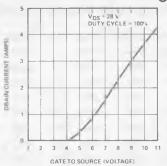

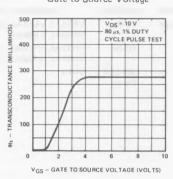

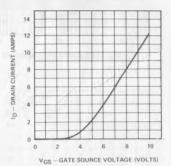

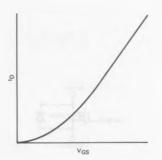

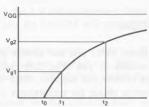

Drain Current vs Gate-to-Source Voltage

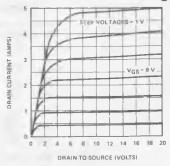

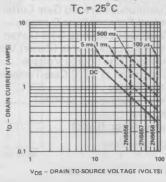

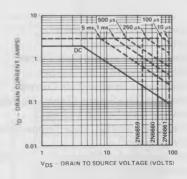

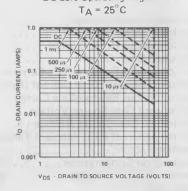

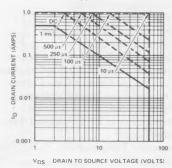

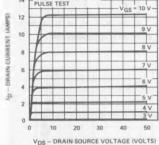

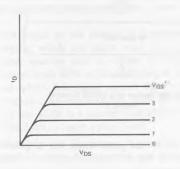

Output Characteristics vs Drain-to-Source Voltage

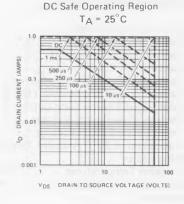

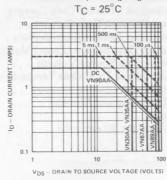

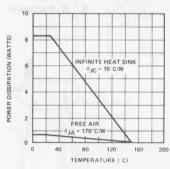

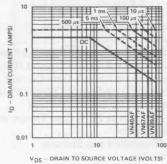

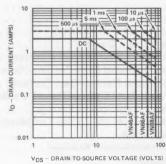

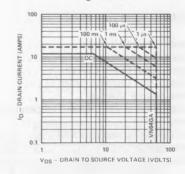

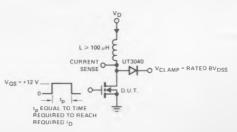

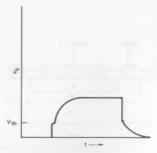

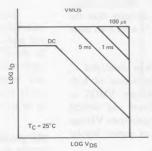

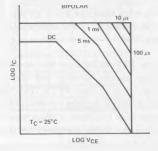

DC and Inductive Safe Operating Region TC=25°C

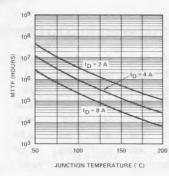

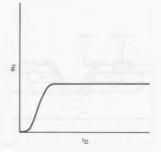

MTTF vs Temperature

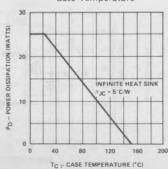

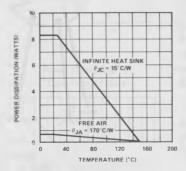

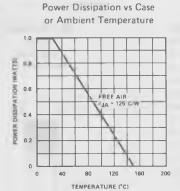

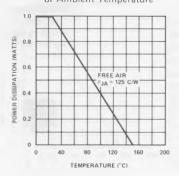

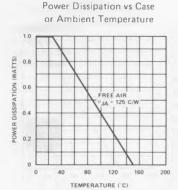

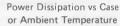

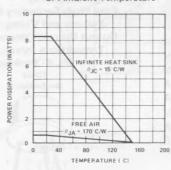

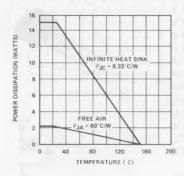

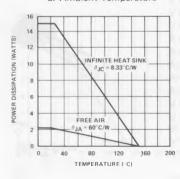

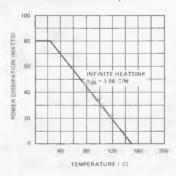

Power Dissipation vs Case Temperature

# Large Signal Series Input Impedance

| Frequency | R <sub>S</sub> (ohms) | X <sub>S</sub> (ohms) |

|-----------|-----------------------|-----------------------|

| 100       | 0.6                   | -6.8                  |

| 110       | 0.9                   | -6.0                  |

| 120       | 1.0                   | -5.3                  |

| 130       | 1.0                   | -5.2                  |

| 140       | 1.2                   | -4.8                  |

| 150       | 1.2                   | -4.4                  |

| 160       | 1.3                   | -4.0                  |

| 170       | 1.3                   | -3.7                  |

| 180       | 1.2                   | -3.4                  |

| 190       | 1.2                   | -2.8                  |

| 200       | 1.0                   | -2.6                  |

|           |                       |                       |

Conditions:  $R_L = 5.5 \ \Omega$   $V_{DS} = 28 \ \text{Volts}$   $I_{DQ} = 1.0 \ \text{Amps}$   $P_{IN} = 10 \ \text{Watts}$

# Small Signal 2-Port Parameters

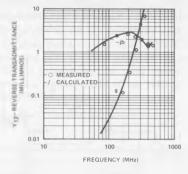

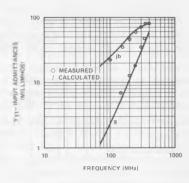

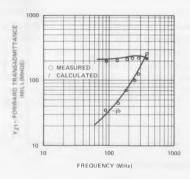

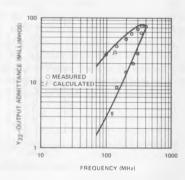

#### 2-Port Y-Parameter Matrix in Millimhos

| Freq  | Y4    | 1      | Y21    |       | Y-    | 12    | Y22   |       |  |

|-------|-------|--------|--------|-------|-------|-------|-------|-------|--|

| (MHz) | (Real | lmag)  | (Real  | lmag) | (Real | Imag) | (Real | lmag) |  |

| 10    | 0     | 10.5   | 886    | -47.5 | 0     | -1.03 | 4.42  | 8.34  |  |

| 20    | 0.897 | 21.3   | 881    | -37.5 | 0     | -2.05 | 5.31  | 15.9  |  |

| 50    | 6.52  | 58.3   | 902    | -106  | .5    | -5.65 | 7.61  | 42.5  |  |

| 100   | 20.1  | 128    | 1060   | -294  | 2.13  | -11.9 | 11.0  | 89.3  |  |

| 150   | 57.0  | 207    | 1220   | -565  | 6.63  | -19.8 | 21.4  | 134   |  |

| 200   | 125   | 322    | 1450   | -964  | 12.8  | -33.4 | 23.1  | 191   |  |

| 250   | 241   | 340    | 1230   | -1.61 | 32.5  | -48.7 | 14.9  | 226   |  |

| 300   | 520   | 219    | 215.5  | -2.4  | 33.6  | -96.9 | -76.3 | 371   |  |

| 350   | 565   | 124    | -243.2 | -2.02 | 43.5  | -123  | -66.1 | 417   |  |

| 400   | 574   | 4.06   | -695.7 | -1.72 | 37.1  | -166  | -59.3 | 551   |  |

| 450   | 509   | - 35.6 | -812.7 | -1.35 | 30.2  | - 198 | -17.0 | 644   |  |

| 500   | 477   | -11.6  | -800.4 | -1.27 | 43.7  | -258  | -13.8 | 749   |  |

|       |       |        |        |       |       |       |       |       |  |

Conditions: 28 V, 1.6 A

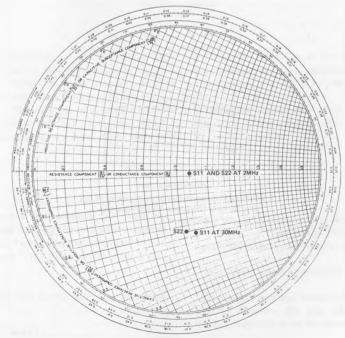

#### Polar S-Parameters in 50.0 Ohm System

| Freq  | S <sub>4</sub> | 14    | S     | 24    | S <sub>12</sub> |        | S <sub>22</sub> |        |

|-------|----------------|-------|-------|-------|-----------------|--------|-----------------|--------|

| (MHz) | (Magn          | Angl) | (Magn | Angl) | (Magn           | Angi)  | (Magn           | Angl)  |

| 10    | _798           | -134  | 25.1  | 106   | .00             | 18.4   | .691            | -141   |

| 20    | .819           | -154  | 13.1  | 91.8  | .03             | 6.42   | .819            | -157   |

| 50    | .839           | -168  | 4.51  | 71.8  | .03             | -6.34  | .766            | -166   |

| 100   | .884           | -173  | 1.95  | 51.1  | .02             | -13.2  | .835            | -169   |

| 150   | .921           | -175° | 1.04  | 40.4° | .016            | -6.22° | .888            | -172 ° |

| 200   | .943           | -177° | .629  | 34.2° | .013            | -1.27° | .917            | -174°  |

| 250   | .953           | -179° | .436  | 28.3° | .013            | 24.5°  | .939            | -175°  |

| 300   | .959           | 178°  | .309  | 26.4° | .013            | 40.4°  | .950            | -176°  |

| 350   | .962           | 178°  | .234  | 24.4° | .015            | 50.7°  | .954            | -176°  |

| 400   | .966           | 177°  | .187  | 24.3° | .017            | 58.8°  | .957            | -177°  |

| 450   | .963           | 176°  | .157  | 25.9° | .020            | 65.5°  | .958            | -178°  |

| 500   | .966           | 176°  | .138  | 27.2° | .029            | 69.0°  | .962            | -178°  |

|       |                |       |       |       |                 |        |                 |        |

Conditions: 28 V. 1.6 A

**CAUTION: Beryllium Oxide** — The top cap of this device is alumina which is harmless. However the ceramic portion between the leads and the metal flange is Beryllium Oxide Ceramic, the dust of which is toxic. Care must therefore be taken during handling and mounting the device to prevent any damage to this area.

Steps must be taken to ensure that all those who may handle, use, or dispose of this device are aware of its nature and of these necessary safety precautions. In particular the transistor should never be thrown out with general industrial or domestic waste.

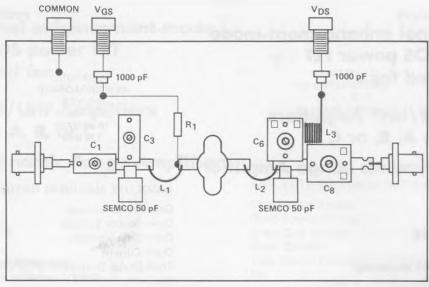

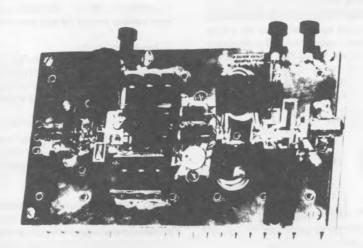

# **Test Fixture**

#### 175 MHz Test Fixture

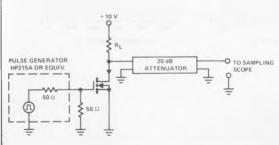

Scale: 3/4 of original size

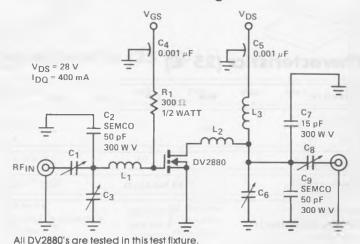

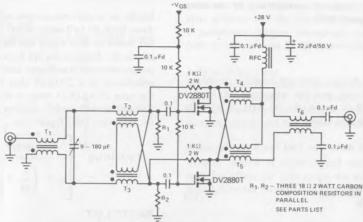

#### 175 MHz DV2880 Schematic Diagram

#### **Parts List**

C<sub>1</sub>, C<sub>3</sub>, 4 to 40 pF ARCO #422 trimmer capacitors

C6, C8, 9 to 180 pF ARCO #463 trimmer capacitors

L<sub>1</sub>, 1 3/16" length of #12 AWG (loop 1/2")

L2, 1" length of #12 (loop 0.4")

L3,8 turns #18 AWG enamel on 1/4" diameter, close wound

$R_1$ , 10 K $\Omega$  1/4 watt carbon resistor

**Preliminary**

n-channel enhancement-mode RF VMOS power FET designed for...

HF/VHF/UHF Amplifiers Class A, B, or C

**Benefits**

No Thermal Runaway

Low Noise Figure High Dynamic Range

Simple Bias Circuitry

Withstands Infinite VSWR

Class A, B, or C Operation

**High Dynamic Range Amplifier**

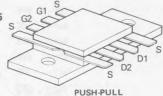

107-1

PUSH-PULL 40 W BROADBAND DRIVER

> 28 V - 35 V 10 dB GAIN

> > 175 MHz

#### ABSOLUTE MAXIMUM RATINGS (25°C)

Gate-Source Voltage 40 V Drain-Source Voltage 80 V Drain-Gate Voltage 80 V Drain Current 4 A Total Device Dissipation @  $25^{\circ}$  Case  $\theta$  jc  $2.2^{\circ}$  C/W Storage Temperature  $-65^{\circ}$  C to  $150^{\circ}$  C Max Junction Temp.  $+200^{\circ}$  C

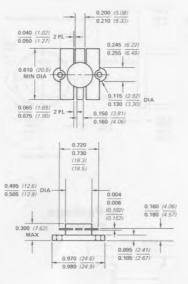

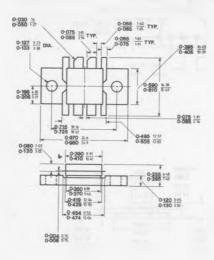

V-Package see Section 5

## Electrical Characteristics (25°C)

| SYMBOL               | CHARACTERISTIC            | MIN | TYP           | MAX | UNIT | TEST CONDITIONS                                            |

|----------------------|---------------------------|-----|---------------|-----|------|------------------------------------------------------------|

| P <sub>OUT</sub> (1) | POWER OUTPUT              | 40  |               |     | w    | V <sub>DD</sub> =28 V <sub>1DQ</sub> = 0.2 A               |

| 001                  |                           |     |               |     |      | P <sub>IN</sub> = 4 W Max, F= 175 MHz                      |

| $\eta^{(1)}$         | DRAIN EFFICIENCY          | 60  |               |     | %    |                                                            |

| gm (2)               | TRANSCONDUCTANCE          |     | 0.5 PARALLEL  |     | Mho  | V <sub>DS</sub> =28 V, I <sub>D</sub> = 2A                 |

| Coss                 | OUTPUT CAPACITY           |     | 28 (Per Side) |     |      |                                                            |

| C <sub>755</sub>     | REVERSE TRANSFER CAPACITY |     | 4 (Per Side)  |     | pF   | V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0 V              |

| Ciss                 | INPUT CAPACITY            |     | 35 (Per Side) |     |      |                                                            |

| NF <sup>(3)</sup>    | SMALL SIGNAL NOISE FIGURE |     | 7.0           |     | dB   | V <sub>DS</sub> =28 V<br>I <sub>D</sub> =0.2 A F = 100 MHz |

©1980 Siliconix incorporated

#### NOTES

- (1) All devices 100% power tested in Siliconix test fixture No. RF 28175 [PP1].

- (2) Measured under pulsed condition with pulse width 300 µsec > 5% duty cycle

- (3) Noise figure measured with 40 Watt power matched source and load.

**Preliminary**

n-channel enhancement-mode RF VMOS power FET designed for...

HF/VHF/UHF Amplifiers Class A, B, or C

**High Dynamic Range Amplifier**

80 W BROADBAND 28 V – 35 V 10 dB GAIN 175 MHz

PUSH-PULL

#### ABSOLUTE MAXIMUM RATINGS (25°C)

| Gate-Source Voltage                 | 40 V      |

|-------------------------------------|-----------|

| Drain-Source Voltage                | 80 V      |

| Drain Gate Voltage                  | 80 V      |

| Drain Current                       | 8 A       |

| Total Device Dissipation @ 25° Case | 160 W     |

| $\theta$ jc                         | 1.1 °C/W  |

|                                     | to 150° C |

| Max Junction Temp.                  | +200°C    |

# V-Package see Section 5

#### PUSH-PULL

#### **Benefits**

No Thermal Runaway

Withstands Infinite VSWR

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

#### Electrical Characteristics (25°C)

| SYMBOL              | CHARACTERISTIC            | MIN | TYP            | MAX | UNIT | TEST CONDITIONS                                                      |

|---------------------|---------------------------|-----|----------------|-----|------|----------------------------------------------------------------------|

| POUT <sup>(1)</sup> | POWER OUTPUT              | 80  |                |     | W    | V <sub>DD</sub> 28 V, I <sub>DQ</sub> 04 A                           |

| 001117              |                           | 00  |                |     | **   | P <sub>IN</sub> = 8 W Max, F= 175 MHz                                |

| η (1)               | DRAIN EFFICIENCY          | 60  |                |     | %    |                                                                      |

| gm (2)              | TRANSCONDUCTANCE          | 1   | .0 PARALLEL    |     | Mho  | V <sub>DS</sub> =28 V <sub>-</sub> I <sub>D</sub> = 4 A              |

| Coss                | OUTPUT CAPACITY           |     | 55 (Per Side)  |     |      |                                                                      |

| Crss                | REVERSE TRANSFER CAPACITY |     | 8.0 (Per Side) |     | pF   | V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0 V                        |

| C <sub>ISS</sub>    | INPUT CAPACITY            |     | 70 (Per Side)  |     |      | 20                                                                   |

| NF <sup>(3)</sup>   | SMALL SIGNAL NOISE FIGURE |     | 7.5            |     | dB   | V <sub>DS</sub> <sup>-28</sup> V<br>I <sub>D</sub> 0.4 A F = 100 MHz |

©1980 Siliconix incorporated

#### NOTES

- (1) All devices 100% power tested in Siliconix test fixture No. RF 28175 [PP2].

- (2) Measured under pulsed condition with pulse width 300 μsec > 5% duty cycle.

- (3) Noise figure measured with 80 Watt power matched source and load.

6

**Preliminary**

n-channel enhancement-mode RF VMOS power FET designed for...

HF/VHF/UHF Amplifiers Class A, B, or C

**High Dynamic Range Amplifier**

PUSH-PULL 120 W BROADBAND 28 V – 35 V 10 dB GAIN 175 MHz

#### **Benefits**

No Thermal Runaway

Withstands Infinite VSWR

Class A, B, or C Operation

Low Noise Figure

High Dynamic Range

Simple Bias Circuitry

#### ABSOLUTE MAXIMUM RATINGS (25°C)

| Gate-Source Voltage                 | 40 V     |

|-------------------------------------|----------|

| Drain-Source Voltage                | 80 V     |

| Drain-Gate Voltage                  | 80 V     |

| Drain Current                       | 12 A     |

| Total Device Dissipation @ 25° Case | 240 W    |

| $\theta$ jc                         | .73° C/W |

| Storage Temperature -65°C           | to 150°C |

| Max Junction Temp.                  | +200°C   |

|                                     |          |

PUSH-PULL

# Electrical Characteristics (25°C)

| SYMBOL               | CHARACTERISTIC            | MIN | TYP            | MAX | UNIT | TEST CONDITIONS                                             |

|----------------------|---------------------------|-----|----------------|-----|------|-------------------------------------------------------------|

| P <sub>OUT</sub> (1) | POWER OUTPUT              | 120 |                |     | W    | V <sub>DD</sub> = 28V, I <sub>DQ</sub> = 0.6 A              |

| OUT                  | , GWEN GOTT GT            | 120 |                |     | **   | P <sub>IN</sub> = 12 W Max, F = 175 MH.                     |

| η (1)                | DRAIN EFFICIENCY          | 60  |                |     | %    |                                                             |

| gm(2)                | TRANSCONDUCTANCE          |     | 1.5 PARALLEL   |     | Mho  | V <sub>DS</sub> = 28 V, I <sub>D</sub> = 6 A                |

| Coss                 | OUTPUT CAPACITY           |     | 85 (Per Side)  |     |      |                                                             |

| Crss                 | REVERSE TRANSFER CAPACITY |     | 12 (Per Side)  |     | ρF   | V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0 V               |

| Ciss                 | INPUT CAPACITY            |     | 105 (Per Side) |     |      | 55                                                          |

| NF (3)               | SMALL SIGNAL NOISE FIGURE |     | 8.5            |     | dB   | V <sub>DS</sub> =28 V<br>I <sub>D</sub> = 0.6 A F = 100 MHz |

|                      |                           |     |                |     |      | ©1980 Siliconlx Incorporated                                |

#### NOTES:

- (1) All devices 100% power tested in Siliconix test fixture No. RF 28175 [PP3]

- (2) Measured under pulsed condition with pulse width 300  $\mu sec > 5\%$  duty cycle.

- (3) Noise figure measured with 120 Watt power matched source and load.

# Siliconix

# n-channel enhancement-mode **VMOS Power FETs** designed for .

- **VHF Broadband Amplifiers**

- **Receiver Front Ends**

- Class B, C, D, E Amplifiers

- Power Oscillators

#### ABSOLUTE MAXIMUM RATINGS

| Maximum Drain-Source Voltage                        |

|-----------------------------------------------------|

| Maximum Drain-Gate Voltage60 V                      |

| Maximum Gate-Source Voltage                         |

| Maximum Continuous Drain Current 2.0 A              |

| Maximum Dissipation at 25°C Case Temperature 25 W   |

| Linear Derating Factor (Derate from 25°C) 200 mW/°C |

| Temperature (Operating and Storage) –55 to +150°C   |

#### BENEFITS

- Reduces Component Count and Design Time/Effort Withstands Any VSWR High Gain, 10 dB Min @ 200 MHz High Two-Tone Intermodulation Intercept Point Low Small Signal Noise Figure **Linear Transfer Characteristics**

- Permits Broadband Designs High Input Impedance Low Noise Figure

- Permits Efficient Switching Amplifier Designs High Input Impedance No Storage Delay Time Rise and Fall Time Typically 4 nsec

- Improves Reliability Free From Secondary Breakdown Failures and Voltage Derating **Output Current Decreases as** Temperature Increases

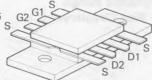

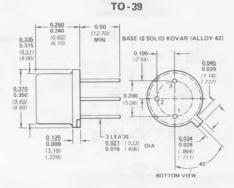

#### S-Package

380-SOE Flange See Section 5

#### ELECTRICAL CHARACTERISTICS (25°C unless otherwise noted)

|   |        | Characteristic                    | Min                                                                                                                                                                                                                                                          | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

|---|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| S | BVDSS  | Drain-Source Breakdown            | 60                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>GS</sub> = 0, I <sub>D</sub> = 10 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |

| Т | ID(on) | ON-State Drain Current (Note 1)   | 300                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                   |

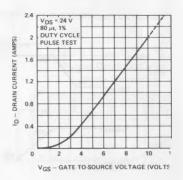

|   | 9fs    | Forward Transconductance (Note 1) | 170                                                                                                                                                                                                                                                          | 240                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mΰ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DS</sub> = 24 V, I <sub>D</sub> = 0.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                   |

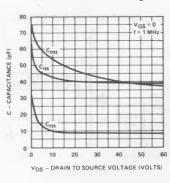

|   | Coss   | Common-Source Output Capacitance  |                                                                                                                                                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

| D | Ciss   | Common-Source Input Capacitance   |                                                                                                                                                                                                                                                              | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ρF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VGS = 0, VDS = 25, f = 1 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (Note 2                                                           |

| N | Crss   | Reverse Transfer Capacitance      |                                                                                                                                                                                                                                                              | 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | THOLE E                                                           |

|   | Gps    | Common-Source Power Gain          | 10                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DS</sub> = 24 V, I <sub>D</sub> = 0.2 A, f = 200 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |

|   | NF     | Small Signal Spot Noise Figure    |                                                                                                                                                                                                                                                              | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ub ub                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DS</sub> = 24 V, I <sub>D</sub> = 0.2 A, f = 150 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |

|   | T      | T ID(on)  9fs Coss Ciss Crss Gps  | S BVDSS Drain-Source Breakdown T ID(on) ON-State Drain Current (Note 1)  9ts Forward Transconductance (Note 1) Coss Common-Source Output Capacitance C Ciss Common-Source Input Capacitance C Crss Reverse Transfer Capacitance Gps Common-Source Power Gain | S         BVDSS         Drain-Source Breakdown         60           T         ID(on)         ON-State Drain Current (Note 1)         300           9fs         Forward Transconductance (Note 1)         170           Coss         Common-Source Output Capacitance           Ciss         Common-Source Input Capacitance           N         Crss         Reverse Transfer Capacitance           Gps         Common-Source Power Gain         10 | S T         BVDSS         Drain-Source Breakdown         60           T         ID(on)         ON-State Drain Current (Note 1)         300           Bfs         Forward Transconductance (Note 1)         170         240           Coss         Common-Source Output Capacitance         34           Ciss         Common-Source Input Capacitance         32           N         Crss         Reverse Transfer Capacitance         4.8           Gps         Common-Source Power Gain         10 | S T         BVDSS         Drain-Source Breakdown         60           T         ID(on)         ON-State Drain Current (Note 1)         300           gfs         Forward Transconductance (Note 1)         170         240           Coss         Common-Source Output Capacitance         34         37           C ciss         Common-Source Input Capacitance         32         35           N Crss         Reverse Transfer Capacitance         4.8         6.5           Gps         Common-Source Power Gain         10 | S T         BVDSS         Drain-Source Breakdown         60         V           T         ID(on)         ON-State Drain Current (Note 1)         300         mA           Bfs         Forward Transconductance (Note 1)         170         240         m75           Coss         Common-Source Output Capacitance         34         37           D Ciss         Common-Source Input Capacitance         32         35         pF           N Crss         Reverse Transfer Capacitance         4.8         6.5           Gps         Common-Source Power Gain         10         dB | S   BVDSS   Drain-Source Breakdown   60   V   VGS = 0, ID = 10 µA |

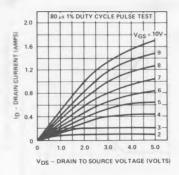

1. Pulse test - 80 µsec pulse, 1% duty cycle

2. Sample test.

VNAR

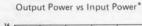

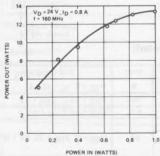

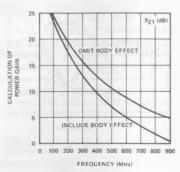

#### VMP4 PERFORMANCE CHARACTERISTICS

\*Conjugate input/output match

Saturated Output Power vs Frequency\*

PIN = 1 Watt, IDRAIN = 0.8 A

\*Conjugate input/output match

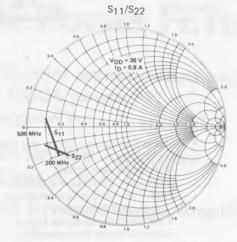

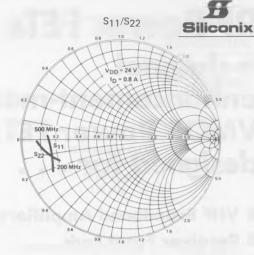

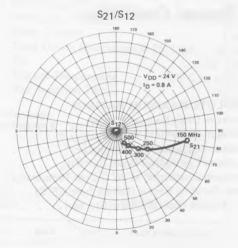

#### POLAR S-PARAMETERS IN 50.0 OHM SYSTEM

| FREQ.  | S     |       | S     |       | S <sub>1</sub> | -     | S     | 22    | S <sub>21</sub> |

|--------|-------|-------|-------|-------|----------------|-------|-------|-------|-----------------|

|        | (MAGN | ANGL) | (MAGN | ANGL) | (MAGN          | ANGL) | (MAGN | ANGL) | DB              |

| 1.00   | 1.00  | -4    | 26.07 | 177.0 | -48 dB         | 87.3  | 0.78  | -5    | 28.32           |

| 2.00   | 1.00  | -9    | 25.98 | 174.1 | 0.006          | 84.3  | 0.78  | -9    | 28.29           |

| 5.00   | 0.98  | -21   | 25.37 | 165.4 | 0.016          | 75.9  | 0.77  | -23   | 28.09           |

| 10.00  | 0.94  | -41   | 23.50 | 152.1 | 0.029          | 63.1  | 0.75  | -44   | 27.42           |

| 20.00  | 0.84  | -72   | 18.76 | 131.7 | 0.046          | 43.6  | 0.69  | -77   | 25.46           |

| 30.00  | 0.76  | -93   | 14.78 | 118.1 | 0.054          | 31.0  | 0.66  | -99   | 23.39           |

| 40.00  | 0.72  | -107  | 11.91 | 108.6 | 0.058          | 22.6  | 0.64  | -113  | 21.52           |

| 80.00  | 0.68  | -134  | 6.30  | 87.2  | 0.059          | 5.5   | 0.63  | -139  | 15.99           |

| 100.00 | 0.68  | -140  | 4.99  | 80.4  | 0.057          | 1.0   | 0.64  | -144  | 13.96           |

| 150.00 | 0.72  | -148  | 3.14  | 67.4  | 0.049          | -4.9  | 0.68  | -151  | 9.95            |

| 200.00 | 0.76  | -153  | 2.18  | 57.7  | 0.039          | -4.7  | 0.72  | -156  | 6.79            |

| 300.00 | 0.83  | -161  | 1.23  | 44.4  | 0.025          | 20.6  | 0.79  | -162  | 1.79            |

| 400.00 | 0.88  | -166  | 0.78  | 36.5  | 0.030          | 62.0  | 0.83  | -167  | -2.10           |

|        |       |       |       |       |                |       |       |       |                 |

#### TWO-PORT Y-PARAMETER MATRIX IN MILLIMHOS

| FREQ  | γ.    | 11    | Y      | 21      | Υ-    | 12    | Υ:    | 22    |

|-------|-------|-------|--------|---------|-------|-------|-------|-------|

| FREQ  | (REAL | IMAG) | (REAL  | IMAG)   | (REAL |       | (REAL | IMAG) |

| 1.0   | 0.00  | 0.28  | 293.40 | -0.58   | 0.00  | -0.04 | 2.49  | 0.28  |

| 2.0   | 0.00  | 0.56  | 293.40 | - 1.16  | -0.00 | -0.07 | 2.49  | 0.56  |

| 5.0   | 0.01  | 1.41  | 293.40 | -2.89   | -0.00 | -0.18 | 2.50  | 1.41  |

| 10.0  | 0.03  | 2.81  | 293.38 | -5.79   | -0.00 | -0.36 | 2.53  | 2.81  |

| 20.0  | 0.14  | 5.62  | 293.32 | -11.58  | -0.00 | -0.72 | 2.67  | 5.62  |

| 30.0  | 0.31  | 8.43  | 293.23 | -17.38  | -0.01 | -1.07 | 2.89  | 8.43  |

| 40.0  | 0.54  | 11.23 | 293.09 | -23.20  | -0.01 | -1.42 | 3.21  | 11.22 |

| 80.0  | 2.17  | 22.39 | 292.11 | -46.66  | -0.04 | 2.76  | 5.39  | 22.24 |

| 100.0 | 3.41  | 27.92 | 291.33 | -58.57  | -0.04 | -3.37 | 7.03  | 27.60 |

| 150.0 | 7.74  | 41.47 | 288.30 | -89.10  | 0.04  | -4.66 | 12.69 | 40.36 |

| 200.0 | 13.93 | 54.43 | 283.21 | -120.95 | 0.43  | -5.49 | 20.51 | 51.73 |

| 300.0 | 31.89 | 76.96 | 263.22 | -188.63 | 3.36  | -5.68 | 41.54 | 67.76 |

| 400.0 | 55.71 | 91.32 | 223.27 | -256.91 | 11.91 | -5.18 | 64.78 | 70.47 |

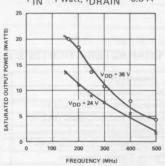

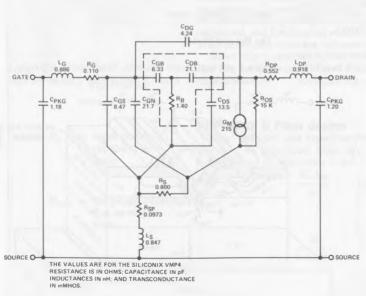

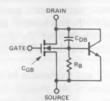

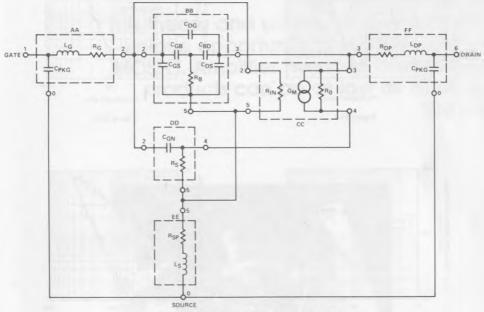

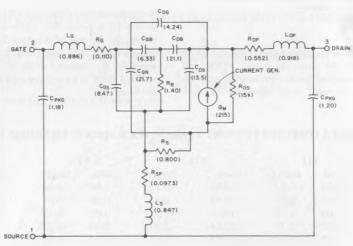

#### VMP4 Equivalent Circuit

#### VMP4 PERFORMANCE CHARACTERISTICS (Cont'd)

0.047<sub>p</sub>F\* 100 11

100 11

100 12

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100 11

100

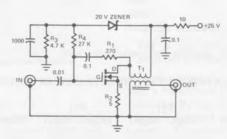

Quadrature Amplifier

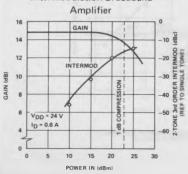

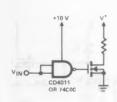

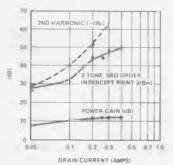

Gain & 2-Tone 3rd Order Intermodulation Quadrature (100-160 MHz) Amplifier 14 GAIN 12 INTER 10 GAIN V<sub>DD</sub> = 25 V I<sub>D</sub> = 1.2 A 4 5 15 20 25 30 POWER IN (dBm)

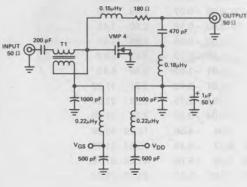

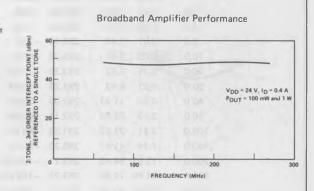

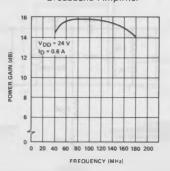

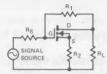

Broadband Amplifier

+VGS O-

T1 4T #22 AWG TWISTED PAIR ON INDIANA GENERAL F625 8Q2

Gain and 2-Tone 3rd Order Intermodulation Broadband

Broadband Amplifier

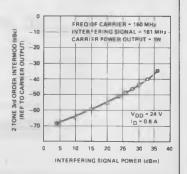

Effects of Interference

# n-channel enhancement-mode **VMOS Power FETs** designed for .

**Performance Curves VNAZ** See Section 3

- **High Speed Switching**

- **CMOS to High Current Interface**

- **TTL to High Current Interface**

- **High Frequency Linear Amplifiers**

- Line Drivers

- DC to DC Converters

- **Switching Power Supplies**

#### ABSOLUTE MAXIMUM RATINGS

| *Maximum Drain-Source Voltage                 |         |

|-----------------------------------------------|---------|

| 2N6656                                        | 35 V    |

| 2N6657                                        | 60 V    |

| 2N6658                                        |         |

| *Maximum Drain-Gate Voltage                   |         |

| 2N6656                                        | 35 V    |

| 2N6657                                        | 60 V    |

| 2N6658                                        | 90 V    |

| *Maximum Continuous Drain Current             | . 2.0 A |

| Maximum Pulsed Drain Current (Note 1)         | . 3.0 A |

| *Maximum Continuous Forward Gate Current      | 2.0 mA  |

| *Maximum Pulsed Forward Gate Current 1        | 00 mA   |

| *Maximum Continuous Reverse Gate Current 1    | 00 mA   |

| *Maximum Forward Gate-Source (Zener) Voltage  | 15 V    |

| *Maximum Reverse Gate-Source Voltage          | -0.3 V  |

| *Maximum Dissipation at 25°C Case Temperature | 25 W    |

| *Linear Derating Factor 200 i                 | mW/°C   |

| *Temperature (Operating and Storage)55 to +   | ⊦150°C  |

| *Lead Temperature                             |         |

| (1/16" from case for 10 sec)                  | .300°C  |

| #L-d' IEDEOid d                               |         |

#### BENEFITS

- Directly Interfaces to CMOS. TTL. **DTL** and MOS Logic Families Low Drive Current (IGSS < 100 nA) Threshold Voltage 0.8 to 2.0 V

- Permits More Efficient and Compact Switching Designs Typical Ton and Toff < 5 nsec

- Reduces Component Count and Design Time/Effort **Drives Inductive Loads Directly** Fan Out From a CMOS Logic Gate > 100

Easily Paralleled with Inherent Current Sharing Capability High Gain

Improves Reliability Free From Secondary Breakdown Failures and Voltage Derating **Output Current Decreases as** Temperature Increases Input Protected From Static Discharge

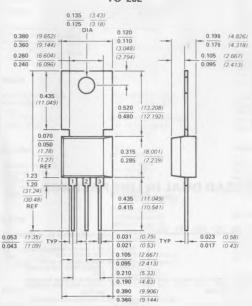

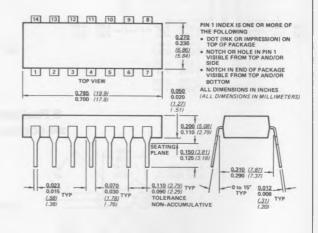

A-, J- Package

TO-3 See Section 5

1. Pulse test - 80 μsec pulse, 1% duty cycle.

<sup>\*</sup>Indicates JEDEC registered data

#### ELECTRICAL CHARACTERISTICS (25°C unless otherwise noted)

|    |     |                     | Characteristic                                   |     | 2N6656 |     |     | 2N6657 |     |     | 2N6658 |     | Unit | Test Conditions                                                                    |

|----|-----|---------------------|--------------------------------------------------|-----|--------|-----|-----|--------|-----|-----|--------|-----|------|------------------------------------------------------------------------------------|

|    |     |                     | Characteristic                                   | Min | Тур    | Мах | Min | Тур    | Max | Mın | Тур    | Max | Omic | 1 est Cullations                                                                   |

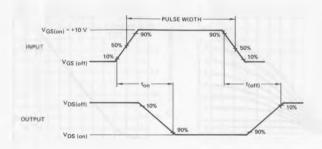

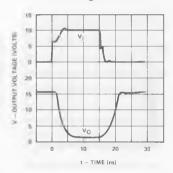

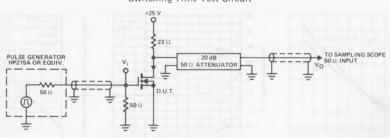

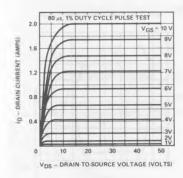

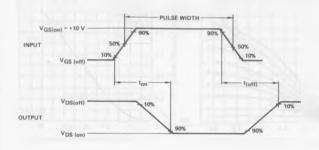

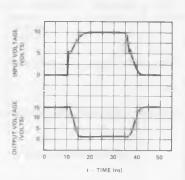

| 1  |     | BVDSS               | Drain-Source Breakdown                           | 35  |        |     | 60  |        |     | 90  |        |     |      | VGS 0.1D 10 µA                                                                     |