NUMÉRO 553 DECEMBRE 1993

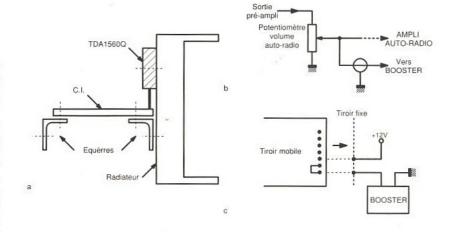

**BOOSTER 2X40W** A TDA 1560Q

## LA SYNTHÈSE DIGITALE DIRECTE

SUR PC **UN COMPRESSEUR -**LIMITEUR AUDIO

**DES TUBES**

**CARTE VOLTMÈTRE**

303330300 LA SIMULATION **AVEC ISPICE** T2438 - 553 - 24.00 F

## SOM Maire

**ELECTRONIQUE** APPLICATIONS

MENSUEL édité par PUBLICATIONS GEORGES VENTILLARD S.A. au Capital de 5 160 000 F 2 à 12, rue de Bellevue, 75019 PARIS Tél.: 42.00.33.05 - Fax: 42.41.89.40 Télex: 220409 F

Principaux Actionnaires:

- M. Jean-Pierre Ventillard

- Mme Paule Ventillard

Président-Directeur-Général,

Directeur de la Publication : Jean-Pierre VENTILLARD

Directeur de la Rédaction : Bernard FIGHIERA

> Rédacteur en Chef : Claude DUCROS

> Marketing/Ventes: Jean-Louis PARBOT Tél.: 42.00.33.05.

Création maquette : Rachid MARAI

Inspection des Ventes: Société PROMEVENTE - M. Michel IATCA 11, rue de Wattignies - 75012 PARIS. Tél.: 43.44.77.77 - Fax: 43.44.82.14.

### Publicité:

Société Auxiliaire de Publicité 70, rue Compans, 75019 PARIS Tél.: 42.00.33.05 C.C.P. PARIS 37 93 60

Directeur commercial : Jean-Pierre REITER Chef de publicité : Francine FIGHIERA Assistée de : Laurence BRESNU

Abonnement : Marie-Christine TOUSSAINT Voir notre tarif «spécial abonnement». Pour tout changement d'adresse, envoyer la dernière bande accompagnée de 2,80 F en timbres.

IMPORTANT: ne pas mentionner notre numéro de compte pour les paiements par chèque postal.

Electronique Radio Plans décline toute responsabilité quant aux opinions formulées dans les articles, celles-ci n'engageant que leurs auteurs. Les manuscrists publiés ou non ne sont pas retournés. «La loi du 11 mars 1957 n'autorisant aux termes des alinéas 2 et 3 de l'article 41, d'une part que «copies ou reproductions strictement réservées à l'usage privé du copiste et non destinées à une utilisation collective» et d'autre part, que les analyses et les courtes citations dans un but d'exemple et d'illustration, «toute représentation ou reproduction intégrale, ou partielle, faite sans le consentement de l'auteur ou de ses ayants-droit ou ayants-cause, est illicite» (alinéa premier de l'article 40). Cette représentation ou reproduction, par quelque procédé que ce soit, constituerait donc une contrefaçon sanctionnée par les articles 425 et suivants du Code Pénal».

Ce numéro a été tiré à 37 600 exemplaires

Dépôt légal décembre 93 - éditeur 1735

Mensuel paraissant en fin de mois.

Distribué par S.A.E.M. Transports-Presse

Photocomposition:

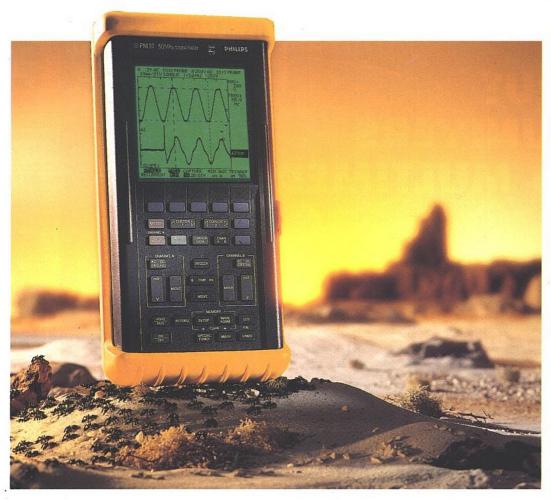

COMPOGRAPHIA - 75011 PARIS Photo de couverture: E. Malemanche.

Numéro 553 - Décembre 1993

ISSN 1144-5742

## **ETUDES ET CONCEPTION**

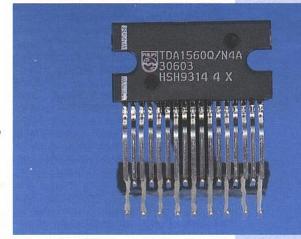

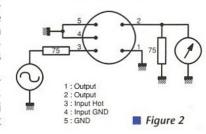

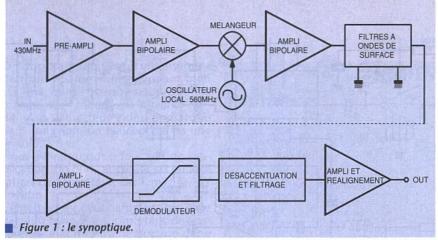

43 UN BOOSTER 2 X 40 W AVEC LE TDA 1560 Q. 50 RÉCEPTEUR FM VIDÉO 430 MHZ

## **REALISATION**

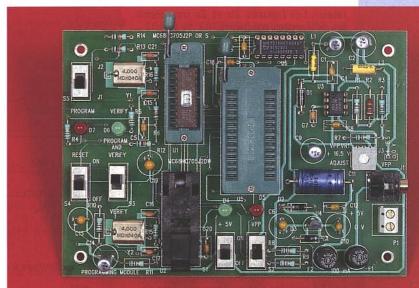

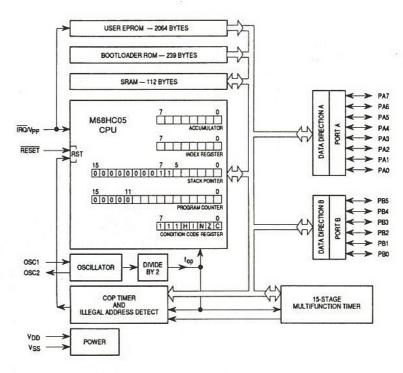

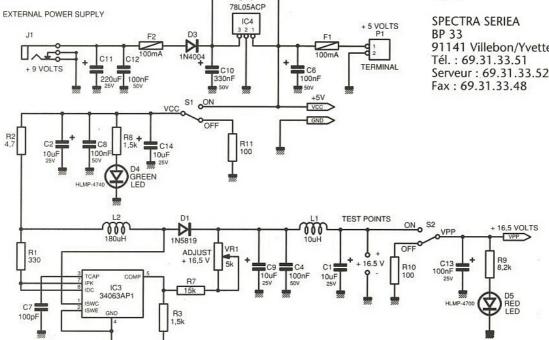

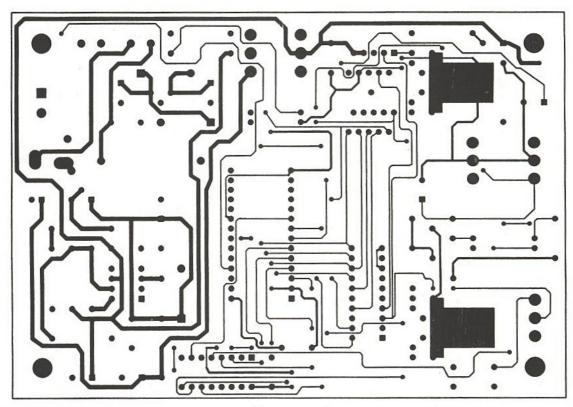

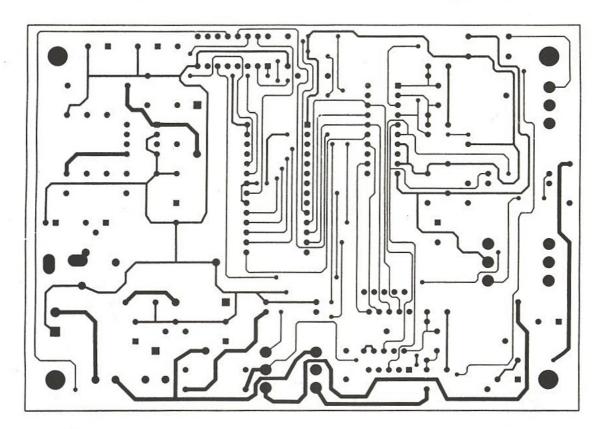

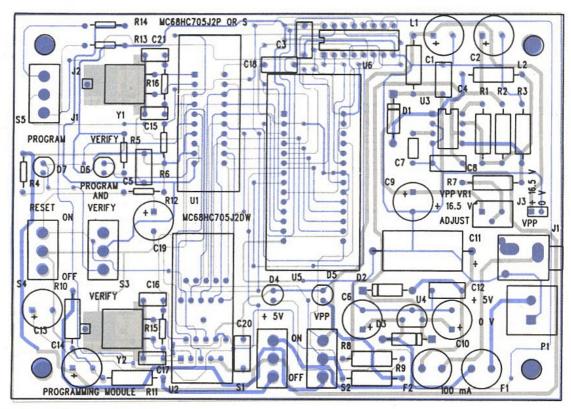

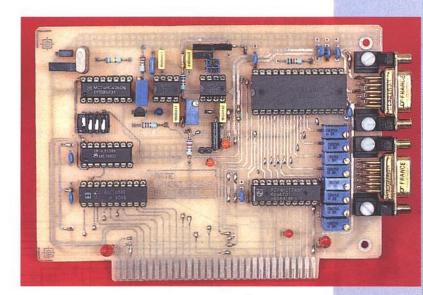

25 PROGRAMMATEUR DE 68 HC705 J2 39 CIRCUIT INTÉGRÉ POUR ONDULEUR DE TENSION 55 CARTE VOLTMÈTRE POUR PC 83 COMPRESSEUR-LIMITEUR L8TC

## **TECHNIQUE**

9 L'ACCESS-BUS : LE PROTOCOLE

## **MESURE ET INSTRUMENTATION**

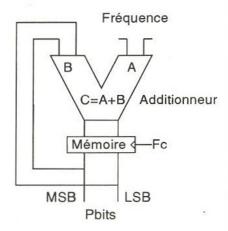

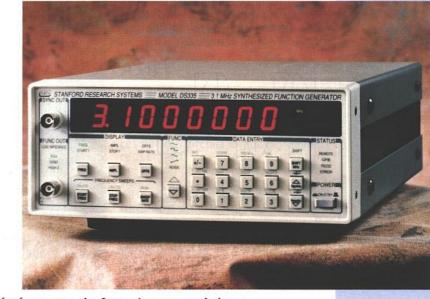

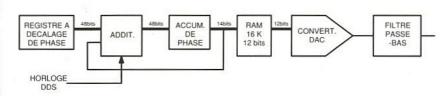

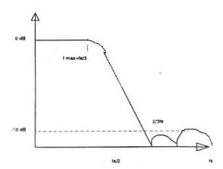

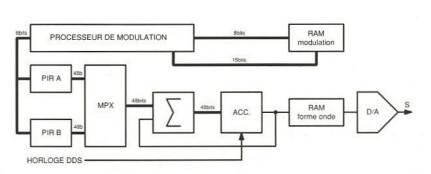

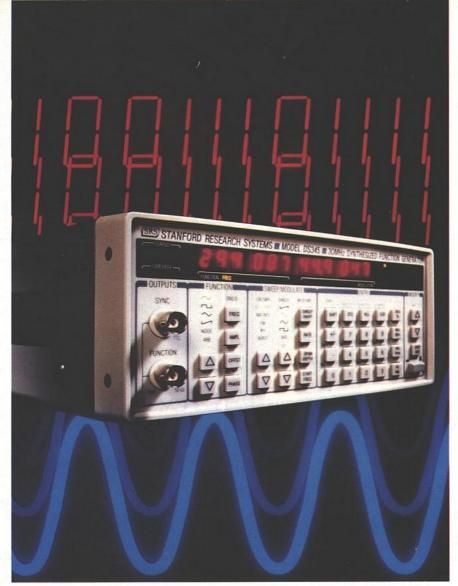

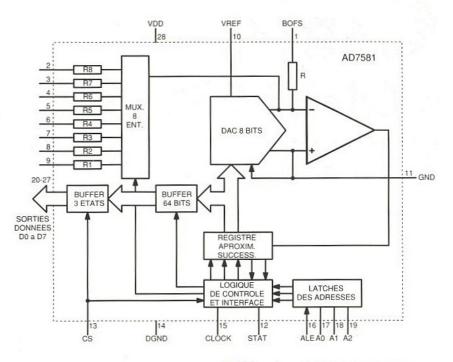

19 LA SYNTHÈSE DIGITALE DIRECTE ET LES GÉNÉRATEURS ARBITRAIRES

## CIRCUITS D'APPLICATION

63 LE JEU D'INSTRUCTIONS DES MICROCONTRÔLEURS RISC PIC 16CXX

## **COMPOSANTS ET TECHNOLOGIE**

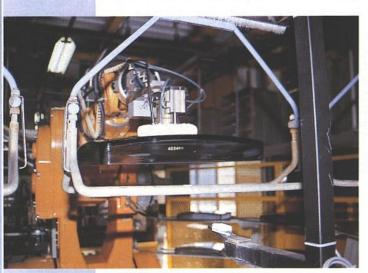

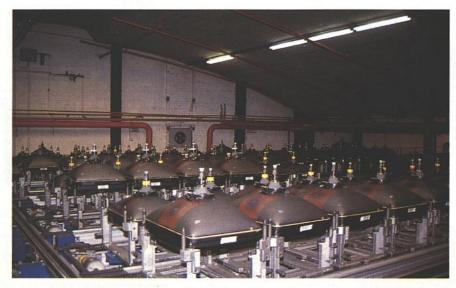

75 FABRICATION DES CATHOSCOPES COULEUR PHILIPS À DREUX

## C.D.A.O.

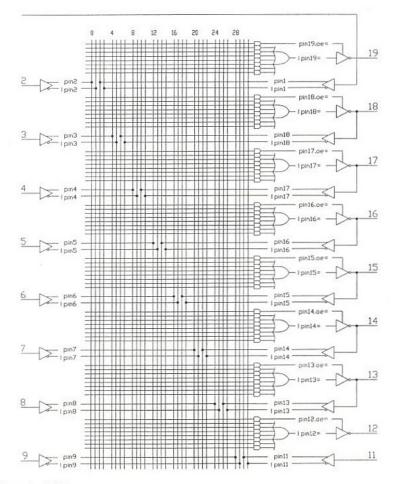

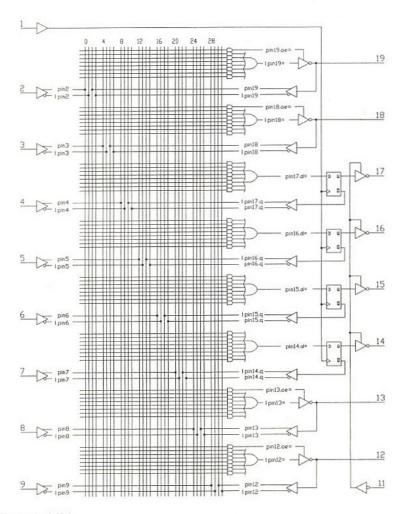

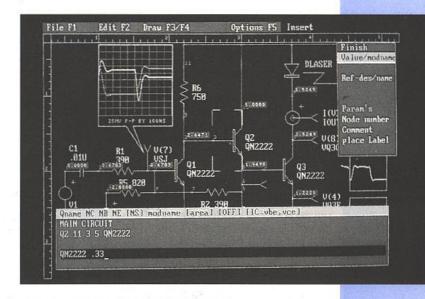

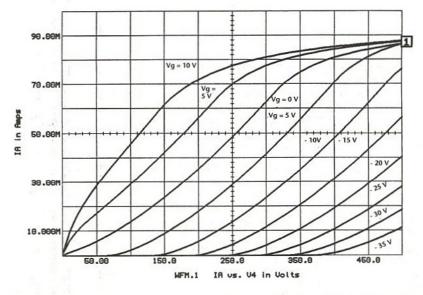

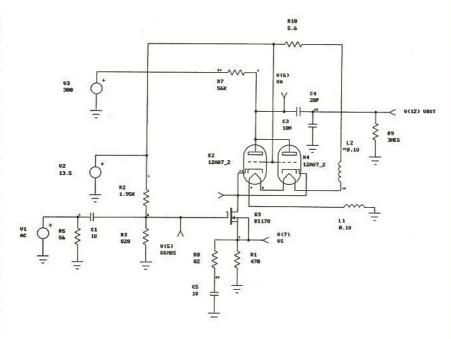

33 PROLOGIC : LE MODE D'EMPLOI 69 LA SIMULATION DES CIRCUITS À TUBES AVEC INTUSOFT SPICE

## COMMUNICATION

81 LE SEPT : DIX ANS DE CARTES À PUCE

## **IDEES ET METHODE**

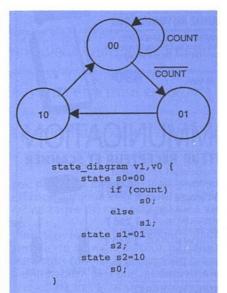

17 GÉNÉRATION DE SIGNAUX PÉRIODIQUES PAR MICROCONTRÔLEUR

## **INFOS**

90 LE HA5332 : DOUBLE SHA 100 ns HARRIS

INTERRUPTEURS MOS DE PUISSANCE ST SÉRIE VN

92 ACQUISITION DE DONNÉES PAR RECONNAISSANCE VOCALE : LE TALKMAN

EIF ET LE RANGEMENT INDUSTRIEL

DOUBLES DAC 12 BITS MX 7837/47

93 CARTES DE COMMUNICATION SÉRIE SELIA

CONDENSATEURS CÉRAMIQUE DE PUISSANCE AVX

IMPRIMANTES THERMIQUES INDUSTRIELLES AFEISA

96 L'EXTENSION DE BUS PC, PCFACE III

UNE LIBRAIRIE ÉTENDUE DE MODÈLES RF INTUSOFT

RENDEZ-VOUS EDUCATEC 93

Ont participé à ce numéro : J. Alary, R. de Bailliencourt, C. Basso, F. Broyde, F. de Dieuleveult, C. Djabian, A. Garrigou, P. Gueulle, J.-P. Jacquet, P. Oguic, Ch. Pannel, D. Paret.

## ACCESS.BUS: LE PROTOCOLE

Dans le précédent article (n° 551), nous

vous avons présenté le concept

ACCESS.bus. Ce concept repose sur la

«couche physique» du bus I2C et ne

demande donc aucune autre

connaissance électronique que celle

que vous connaissez bien au travers des

nombreux articles que ERP a déjà publiés.

Se reposant électriquement sur le bus I2C, aucun composant spécifique

ACCESS. bus n'a été développé, pour la bonne et unique raison que tous ceux

qui sont I2C conviennent et fonctionnent parfaitement.

La spécificité du protocole ACCESS. bus réside dans le fait qu'il est plus orienté

vers la communication entre un mini-ordinateur (ou une grosse CPU) et des

éléments périphériques interactifs.

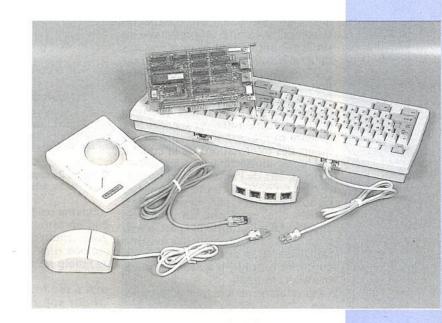

Comme vous avez pu le remarquer sur les photos déjà présentées, de nombreux ACCESSoires compatibles à ce bus sont déjà commercialisés aux États-Unis.

Notre but, au sein de cette revue, n'est pas de vous vanter ces équipements mais de vous indiquer comment faire en sorte que tous les équipements que vous avez déjà réalisés «compatibles I2C» puissent, en plus, devenir un jour un «périphérique interactif» sans toucher au hardware mais en implémentant des couches logicielles de plus haut niveau au cœur de la CPU.

Passons au thème que nous allons aborder aujourd'hui et que nous avons défloré lors du précédent numéro (551). Il s'agit de pénétrer plus en profondeur dans la structure du protocole de l'ACCESS. bus. Nous terminerons cette série le mois prochain avec des exemples de réalisations matérielles en décrivant les composants (I2C), les plus fréquemment rencontrés dans des réalisations industrielles de l'ACCESS.

## **LE CONTENANT**

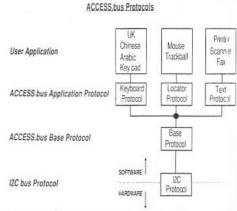

Effectuons le grand plongeon ! L'architecture générale du protocole est donnée figure 1.

Avant de rentrer dans le plus petit détail et les commentaires associés à chacune des parties représentées sur cette figure, rappelons que tout système de communication bien conçu se plie aux fameuses couches ISO/OSI (Open System Interconnexion/International Standard Organisation) et que, comme un enfant bien sage, l'AC-CESS.bus s'y conforme.

Au nombre de sept, qui sont et que disent ces fameuses couches ? Bien souvent, les gens en parlent mais bien rares sont ceux capables d'en donner leur signification clairement.

Evidemment, nous pourrions passer totalement sous silence les relations qui existent entre les couches ISO/OSI et l'ACCESS.bus, mais alors vous éprouveriez sans doute une gêne au

Figure 1 : architecture du protocole.

moment de l'implémentation du protocole dans l'environnement PC, ne sachant plus très bien qui fait quoi ou qui doit faire quoi.

Aussi, sans considérer cela comme une punition suprême que vous ne méritez certainement pas et afin d'éviter tout

problème, il est préférable, pour une fois au moins, de bien savoir de quoi on parle.

La figure 2 vous indique les appellations ISO/OSI des différentes couches. Rappelons succinctement leurs fonctions.

Tout d'abord, sachez qu'il n'existe aucune hiérarchie entre les couches des différents niveaux et appartenant à un même système. En fait, chaque couche se comporte comme un prestataire de service indépendant et ne s'engage qu'avec la couche de même niveau du système avec laquelle elle est en relation.

De ce fait, dans chaque système mis en œuvre avec ce type d'architecture, chaque couche offre ses services à la couche qui lui est supérieure et requiert des informations de la couche qui lui est immédiatement inférieure. De plus, lors de l'implantation concrète dans un système, toutes les couches ne sont pas nécessairement utilisées. Mais sachez que, plus on utilise de couches, plus l'information passée sera sûre et le taux d'erreurs prévisible faible car il y aura alors plus de contrôles (et plus, bien sûr, le traitement sera lourd).

Faisons rapidement le tour du proprié-

## La couche physique n° 1

Elle assure le transport de l'information (c'est rare qu'elle n'y soit pas !). L'unité d'information utilisée dans

cette couche est le bit.

La couche fournit les procédures et les fonctions mécaniques, électriques, électroniques nécessaires pour établir, maintenir et libérer des connexions physiques entre les Équipements Terminaux de Traitement des Données (ETTD), les Équipements Terminaux de Circuits de Données (ETCD) et/ou les Centres de Communication de Données (CCD).

Comme nous le verrons plus loin, en ce qui concerne l'ACCESS.bus, une partie du protocole I2C remplit cette couche.

## La couche liaison n° 2

Elle est responsable de l'acheminement sans erreur de blocs d'informations sur des liaisons de données.

L'unité de base est la trame.

En effet, les supports de transmission introduisent des erreurs dans les informations transportées et le but de cette couche est d'assurer un taux d'erreurs résiduel négligeable. Différents moyens sont utilisés et utilisables pour effectuer ces contrôles. Citons par exemple les parités, le CRC (Cyclic Redundancy Code)..

Cette couche est divisée en deux souscouches:

- MAC (Medium Access Control).

- LLC (Logical Link Control).

Comme nous le verrons plus loin en ce qui concerne l'ACCESS.bus, une partie du protocole I2C remplit cette couche.

## OSI Model of ACCESS.bus Application

OSI = Open System Interconnection model

| OSI Model             | ACCESS.bus system |

|-----------------------|-------------------|

| 7: Application Layer  | PC / Workstation  |

| 6: Presentation Layer | PC / Workstation  |

| 5: Session Layer      | PC / Workstation  |

| 4: Transport Layer    | ACCESS.bus        |

| 3: Network Layer      | I2C / ACCESS.bus  |

| 2: Link Layer         | 12C               |

| 1: Physical Layer     | 12C               |

Figure 2 : appellation des différentes couches ISO.

## La couche réseau n° 3

Elle est responsable de l'acheminement des paquets de données qui transiteront à l'intérieur du système (par exemple d'un nœud à l'autre).

Un «routeur» est nécessaire. Un contrôle de flux est contenu dans cette couche pour éviter des pertes de données et éviter l'encombrement de certains chemins. Enfin, un adressage est nécessaire pour permettre l'acheminement des paquets.

Comme nous le verrons plus loin, en ce qui concerne l'ACCESS.bus, une partie du protocole I2C remplit cette couche ainsi qu'une partie du protocole spécifique ACCESS.bus.

## La couche transport n°4

Elle est responsable du contrôle du transport des informations de bout en bout au travers du réseau.

Cette couche doit assurer que les messages des utilisateurs connectés à un réseau sont correctement parvenus à leurs destinataires. Une qualité de service sera définie et devra être respectée. Une autre fonction de cette couche est de rassembler les messages qui ont été découpés en morceaux par commodité pour le transport.

Comme nous le verrons plus loin, en ce qui concerne l'ACCESS.bus, seule une partie du protocole spécifique AC-CESS.bus remplit cette couche.

Pratiquement, le protocole ACCESS.bus s'arrête à ce niveau de l'architecture OSI/ISO et les couches supérieures sont assurées par l'ensemble mini-ordinateur/ workstation.

Ce sont :

## La couche session

Elle est responsable de la mise en place et du contrôle du dialogue entre les tâches distantes.

Cette couche a pour but d'activer et de synchroniser certains événements. Les contrôles seront assurés par des mécanismes qui utilisent des jetons. Seule l'interface qui possède un jeton pourra assurer la fonction assurée par le jeton.

## La couche présentation

Elle est responsable de la présentation

des données échangées par les applications.

Elle assure la compatibilité entre tous les matériels raccordés au réseau. Elle s'occupe de la syntaxe des données.

## La couche application

Elle est responsable de la sémantique de l'information et complète la partie syntaxe prise en charge par la couche de présentation.

Et c'est tout... ouf! Mais c'était nécessaire pour que tous les points soient sur les «i»!

La figure 2 indique donc où sont affectées et remplies les différentes couches OSI/OSI dans le cas de l'AC-CESS.bus et en résumé, on peut dire

- les couches supérieures («session, présentation, application») sont direc-tement reliées à l'environnement logi-

ciel ou machine;

- la couche «transport» dépend directement du protocole ACCESS.bus, mais un protocole n'est rien si personne ne le transporte. Or, pour le transporter, il est nécessaire d'avoir un moyen de transport fiable, connu, économique, d'emploi facile, de sources multiples, pour trouver des composants utilisables, de nombreuses fonctionnalités, etc.

C'est donc pour ces nombreuses raisons qu'il a été choisi d'employer, pour les couches «réseau, liaison et physique», le mécanisme du protocole du Bus I2C sans en changer une ligne (ni de données : SDA, ni d'horloge : SCL). La figure 1 présente d'une façon plus concrète les séparations «hard»/«soft» ainsi que les zones dédiées à chaque partie.

La couche encore plus basse (et pas du tout ISO:OSI) est la partie matérielle

du réseau.

Avant de nous lancer dans la partie logicielle, commençons par le côté visible de l'iceberg que constitue la par-tie mécanique de l'ACCESS.bus.

## **SPÉCIFICATIONS** MATÉRIELLES

## Connecteurs et câblage de la

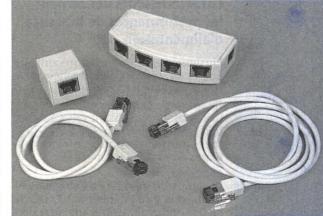

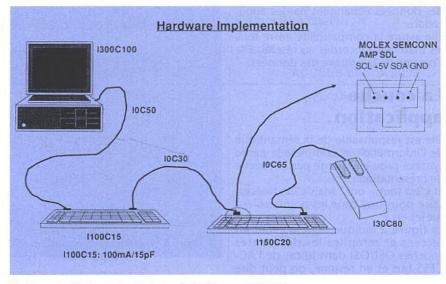

A ce jour, deux prises quasi similaires provenant de deux sociétés de réputation mondiale (il s'agit des sociétés Molex - Semconn - et AMP - SDL - ont été homologuées.

Ces prises possèdent un écran. La version de Molex n'a pas de verrou alors que celle de AMP en possède un, mais les deux sont compatibles.

Ces prises mâles et femelles, semblables aux prises téléphoniques, sont équipées de quatre fils, comme l'indique le figure 3.

Une seule prise est nécessaire par ordinateur.

On reconnaît les fils Serial DAta (SDA) et Serial CLock (SCL) du bus I2C, auShielded Male Modular Connector Modular Connector 4321 1 - GND - GND (Black) 2-SDA 2 - SDA (Green) 3 - +5V (Red) 4 - SCL (White) 3 - +5V

Positive locking, keyed, connector is slightly bigger than a phone plug. Double release instead of single. Supplied by AMP and Molex.

Figure 3 : la connectique normalisée ACCESS.bus

quel on a adjoint une masse et un plus

Remarque de l'auteur : bien entendu, en cas d'extensions externes de bus 12C de vos propres réalisations, nous vous recommandons de vous conformer à ce type de prise... c'est gratuit et on ne sait jamais!

Les ACCESSoires qui n'ont pas à être tenus dans la main, tels que souris, etc., devraient posséder deux prises femelles, de façon à pouvoir satisfaire le montage daisy chain.

Par contre, ceux qui doivent être tenus en main (souris, lecteur de barcode...)

CAO

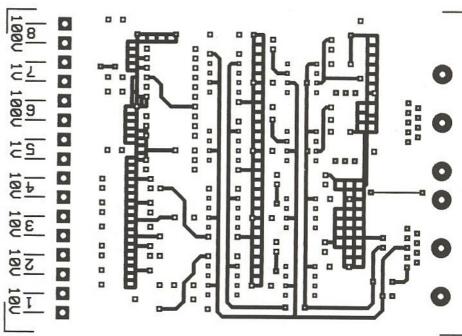

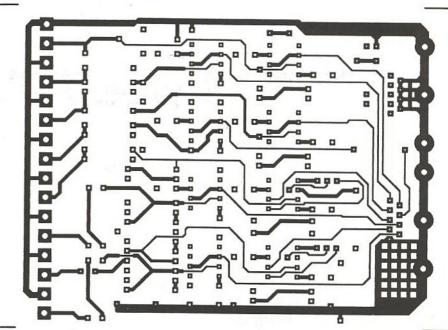

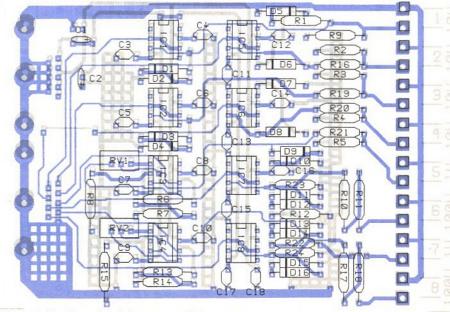

"CADPAK" = SAISIE DE SCHEMAS

DESSIN ET ROUTAGE DE CIRCUITS-IMPRIMES

SUR PC AT et 386/486

## NE SOYEZ PAS UN DINOSAURE. ...pour 1490 F TTC franco achetez "CADPAK"...

Interface utilisateur graphique moderne (icônes et souris)-Ecrans CGA, EGA, VGA, SVGA, avec ZOOMS - Export de fichiers vers PAO/TT - PCB en simple et double-face - Bibliothèques standards et CMS (extensibles par l'utilisateur) - Sorties sur matricielles, Lasers, plotters, Gerber, perçage à CN. NOTICE EN FRANCAIS. (version Démo contre chèque 50 Francs)

22 Rue Emile Baudot 91120-Palaiseau Tel: (1) 69 30 13 79 Fax: (1) 69 20 60 41

peuvent ne disposer que d'un seul connecteur femelle. En d'autres termes, ceci signifie que des répartiteurs en «T» sont permis sur le bus en plus de la daisy chain.

## Capacités recommandées des conducteurs

La capacité linéique des conducteurs SDA et SCL devrait être inférieure à 70 pF par mètre (valeur de la capacité de l'un des conducteurs par rapport à ceux réunis à l'écran). Le câble standard pour ACCESS.bus utilise des jauges de 26 pour le plus 5 V et la masse et de 28 pour SDA et SCL.

## Caractéristiques concernant les performances de la source d'alimentation

Plusieurs recommandations ont été émises au sujet des performances de la source d'alimentation.

La valeur de la tension

L'ordinateur fournissant l'ACCESS.bus doit fournir une tension de 5 V + /- 5 % (ceci permet de concevoir des systèmes en basse tension «3 V»).

Son temps de montée

Le temps de montée de cette alimentation doit être inférieur à 100 ms de façon à pouvoir assurer un reset correct des différents ACCESSoires présents sur le bus lors de la mise sous tension.

Sa charge capacitive

La source d'alimentation doit être capable de commander les diverses capacités de découplages présentes sur chacun des ACCESSoires. Une capacité de 10 µF par ACCESSoire est recommandée.

Les caractéristiques d'isolement

Deux ordinateurs équipés d'ACCESS. bus ne doivent pas être connectés entre eux sans avoir isolé tout d'abord les 5 Volts.

## Les possibilités d'alimentation auxiliaire

Des ACCESSoires nécessitant des courants importants peuvent posséder leur propre alimentation si cela est nécessaire. Dans ce cas, et de façon à satisfaire le protocole, il est nécessaire de prévoir un circuit de power on reset capable de «reseter» l'ACCESSoire quand l'alimentation du bus est présente.

Les valeurs de courants disponibles

Les (alimentations) ordinateurs équipés de port ACCESS.bus doivent être capables de fournir un minimum de 50 mA et un maximum de 1 A. Une limitation de courant (ou de sur-courant) doit être prévue et des informations sur le produit lui-même doit indiquer ses performances.

Les courants consommés et capacités par ACCESSoires

Chacun des «ACCESSoires» compatible à l'ACCESS.bus doit comporter clairement sur son boîtier la valeur du courant qu'il est sensé consommer et la capacité de charge qu'il représente sur les fils SDA et SCL.

Figure 4 : chaînage de plusieurs périphériques ACCESS.bus.

Cette recommandation permet rapidement de quantifier un réseau. Un exemple de concept est donné en figure 4.

## Configuration du réseau

Le nombre maximal d'éléments

Le nombre maximal d'éléments AC-CESS.bus permis sur le bus est de 125. Contrairement à ce que vous pourriez croire, la limite ne vient pas du fait qu'avec 125 éléments on ne voit plus son bureau, mais simplement de la limite de la gamme d'adressage des composants et du courant maximal que peut fournir l'ordinateur.

La configuration

La configuration physique du réseau doit satisfaire (au moins) les deux conditions suivantes :

a) La somme des courants consommés par tous les éléments branchés sur le réseau ne doit pas excéder le courant maximal que peut fournir l'ordinateur (ah!, que c'est beau le bon sens...).

b) La somme des capacités de «charge» de tous les éléments (câbles inclus) ne doit pas dépasser 800 pF (avec une source de courant de 3 mA).

Bien que le débit nominal de l'AC-CESS.bus soit inférieur à 100 kbits par seconde, vous pourrez remarquer, au chapitre concernant l'12C, que cette valeur correspond à celle de l'12C en mode rapide 400 kbits par seconde.

La longueur des câbles

Il n'y a pas de contrainte théorique et officielle de longueur maximale de câble. Les seules limitations physiques sont celles imposées d'une part par les spécifications du bus I2C (principalement pour satisfaire la valeur de son temps de montée entraînant la valeur de 800 pF sous 3 mA max.) et, d'autre part, que la chute de tension du 5 V reste dans les spécifications des +/- 10 % pour les ACCESSoires en dépit de leurs consommations maximales.

Généralement, sans autres formes de procès, la longueur «maximale» des câbles est de l'ordre de 8 m.

## Les EMC et ESD

Les EMC

L'écran du câble et le boîtier de la prise doivent être réunis à la masse logique ET de l'alimentation en UN SEUL point DANS l'ordinateur.

L'écran devrait être gardé séparé de la masse de l'alimentation et de la masse logique à l'intérieur des câbles AC-CESS.bus.

L'écran est isolé de la masse logique par une résistance de valeur minimale de  $100~\Omega$  à l'intérieur de chaque élément du réseau.

Le filtrage radio-fréquence doit être assuré par l'ordinateur au départ des fils du bus.

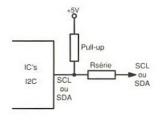

Les ESD (résistances série)

Du fait de l'emploi de sources de courant (pour augmenter la charge capacitive du bus), la valeur maximale des résistances à insérer en série, pour chacun des éléments connectables sur le bus avec chaque fil SDA et SCL (voir fiqure 5) est limitée à  $100 \Omega$ .

Figure 5

Ces résistances ont pour effet de filtrer légèrement les signaux et d'assurer une meilleure protection contre les phénomènes engendrés par les décharges électrostatiques.

Et, pour terminer cette partie, le niveau

de compatibilité I2C

«Sans autre indication mentionnée dans cette spécification (ACCES.bus), les interfaces matérielles reliées à l'AC-CESS.bus doivent être compatibles et conformes à toutes les spécifications du bus I2C publiées par Philips».

C'est clair et sans équivoque! Après ce hors-d'œuvres à fortes tendances hardware, nous allons passé à la partie un peu plus délicate orientée software.

## LE CONTENU DU PROTOCOLE

Ce contenu est le second fondement profond de l'ACCESS.bus.

Il se compose de deux grandes parties très distinctes qui ont pour nom : AC-CESS.bus BASE PROTOCOL et AC-CESS.bus APPLICATION PROTOCOL.

## L'ACCESS.bus Base Protocol

Autant le protocole I2C était le cœur de la partie électrique, autant le BASE PROTOCOL sera l'âme de l'ACCESS. bus

Il assure, comme indiqué précédemment, les couches 2 et 3 du modèle OSI/ISO.

A ce titre, sa fonction est commune à tous les périphériques (ACCESSoires) et définit les messages de COMMANDES et de STATUS échangés entre les éléments et le contrôleur de protocole qui sont utilisés principalement pour :

reconnaître et configurer chaque périphérique relié au système (à la mise sous tension ou pendant la marche normale);

- assigner à chaque périphérique un identificateur unique.

- connecter le «dévice drivers» approprié pour mettre en action le programme d'application spécifique associé pour qu'il puisse discuter avec son périphérique dédié.

### Axiome numéro 1

Dans le cadre du protocole ACCESS. bus, chaque élément participant est foncièrement un maître tacite (donc un «maître émetteur») qui, lorsqu'il n'a rien à dire, se positionne en «esclave récepteur».

Ceci sous-entend donc que, dans l'éventail des possibilités que possède le protocole I2C (représenté au tableau de la figure 6), deux d'entre elles sont ignorées, au moins, pour des applications directes de l'ACCESS.bus mais, par contre, peuvent très bien être utilisées par le même micro-ordinateur pour commander à l'aide des mêmes fils (mais à des adresses différentes), comme nous le verrons plus loin, pour commander des composants I2C standards.

### Axiome numéro 2

Le fait, pour chacun des éléments, de devoir être un «maître» impose directement de structurer le protocole et le réseau sous sa forme «multimaster» et donc de gérer les problèmes de synchronisation et d'arbitrage du bus.

Que fait un réseau, sinon que de transporter des messages ?

Alors, pour commencer, examinons le format de ceux-ci.

I<sup>2</sup>C ADDRESS ALLOCATION TABLE

|       | A2-A0                                                          |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

|-------|----------------------------------------------------------------|------------|-----------|------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----|--|--|--|

| 46-A3 | 0                                                              | 1          | 2         | 3                                        | 4                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                | 7  |  |  |  |

| Q     | General call<br>address                                        | Reserved — |           | -                                        |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

| 1     |                                                                |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

| 2     | PCF8200*<br>SAF1135:                                           | SAA5243*   |           |                                          | SAA9020*               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  | -  |  |  |  |

|       | 0.0.1100                                                       | SAA5245*   | SAA90681- |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

| 3     |                                                                |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SAA1136!                         |    |  |  |  |

| 4     | SAA1300-<br>TDA8444-                                           |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (100)<br>(100)                   | _, |  |  |  |

|       | PCF8574                                                        |            |           | -                                        | PCD3311/AL<br>PCD3312L | 三                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SA3028                           |    |  |  |  |

| 5     |                                                                |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

| 6     |                                                                |            |           | -3-3-13-13-13-13-13-13-13-13-13-13-13-13 |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

| 7     | PCF8576!-                                                      |            | PCF85771  | PCF8577AI                                | PCF8576*<br>PCF8579*   | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PCF8566<br>L_                    | -  |  |  |  |

|       | PCF8574*—<br>SAA1064L—                                         |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·                                |    |  |  |  |

| В     | TDA8420!—<br>TDA8421!—<br>TEA6300/T!—<br>TEA6310T!—            |            | TDA8045*  |                                          | TDA84221<br>TDA84611—  | SAA9050*<br>SAA9051*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SAA9062*<br>SAA9063*<br>SAA9064* |    |  |  |  |

| 9     | TDA84401—<br>PCF8591*—                                         |            | ===       |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  | 二  |  |  |  |

| A     | PCF8583*—<br>PCF8570*—<br>PCF8571*—<br>PCF8572*—<br>PCF8582AI— |            |           |                                          |                        | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |    |  |  |  |

| В     | PCF8570*-                                                      |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  | -  |  |  |  |

| С     | TSA5511*—<br>SAB3035*—<br>SAB3036*—<br>SAB3037*—               | TEA6000'   | TSA6057L  |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

|       | TDA84001-                                                      |            |           |                                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  | -  |  |  |  |

| D     | TDA8433I—<br>TDA8443AI—<br>TDA8573*—                           |            |           | =                                        |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |    |  |  |  |

| E     |                                                                |            |           |                                          |                        | Commercial |                                  |    |  |  |  |

| F     | Reserved—                                                      |            |           |                                          | 1                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  | -  |  |  |  |

Address Format: A8 A5 A4 A3 A2 A1 A0 RW Legend \*= RW, != W. := R

Figure 6 : allocation des adresses selon les circuits 12C.

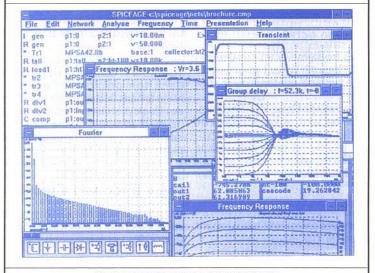

CAO sur PC/AT et compatibles PRIX "en promotion d'été" au lieu de 4950<sup>nt</sup>

3950FHT

ESSAYEZ.. ET VOUS SEREZ CONVAINCUS! COMMENT ECONOMISER SANS COMPROMIS

## «SPICEAGE POUR WINDOWS»

logiciel de simulation & d'analyse analogique sur PC

Une documentation complète et une disquette de démonstration interactive sont à la disposition GRATUITE des établissements d'enseignement et les professionnels de l'éléctronique, et au prix de 150 F ttc franco pour les particuliers.

91120 PALAISEAU

Tél.: (33) 1.69.30.13.79 Fax: (33) 1.69.20.60.41 Télex: 603 103 F

DISTRIBUTEUR EXCLUSIF DE TATUM LABS

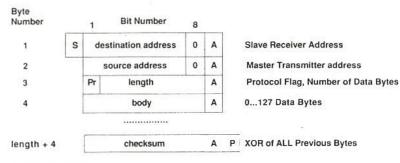

## Format du message

Le format du message est présenté sous deux formes différentes aux figures 7 et 8, la première sous sa forme conventionnelle I2C et l'autre sous une forme plus spécifique «ACCESS.bus» (décrite ici octet par octet), dans laquelle ont été omises volontairement les représentations des conditions de START, de STOP ainsi que les ACKnoledges, pour rendre plus lisible le contenu des octets.

Fréquemment, nous utiliserons cette dernière présentation pour décrire les valeurs à charger dans ces octets.

Comme vous avez pu vous en rendre compte, le contenu des octets n'a plus le même sens que celui du protocole I2C stricto-sensus.

La seule chose conservée à ce niveau est le fait que les bits de poids FORT sont envoyés en TÊTE.

## Le premier octet

En effet, bien que le premier octet décrive encore l'adresse du destinataire (esclave récepteur) du message (127 adresses disponibles mais, attention, seulement 14 ACCESSoires auront seulement le droit d'être présents en même temps), le deuxième octet a pour mission d'indiquer l'adresse du maître émettant.

Le dernier bit de ce premier octet est toujours un zéro, ce qui signifie que celui qui vient de démarrer un échange désire «écrire» ou, encore, souhaiterait démarrer un échange.

Nous avons donc affaire à un système potentionnellement multi-maîtres.

### Le deuxième octet

Le deuxième octet déclare l'adresse de la source qui désire émettre. A noter que cette possibilité n'existait pas précédemment de façon explicite dans le protocole I2C et que de nombreux utilisateurs, fonctionnant en mode multimaîtres, l'avaient déjà instaurée.

## Le troisième octet

Le MSB du troisième octet contient un «Protocol Flag» (Pr) ayant pour but de déclarer le type de contenu du message envoyé :

Pr = 0: ce ne sont que des données. Pr = 1: ce ne sont que des ordres de commandes ou d'états.

Les autres bits de cet octet indiquent le nombre d'octets de données qui vont suivre (de 0 au maximum de 127 octets).

### Les autres

Suivent ensuite les octets transportant les informations désirées.

## Le dernier

Enfin, le wagon de queue de tout ce petit train contient une «checksum» construit en faisant un XOR (un «OU exclusif) de TOUS les octets précédents (y compris l'octet d'adresse). La cheksum doit être calculée de sorte que le XOR de tous les octets précédents soit égal à zéro.

## Message Format

- S: Start Condition

- P: Stop Condition

- A: Acknowledge

- Pr: Protocol Flag (Pr=0: body is data; Pr=1: body is control/status)

Figure 7 : format du message I2C.

- Follows I2C addressing format

- · bits 7 through 1 form a 7 bit address

- · bit 0 is always zero indicating a master transmitter (write) operation

Figure 8: format du message ACCESS.bus.

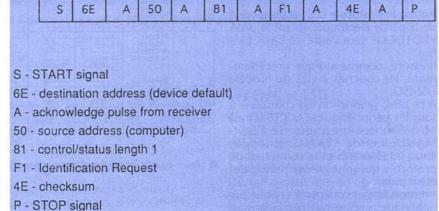

Un exemple de ce petit train est donné figure 8.

Tout cela n'étant pas trop compliqué dans son prinicipe, commençons maintenant à examiner les contenus des deux premiers octets des messages (le jeu d'adresses) qui ne sont pas aussi innocents que l'on pourrait le croire à première vue.

## Le jeu d'adresses disponibles

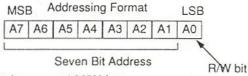

Les adresses de l'ACCESS.bus suivent celles de l'12C standard sur 7 bits (voir figure 9). Les adresses sur 10 bits ne sont pas permises.

Le huitième (LSB) sera toujours à zéro, comme indiqué précédemment, afin d'être en position de maître émetteur (ou d'écrire). Nous aurons donc toujours des adresses paires pour les adresses destinataires ou sources.

Pour les ACCESSoires de l'ACCESS. bus, un champ d'adresses a été réservé parmi les 128 possibles. Il s'agit (voir figure 6) de : 50 h pour l'ordinateur «host» d'accueil (mini, PC workstation...), puis 6 Eh comme adresse par défaut de TOUS les ACCESSoires à leur première mise sous tension et, enfin, 52 h à 6 Ch, soit quatorze adresses possibles qui seront assignées par le host à l'ACCESSoire selon son bon vouloir.

A noter que ce champ était laissé libre dans la table d'allocation des adresses proposées par PHILIPS pour l'usage de microcontrôleurs sans faire de recouvrement d'espaces avec d'autres types de composants I2C.

L'implémentation de l'ACCESS.bus sur un système doit au minimum tenir compte de ces adresses mais peut aussi tenir compte de l'intégralité du champ offert par l'I2C après s'être assuré que ces adresses ne sont pas utilisées par d'autres équipements.

Dernière remarque concernant les adresses : le bit de poids le plus faible de l'adresse source a été positionné à zéro mais n'a pas de signification particulière (à ce jour) en attendant une extension du bus si jamais elle ait lieu un jour.

Passons donc aux différents types de messages pouvant se présenter.

## Les différents types de messages

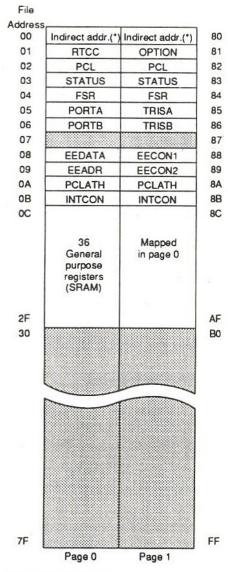

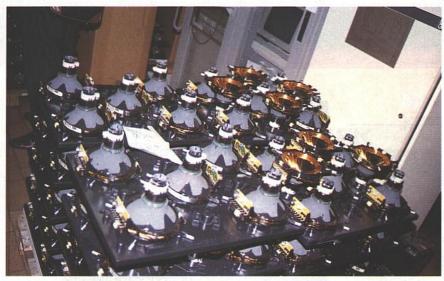

Le protocole ACCESS.bus définit huit types de messages différents qui sont résumés sur le tableau de la **figure 10**. Tel quel, ce tableau n'avoue pas du tout toutes ses subtilités cachées.