# RADIO PLANS AVRIL 93

LES MICROCONTRÔLEURS ST 62XX SGS-THOMSON. CARTE CONVERTISSEUR N/A POUR PC. LA TRANSMISSION VIDÉO SUR PAIRE TORSADÉE. MODULES «NOISE-GATE» FORMAT EUROPE.

**ELECTRONIQUE** APPLICATIONS

MENSUEL édité par

**Publications Georges Ventillard** Société anonyme au capital de 350 880 F Siège social

Direction-Rédaction-Administration-Ventes : 2 à 12, rue de Bellevue, 75940 Paris Cedex 19

Tél.: 42.00.33.05

Télex: PGV 220409F - Télécopie: 42.41.89.40

Président-Directeur Général, Directeur de la Publication : J.-P. VENTILLARD

Directeur de la Rédaction : Bernard FIGHIERA

Rédacteur en chef :

Claude DUCROS

Publicité: Société Auxiliaire de Publicité

70, rue Compans, 75019 paris Tél.: 42.00.33.05 - C.C.P. 37-93-60 Paris Directeur commercial: J.-P. REITER

Chef de publicité: Francine FIGHIERA

Assistée de : Laurence BRESNU Marketing: Jean-Louis PARBOT

Directeur des ventes : Joël PETAUTON Inspecteur des ventes : Société PROMEVENTE

M. Michel IATCA

11, rue de Wattignies, 75012 Paris.

Tél.: 43.44.77.77 - Fax: 43.44.82.14

Service des abonnements :

2 à 12, rue de Bellevue, 75019 Paris. Voir notre tarif «spécial abonnement».

Pour tout changement d'adresse, envoyer la dernière bande

accompagnée de 2,50 F en timbres.

IMPORTANT : ne pas mentionner notre numéro de compte

IMPORTANT: ne pas mentionner notre numero de compte pour les paiements par chèque postal. Electronique Radio Plans décline toute responsabilité quant aux opinions formulées dans les articles, celles-ci n'engageant que leurs auteurs. Les manuscrits publiés ou non ne sont pas retournés.

«La loi du 11 mars 1957 n'autorisant aux termes des alinéas 2 et 3 de l'article 41, d'une part que «copies ou reproductions strictement réservées à l'usage privé du copiste et non destinées à une utilisation collective» et d'autre part, que les analyses et les courtes citations dans un but d'exemple et d'illustration, «toute représentation ou reproduction intégrale, ou partielle, faite sans le consentement de l'auteur ou de ses ayants-rause, est lilicitée» (alinéa premier de l'article 40). Cette redroit ou ayants-cause, est illicite» (alinéa premier de l'article 40). Cette re-présentation ou reproduction, par quelque procédé que ce soit, constituerait donc une contrefaçon sanctionnée par les articles 425 et suivants du Code Pénal»

Ce numéro a été tiré à 39 000 exemplaires Dépôt légal avril 93 - éditeur 1716 Mensuel paraissant en fin de mois. Distribué par S.A.E.M. Transport-Presse Photocomposition COMPOGRAPHIA - 75011 PARIS -Imprimerie SIEP Bois-le-Roi et REG Lagny. Photo de couverture : E. Malemanche.

#### ETUDE ET CONCEPTION

- 15 Quatre modules «portes de bruit» audio.

- Carte de conversion N/A pour PC.

#### MONTAGES

- Deux convertisseurs à découpage 12 V. 11

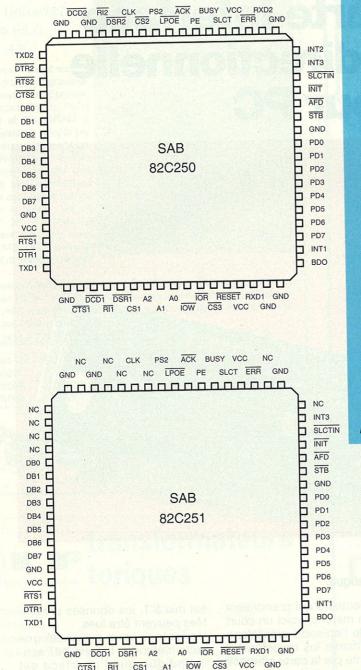

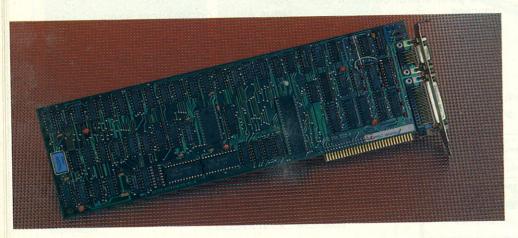

- 67 Carte parallèle bidirectionnelle pour PC.

#### TECHNIQUE

- Le démarrage des oscillateurs à résonateur. 7

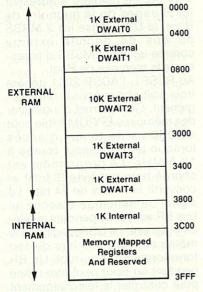

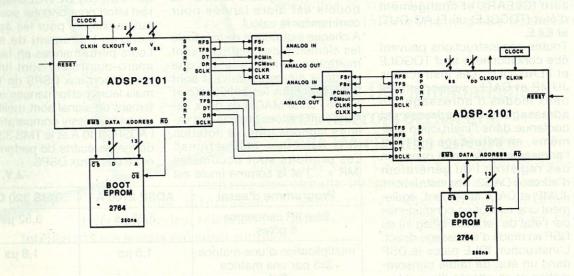

- Les DSP Analog Devices (2). 57

#### CIRCUITS D'APPLICATION

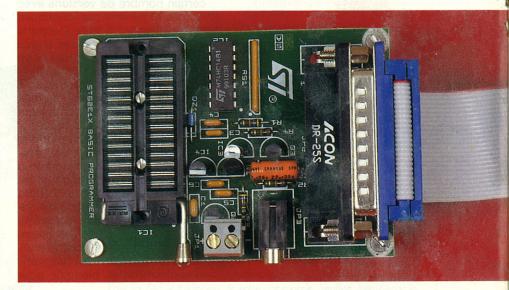

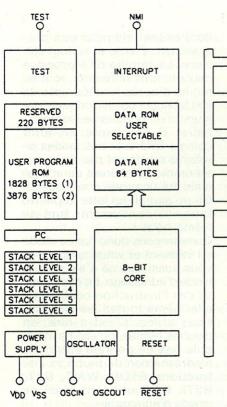

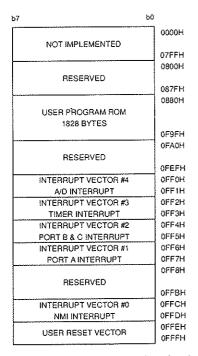

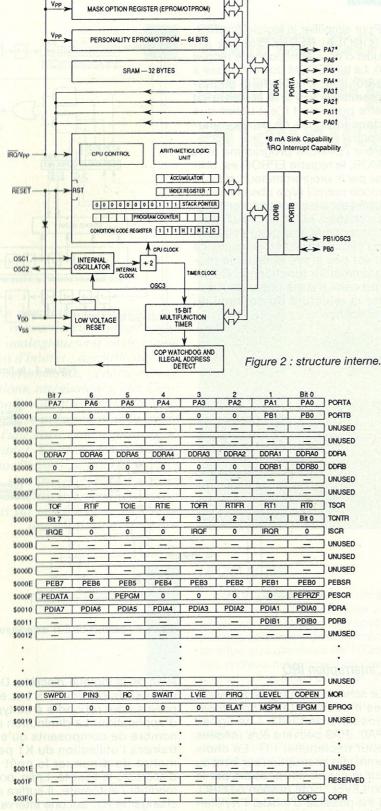

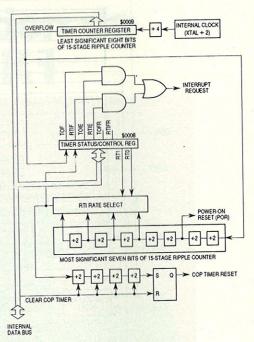

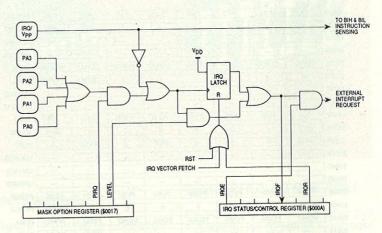

41 Les microcontrôleurs ST62XX, SGS-Thomson

#### COMPOSANTS ET TECHNOLOGIE

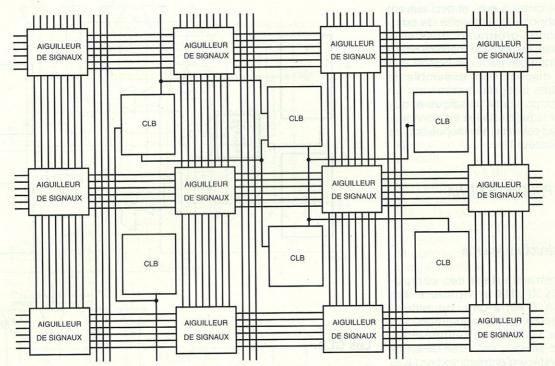

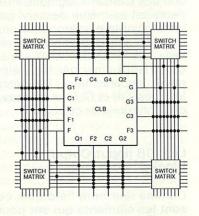

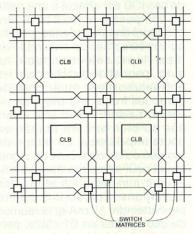

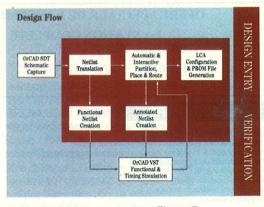

- 35 Les FPGA XC4000 XILINX.

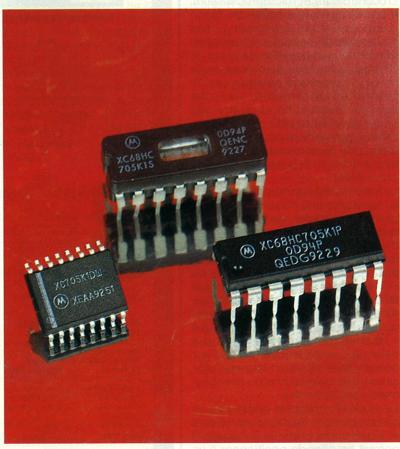

- 46 Présentation du 68HC705K1 MOTOROLA.

#### COMMUNICATION

La transmission vidéo sur paire torsadée. 25

#### infos

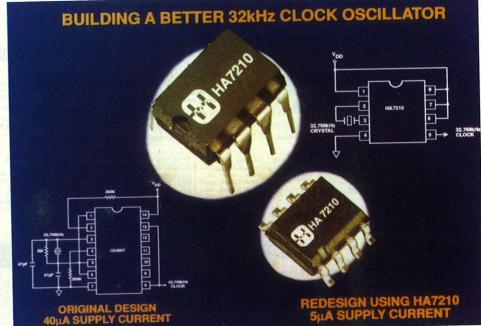

- Le HA7210, Cl oscillateur basse tension

- Le générateur de mires TV SIDER 920.

- Un nouveau compteur universel: le HP53131A.

- Des EEPROM 16 kbits I2C chez SGS-THOMSON.

Ont participé à ce numéro : J. Alary, J.-Y. Bedu, C. Broussas, P. de Carvalho, F. de Dieuleveult, X. Fenard, A. Garrigou, P. Gueulle, J.-P. Jacquet, P. Oguic, D. Paret.

## a and a

# Le démarrage des oscillateurs

Quels sont les éléments importants pour le bon fonctionnement d'un oscillateur? Comment le résonateur doit-il être spécifié pour être certain que le montage fonctionnera dans les conditions les plus défavorables? Peut-on remplacer, dans un montage considéré, un quartz par un résonateur céramique moins cher? Pourquoi le montage n'oscille-t-il plus quand on remplace le résonateur à 4 MHz par un résonateur à 32 kHz? Combien de fois avons-nous entendu ces simples petites phrases? Que de bonnes questions! Lors des deux précédents numéros, nous vous avons décrit comment réussir à faire fonctionner des oscillateurs pour microcontrôleurs et comment définir le type de quartz ou résonateur céramique à utiliser. Ce dernier article concernant ce domaine va évoquer comment résoudre les cas difficiles du «démarrage» des oscillateurs et comment savoir rédiger les lignes et cases parfois si complexes des OEF («Order Entry Form») des constructeurs.

Qu'est-ce encore que ces bêtes étranges - OEF - ?

Pour les non-initiés, sachez que les OEF sont d'horribles feuilles que chaque constructeur de microcontrôleur demande de remplir à chacun des utilisateurs de microcontrôleurs masqués au moment où ces derniers sont prêts à donner leurs «codes» à rommer. Ce «papier» étant par principe «contractuel», il vaut mieux ne pas se tromper en ce qui concerne les multiples options qui sont offertes (ports, types de reset...)..., y compris celles concernant les oscillateurs, (sinon le lot de composants rommés que vous recevriez pourrait à la riqueur vous servir de - chers pin's!

Maintenant que nous vous avons bien sensibilisés au problème, vous êtes prêts à pouvoir nous suivre dans ce dédale oscillatoire.

#### LE DÉMARRAGE DES OSCILLATEURS

Le démarrage d'un oscillateur n'est possible que lorsque les deux conditions suivantes sont remplies :

- il doit y avoir un signal de départ à la fréquence d'oscillation, - si, après avoir appliqué un signal de démarrage, le niveau du signal de sortie est trop faible alors il faut que le gain de boucle soit supérieur à l'unité (pour qu'il y ait divergence).

Normalement, la première condition est toujours remplie du fait de la présence de «bruit thermique» ou encore d'impulsions dues à la mise sous tension du montage.

Avec un gain de boucle supérieur à l'unité, le signal à la fréquence d'oscillation sera amplifié et s'accroîtra exponentiellement jusqu'à un niveau adéquat.

La valeur de R1 max telle que nous l'avons chiffrée dans l'article précédent garantit un gain de boucle de «1», aussi devonsnous prendre une valeur inférieure de façon à être certain du démarrage.

Cependant, le fait de prendre certaines marges de sécurité ne résoud pas tous les problèmes de démarrage. En effet, très souvent, même un démarrage «fiable» prenant trop de temps n'est pas acceptable pour l'utilisateur.

Examinons plus en détail ce point particulier.

L'amplitude du signal de l'oscillateur croit exponentiellement avec la constante de temps :

$$\tau = -\frac{2 L}{Rt}$$

(le signe moins est utilisé parce que nous sommes en présence d'une résistance négative).

Équation dans laquelle L est la valeur de l'inductance série du résonateur et Rt la somme des résistances R1 (résistance série résonateur) et Rosc (Résistance – de valeur négative – présentée par le montage oscillateur à l'ensemble L1, C1, R1).

Le calcul de R1 max effectué dans le numéro précédent a donné en fait la valeur maximale de Rosc pour un gain de boucle unité:

Rosc = - R1max

Dans le cas théorique où Rt=0,  $\tau$  devient infini et la tension d'oscillation ni ne s'accroît ni ne décroit. Pour Rt inférieur à 0 nous obtenons une valeur positive pour  $\tau$  et la tension d'oscillation croit exponentiellement.

Exemple 1

Prenons l'exemple d'un résonateur céramique à 3,58 MHz ayant pour valeurs L1 = 440  $\mu$ H et R1 = 8  $\Omega$  et le montage de l'exemple utilisant le 84 C xxx dans lequel Rosc = - R1max = - 10,5  $\Omega$ . Ce qui donne pour  $\tau$ :

$\tau = -\frac{2 \times 440 \cdot 10^{-6}}{8 - 10.5} \cong 0,35 \text{ ms}$

Exemple 2:

Prenons maintenant le cas d'un montage à quartz dans lequel L1 = 41 mH, R1 inférieure à 60  $\Omega$  et dans le cas où Rosc = - R1 max. : 248  $\Omega$ , on obtient en utilisant la même formule :

$\tau = 0.44 \text{ ms}$

### Temps de démarrage de l'oscillateur

Après avoir chiffré la constante de temps de démarrage de l'oscillateur, venons-en maintenant' au temps qui lui est nécessaire pour se mettre réellement en branle.

Cette valeur est fondamentale dans de nombreux montages qui passent leur temps à «s'endormir» (pour de sombres raisons de consommation) puis à se réveiller le plus rapidement possible dès qu'une catastrophe poind à l'horizon d'une entrée d'interruption par exemple.

Le démarrage de la tension d'oscillation aura une certaine valeur à la mise sous tension et croitra jusqu'au niveau adéquat pour faire fonctionner la partie digitale du circuit intégré.

Sachant qu'à chaque période, l'amplitude du signal augmentera d'un facteur «e» (= 2,71828), il est possible d'estimer le nombre de périodes qu'il est nécessaire d'effectuer pour atteindre le seuil fatidique de tension de l'amplificateur (connu pour une technologie donnée).

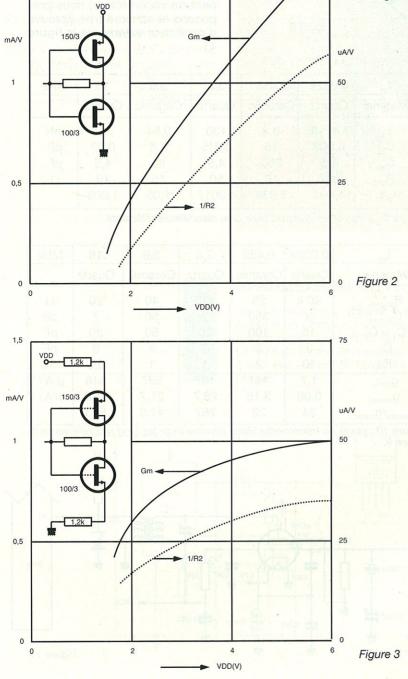

Le nombre de périodes peut être estimé à l'aide de l'équation suivante : (d'accord ça fait un peu «parachuté» mais les calculs sont disponibles pour les curieux) : Les variations de ce paramètre en fonction de la réalisation des transistors CMOS «N» et «P» sont données **figures 2** et **3**.

La première figure montre que gm dépend énormément de la tension d'alimentation.

La seconde figure montre qu'après avoir introduit des résistances de contre-réaction dans les «sources» des transistors, la transconductance est rendue moins dépendante de l'alimentation.

De plus, pour des composants en CMOS, ce paramètre «gm» varie peu en fonction de la fréquence

$$N \cong Ln [16 Fosc^2 L1 \frac{Co + Cit}{Cit} (Co + \frac{Cit \times Cot}{Cit + Cot})]$$

où Fosc = fréquence d'oscillation, L1 = inductance série du résonateur,

Co = capacité parallèle du résonateur.

Cit = Capacité totale d'entrée, Cot = capacité totale de sortie,

Ln = Logarithme néperien et le temps de démarrage égal à  $t = N \times \tau$

En reprenant les valeurs citées plus haut (440  $\mu$ H et 40 pF) du premier exemple à résonateur céramique on obtient t = 1 ms et, en prenant celles du montage à quartz (41 mH et 4 pF), on obtient 2,5 ms.

#### Et si on parlait un peu transconductance Gm de l'amplificateur

Pour terminer cet article, nous allons revenir au point de départ de cette petite série (en fait «boucler» semble assez normal quand on évoque le sujet des oscillateurs)

En effet, si par les temps qui courent, on considère que le choix de l'élément résonant s'effectue (hélas) principalement en fonction de considérations souvent plus économiques que techniques, le seul élément auquel il est nécessaire de s'intéresser est le malheureux amplificateur intégré qui n'en demandait pas tant.

Son schéma équivalent est à nouveau donné figure 1 dans lequel en lieu et place de «i» nous avons écrit (gm x V1).

La transconductance «gm» est alors le paramètre le plus important du montage (ce paramètre fut aussi longtemps appelé la «pente» «s» du montage). (au moins dans les plages qui nous concernent) et peut donc être mesuré en statique.

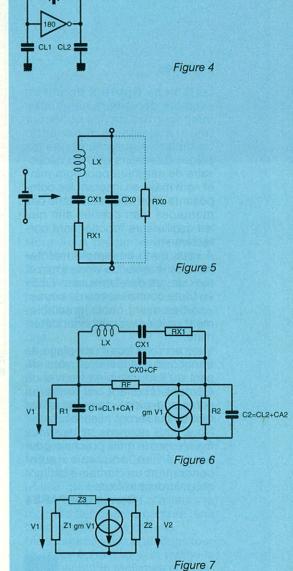

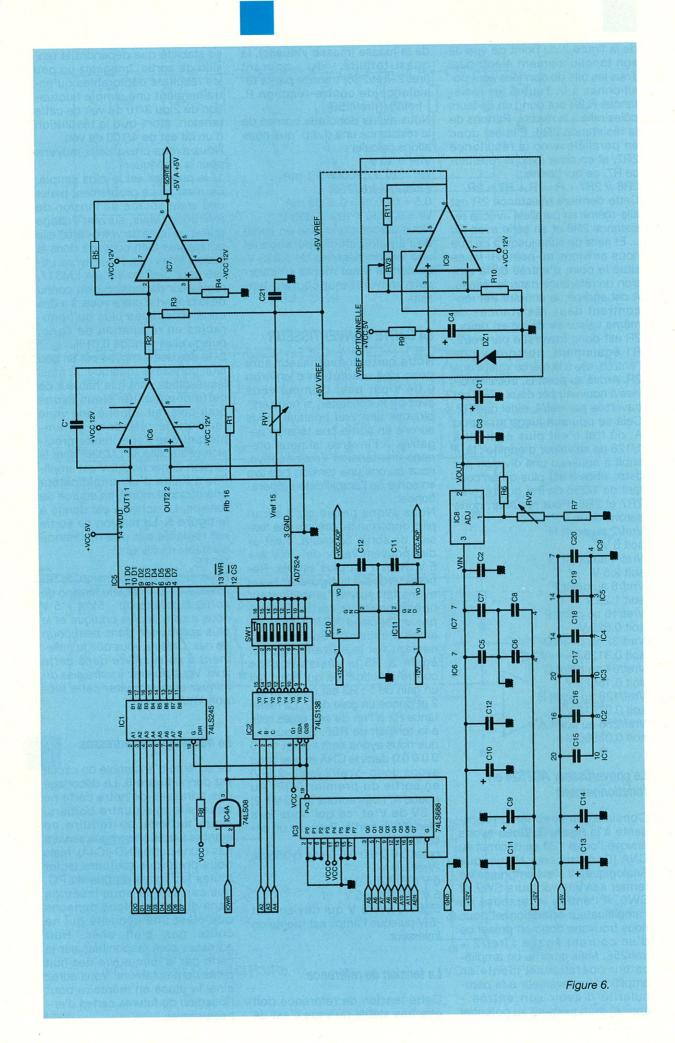

Si l'on en revient maintenant au montage figure 4, il faut lui adjoindre l'élément résonant (et son schéma équivalent figure 5) pour être complet figure 6. Sa version équivalente est indiquée figure 7 dans laquelle Z1, Z2, Z3 sont les impédances équivalentes de chaque branche. On en déduit très simplement que :

V2 = - gm x V1 ( Z2 / (Z1 + Z3) Le gain de boucle est unitaire si la tension de contre-réaction est égale à la tension d'entrée initia-

lement présente V1 soit : V1 = V2 X (Z1 / (Z1 + Z3). Ces deux équations permettent de définir la condition d'oscilla-

$$gm = -\frac{Z1 + Z2 + Z3}{Z1 \times Z2}$$

et compte tenu des éléments équivalents des branches, on calcule Z1, Z2, Z3 ce qui donne la valeur de gm (en fonction de la pulsation  $\omega$ ).

Les valeurs de gm

tion entretenue:

La valeur calculée de gm est un nombre complexe dont il est nécessaire de rendre nulle la partie imaginaire pour ne conserver que la partie réelle.

L'annulation de ce terme amène à résoudre une équation du second degré en fonction de la pulsation et donne donc deux valeurs possibles pour gm (en fait une plage de valeurs entre lesquelles le montage pourra osciller).

Une manière simple et imagée de représenter ces solutions est de résoudre géométriquement dans ENTREE CF SORTIE

V1 R1 CA1 gm V1 R2 CA2 V2

Figure 1

1,5

le plan complexe l'équation correspondant aux deux membres de cette dernière :

- gm x (Z1 x Z2) d'une part = (Z1 + Z2 + Z3) d'autre part.

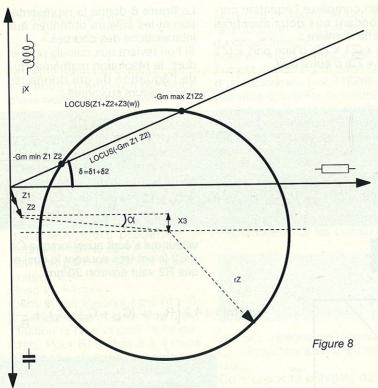

La figure 8 donne la représentation et les valeurs obtenues aux intersections des courbes.

Si l'on revient aux calculs purs et durs, la résolution mathématique de l'équation de gm donne les deux valeurs suivantes:

$$gm \ max = \frac{C1 \ C2}{R_{X1} \left(C_{X0} + C_F\right)^2 + 1 / \left(\omega^2 \ R_F\right)}$$

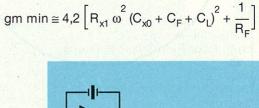

$$gm \ min = \left(2 + \frac{C_1}{C_2} + \frac{C_2}{C_1}\right) \left[ \ R_{X1} \ \omega^2 \left(C_{x0} + C_F + C_L\right)^2 + \frac{1}{R_F} \right] + \frac{C_2}{R_1 C_1} + \frac{C_1}{R_2 C_2}$$

valeur qui s'écrit aussi lorsque C1 = C2 (c'est très souvent le cas) et que R2 vaut environ 20/gm:

En réponse à des courriers de lecteurs.

1. Nous reviendrons sur une question très «salée» concernant la mise en parallèle (et leur commutation possible) de deux éléments résonants de façon à pouvoir minimiser la consommation lors d'un prochain article s'intéressant aux microcontrôleurs faible consommation. Disons dès à présent qu'à l'aide de l'article ci-dessus, en calculant l'impédance équivalente à l'ensemble des deux mis en parallèle et en s'aidant de la connaissance de am de l'oscillateur, on peut d'ores et déjà obtenir une réponse très «smart» au problème posé.

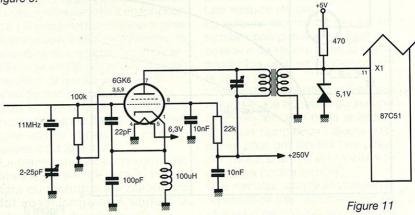

2 - Pour ceux qui auraient encore vraiment du mal à faire fonctionner l'oscillateur interne de leur petit microcontrôleur, nous proposons le schéma très éprouvé d'oscillateur externe de la figure

#### **Exemples**

Le tableau figure 9 donne un exemple de valeurs habituellement fournies par les constructeurs d'éléments résonants. Le tableau figure 10 donne les plages de valeurs qu'il est nécessaire de satisfaire pour «gm min» et «gm max» en insérant les composants cités ci-dessus dans des montages bien connus afin que les oscillateurs fonctionnent correctement.

A vous donc de remplir maintenant les «cases» de valeurs min et max de gm des fameuses «OEF» en toute connaissance de cause : soit en ayant choisi préalablement un élément résonant déterminé.

- soit en vous fixant une plage de transconductance et en vous disant qu'il faudra bien trouver un élément résonant qui rentre au «chausse-pied» dans les paramètres qui seront nécessaires! Nous vous donnons rendez-vous maintenant le mois prochain pour entamer un nouveau sujet concernant un domaine brûlant

des microcontrôleurs!

**Dominique PARET**

| f <sub>os</sub>                            | 0,0328                                                | 0,455                           | 3,6                                 | 3,6                             | 16                              | MHz                 |

|--------------------------------------------|-------------------------------------------------------|---------------------------------|-------------------------------------|---------------------------------|---------------------------------|---------------------|

| Material                                   | Quartz                                                | Ceramic                         | Quartz                              | Céramic                         | Quartz                          |                     |

| $L_x$ $C_{x1}$ $C_{x0}$ $R_{x1}$ $f_p/f_s$ | 7,8. 10 <sup>6</sup><br>0,003<br>1,5<br>20 k<br>1,001 | 8,2<br>15<br>250<br>10<br>1,038 | 130<br>0,015<br>4,5<br>50<br>1,0017 | 0,54<br>3,6<br>35<br>15<br>1,05 | 5<br>0,02<br>4,5<br>10<br>1,002 | mH<br>pF<br>pF<br>Ω |

Figure 9 : paramètres typiques pour cinq résonateurs différents.

| f <sub>os</sub>                      | 0,0328 | 0,455   | 3,6    | 3,6     | 16     | MHz  |  |  |

|--------------------------------------|--------|---------|--------|---------|--------|------|--|--|

| Material                             | Quartz | Ceramic | Quartz | Ceramic | Quartz |      |  |  |

| R <sub>X1 max</sub>                  | 40 k   | 25      | 120    | 40      | 20     | Ω    |  |  |

| C <sub>Xomax</sub>                   | 3      | 350     | 7      | 50      | 7      | pF   |  |  |

| $C_1 = C_2$                          | 15     | 100     | 20     | 50      | 20     | pF   |  |  |

| C <sub>F</sub>                       | 3      | 3       | 3      | 3       | 3      | pF   |  |  |

| R <sub>F</sub>                       | 10     | 2       | 1      | 1       | 0,5    | ΜΩ   |  |  |

| 9 <sub>mmin</sub>                    | 1,7    | 141     | 107    | 527     | 348    | μA/\ |  |  |

| 9 <sub>mmax</sub>                    | 0,06   | 3,15    | 28,7   | 21,7    | 182    | mA/\ |  |  |

| g <sub>mmax</sub> /g <sub>mmin</sub> | 34     | 22      | 267    | 41,5    | 523    |      |  |  |

Figure 10 : plage de transconductance permise pour les cinq résonateurs de la figure 9.

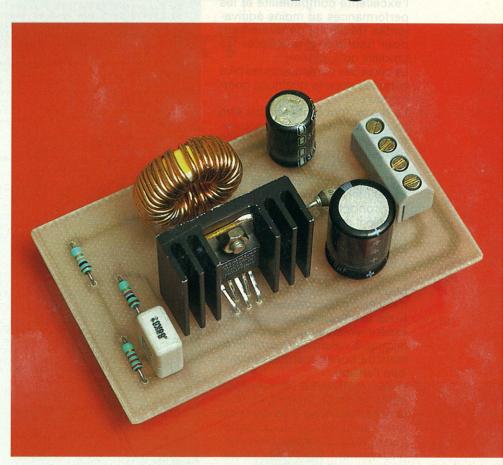

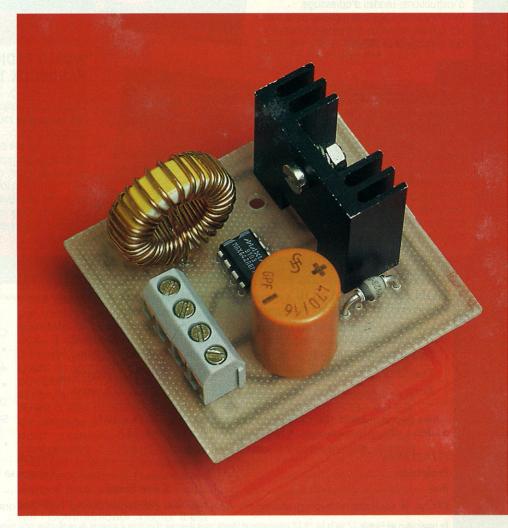

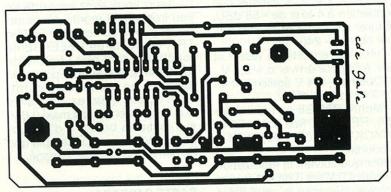

## **Deux convertisseurs** 12 V à découpage

Bien qu'il s'agisse de l'une des tensions d'alimentation les plus courantes qui soient, on ne dispose pas toujours de 12 V là où l'on en aurait besoin. Les deux petits convertisseurs continu-continu à découpage dont nous vous proposons la réalisation offrent une solution élégante pour produire, avec un excellent rendement énergétique, quelques ampères sous 12 V à partir de tensions supérieures ou inférieures (par exemple 6 ou 24 V). Mais les principes utilisés seraient facilement transposables à des puissances ou des tensions différentes.

#### UN ABAISSEUR 24 V À 12 V :

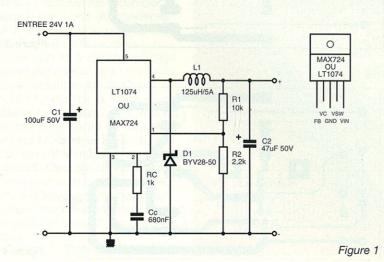

Le schéma de la figure 1 fait appel à un composant récent et particulièrement attrayant, le LT1074 de Linear Technology, ou à son équivalent le MAX724 de Maxim.

Nous vous présenterons en détail cette famille de régulateurs à découpage «5 pattes», aussi ne nous étendrons nous pas sur les principes mis en jeu puisqu'il s'agit là, tout simplement, du schéma d'application typi-

Les valeurs de composants ont été calculées à l'aide du logiciel Switchercad, puis quelque peu adaptées en fonction des possibilités d'approvisionnement en France et des performances mesurées en laboratoire.

En principe, Switchercad est offert aux clients de Linear Technology à la condition qu'il ne soit utilisé qu'avec les composants de la marque : c'est d'ailleurs la moindre des choses compte tenu de la qualité de ce cadeau.

Mais comme nous attendons toujours les échantillons et même la documentation réclamés aux distributeurs français de la marque, il était bien tentant de s'intéresser aux «secondes sources» aimablement fournies par Maxim.

Notre maquette a donc été réalisée avec un MAX724, dont nous avons pu vérifier à cette occasion l'excellente compatibilité et les performances au moins équivalentes (Maxim a généralement pour habitude d'améliorer les produits qu'il «clone»).

Le choix des composants les plus critiques appelle quelques commentaires:

La diode, tout d'abord, doit être un modèle à temps de recouvrement négligeable. La BYV 28-50 permet d'atteindre aisément 2 A en sortie, mais on pourrait faire nettement mieux avec une BYW 80-50 convenablement refroidie. Les condensateurs chimiques devraient en principe être du type à faible impédance série (Low ESR) : celui d'entrée doit en particulier supporter un courant efficace de près d'un ampère et pourrait chauffer s'il n'était pas de qualité suffisante.

Nous avons toutefois pu vérifier expérimentalement que des chimiques à l'aluminium ordinaires mais de bonne marque peuvent

faire l'affaire. Pièce maîtresse du montage après le circuit intégré, l'inductance a fait l'objet d'un choix qui peut surprendre au premier abord, mais que nous avons soigneusement validé en laboratoire : une self d'antiparasitage de

triacs 125 µH/5A Monacor. On pourrait craindre que ce composant se comporte médiocrement à la fréquence de 100 kHz utilisée ici, mais en pratique nous avons pu mesurer un rendement de 83% à pleine charge et une consommation à vide inférieure à 10 mA.

Un choix concurrent menant quasiment aux mêmes résultats consiste à bobiner 33 spires de fil émaillé 10/10 sur un tore en matériau Philips 2P80 (poudre de fer) de 94 nH/sp2. C'est un peu plus encombrant, nettement plus lourd, mais moitié moins cher!

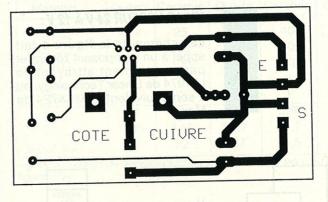

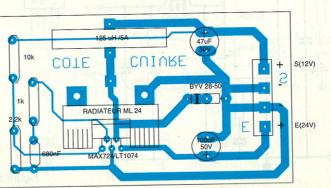

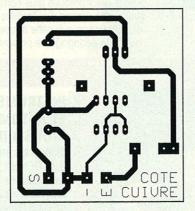

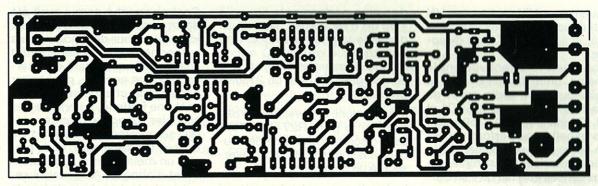

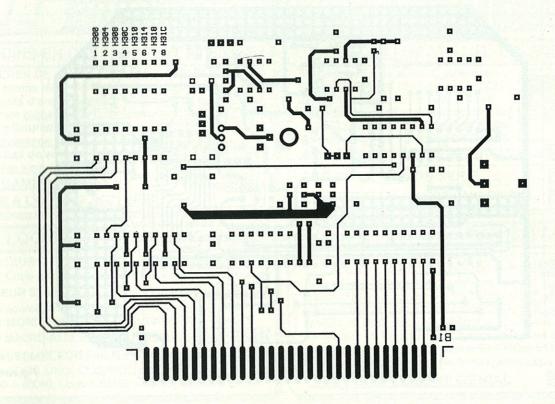

Compte tenu des courants en jeu et de la fréquence de fonctionnement, le tracé du circuit imprimé de la figure 3 est critique : on s'y conformera donc soigneusement, ainsi qu'au plan de câblage de la figure 4.

Moyennant quoi, on aboutira à un module de dimensions modestes, particulièrement facile à utiliser puisque équipé d'un bornier à vis. Nous l'avons testé, branché sur une batterie 24 V,

```

************************** SW 2.0 ******* 2/ 1/1993*******

(C) Copyright, 1991, 1992. Linear Technology.

1630 McCarthy Blvd, Milpitas, CA 95035. 408-954-8400

Topology: Positive Buck Part: LT1074

C3 Not required.

Gowanda GT10-115 95μH R=0.030Ω

L2 Not required.

D1 Hotorola Schottky 1N5825 If=5A Vr=40V Trr=OnS R1 9.79 kn 1%

R2 2.21 kn 1%

RC Suggested value(not for production use): 1.00 kΩ 5% CC Suggested value(not for production use): 1.00 μF U1 LT1074 Im=5.50A Vs=1.6V Rsu=0.10Ω f=100kHz

1 Vout=12V VinHin=20V VinNom=24V VinHax=30V

2 Iomin=0.0A Ionom=2A Iomax=2A

3 Ripple=200mV TaHax=50°C TjHax=100°C TjDmax=100°C

O.129 Operating Hode at full load current

O.131 Duty Cycle

O.132 Max Rated Switch Current at this D.C.

O.133 Peak Inductor/Switch Current

O.134 Output current at crossover (cont/dis)

O.135 Is Max Switch Current Exceeded?

O.136 Is Max Duty Cycle Exceeded?

= 5.500 A

= 2.217 A

O. 139 RMS Inductor Current

O. 140 Peak Inductor Current

O. 141 P-P Inductor Ripple Current

O. 142 Inductor V*ps Product

2.217 A

0.434 A p-

41.2 V*Ps

=

0.145 Input capacitor RMS ripple current 0.149 Output capacitor RMS ripple current

0.945 A RMS

0.125 A RMS

O.159 Output ripple (p-p) without filter

O.160 Is an Output Filter Required?

191.0 mV p-p

23

__No__ mv p-p

0.176 Output ripple voltage after filter

2.217 A

2.000 A

O. 186 Peak Switch Current

O. 187 Average switch current during on time = 0.194 Is an IC Heat Sink Required? = I.196 Thermal Resistance of IC Heat Sink Selec =

-Yes_

13°C/W

O. 197 IC Temperature at Max Ambient Temp

0.657 A

0.200 Avg Diode Current

0.200 Avg Diode Current

0.202 Avg diode current during on time

0.203 Hax Diode Reverse Voltage @VinH

1.205 Diode Forward Voltage for Thermal Calc

0.213 Is a Diode Heat Sink Required?

1.215 Thermal Resistance of Diode Heat Sink Se

0.216 Diode Temperature at Max Ambient Temp

2.000 A

30.0 V

0.5 V

No_- °C/W

68 °C

3.17 W

0.33 W

0.227 Total IC loss

0.230 Total Diode loss

0.233 Total inductor loss

0.26

0.15 W

0.234 Input capacitor loss

0.235 Output capacitor loss

0.01 W

3.91 W

0.236 Total of all losses

0.238 Input power

0.239 Input Supply Current

0.240 Efficiency

30.24 W

1.512 A

86.0 % Figure 2

```

Figure 3

Figure 4

dans deux situations très différentes: d'abord en le faisant débiter sur une ampoule «code» de 36 W, puis en lui faisant alimenter un émetteur-récepteur 27 MHz de 4 W AM.

La surcharge temporaire à 3A a été vaillamment supportée, tandis que la réception radio n'a subi aucune interférence provenant du convertisseur.

Dans les deux cas, le radiateur ML24 de 17° C/W tiédit tout juste à la température ambiante de 20° C: nous sommes à cent lieues du simple régulateur linéaire chutant par effet Joule 12 V sous 2 ou 3 A!

#### UN ÉLÉVATEUR 6 V À 12 V

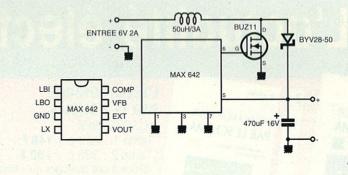

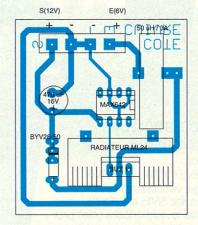

Faute d'avoir pu obtenir à temps des régulateurs «5 pattes» élévateurs, nous avons bâti notre schéma de la **figure 5** autour d'un micro-régulateur à tension fixe MAX642 (12 V) pilotant un MOS de puissance séparé.

Ce n'est pas plus encombrant, mais un peu moins optimisé car on ne dispose plus de la puissance de calcul de Switchercad pour dimensionner les composants périphériques: tout au plus peuton s'inspirer des résultats relatifs à un convertisseur faisant le même travail à une fréquence voisine

Ce montage arrive tout de même à produire 1 A sous 12 V à partir d'une batterie de 6 V, avec un rendement de 91% et une consommation à vide de l'ordre du milliampère!

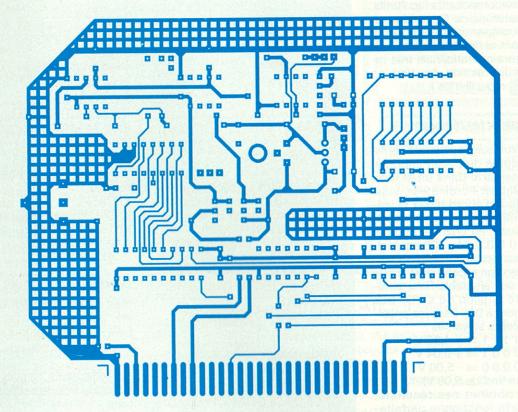

Cela avec une self de 50 µH/3A de même provenance que la précédente, ou avec le même tore 2P80 sur lequel on bobinera cette fois 23 spires de fil émaillé 10/10. Là encore, le tracé du circuit imprimé de la figure 6 est critique, et conduit à l'implantation de la figure 7, relativement compacte puisqu'il n'y a pas de condensateur d'entrée ni de résistances d'ajustement de la tension.

Une version 15 V de ce montage pourrait par contre être construite en remplaçant le MAX642 par un MAX643, quitte à retoucher quelque peu la valeur de la self. L'entrée et la sortie se font toujours sur un bornier à vis, dont le brochage est le même que précédemment. Cela ajouté au fait que la carte présente la même largeur (mais une longueur moindre) rend ces deux modules aisément interchangeables suivant les circonstances.

Patrick GUEULLE

Figure 5

Figure 6

Figure 7

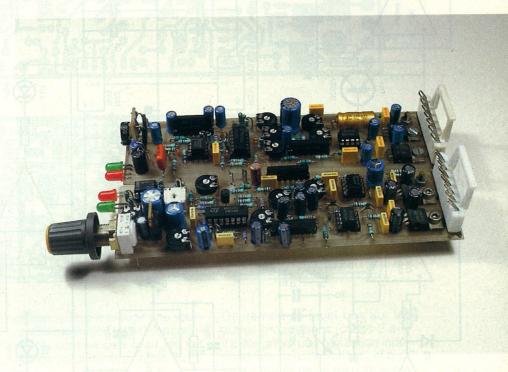

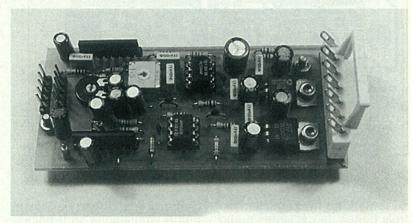

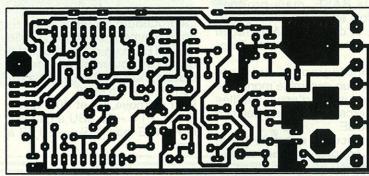

### **Modules «portes** de bruit» à la carte

Venant compléter la série de 19 cartes utiles pour la sono publiées dans les numéros 520, 521, 527 et 539, voici quatre autres réalisations pratiques performantes: 1 - Enfin (!) un NOISE-GATE au format du L6N2, ce qui permet d'inclure six ou huit pièces dans un rack 1 U. 2 - Un nouvel afficheur compatible avec les cartes EUROPE de premières générations (NGSE, LCSE, Nº 496), réduisant de manière significative la consommation light (70 mA toutes LED allumées), et ouvrant la porte vers des versions 160 mm (au lieu de 220 mm). 3 - Une implantation «de recherche» incluant VCA, détecteur RMS, régulateurs de tension, sur une carte minimum: 100 x 45 mm, qui sera utilisée sans plus tarder comme partie active d'un ensemble très complet, grâce à la carte nº 4. 4 - SIDE CHAIN pour NOISE-GATE en 3U, préparée EUROPE. En couplant les cartes 2, 3 et 4 on obtiendra un appareil plutôt à usage studio, et GATE6 (carte 1) soigneusement préréglée pourra suffire à ravir les sonorisateurs avides de silence.

En 1988, ERP abordait les périphériques de studio et sono, en offrant des réalisations à usage professionnel qui ont été reproduites depuis lors à un nombre conséquent d'exemplaires. Cinq ans plus tard, certains entreprennent toujours de les construire, mais comme l'expérience sur le terrain a mis en évidence des améliorations intéressantes, ces nouvelles cartes serviront de mise à jour pour les versions 1988, sans toutefois faire double emploi: en effet, une implantation au format des L6N2 (attendue depuis environ quatre ans...) est une nouveauté. S'il n'a pas été possible d'y intégrer certaines fonctions particulières demandées par quelques utilisateurs professionnels (telle une «pré-indica-tion» 3 dB AVANT que la porte s'ouvre), et s'il a fallu trancher quant au nombre d'indicateurs de comportement mis à disposition, le résultat est pourtant là.

Avant d'aller plus loin, un accord de langage s'avère nécessaire pour couper court à tout contresens : ayant abordé maintes fois le sujet avec de nombreux lecteurs, l'auteur a remarqué deux visions des choses, purement et simplement contraires! Communiquer mérite, il est vrai, quelques conventions si l'on veut éviter le pire, comme vous allez le constater.

Pour votre serviteur, une porte OUVERTE permet le passage, une porte FERMEE l'interdit.

Toutefois (et ce n'est pas ridicule), pour certains un réflexe plus ELECTRIQUE mène exactement au contraire : un INTER OUVERT bloque le passage alors que FERMÉ il assure la liaison.

On imagine alors les dialogues de sourds qui peuvent découler de tels mélanges...

Aussi, usant honteusement de notre pouvoir de dict-auteur, nous imposerons ici notre perception du système : porte ouverte la modulation passe, porte fermée = silence.

Ce n'est qu'un accord de langage ; et pour ceux qu'il dérouterait, il suffira de se dire que quand on ouvre la porte au bruit, on le laisse passer!

Idem pour une clé qui couperait le système : quand la clé est sur OFF, c'est la FONCTION gate qui est inhibée, donc la modulation «passe» en permanence, le bruit aussi.

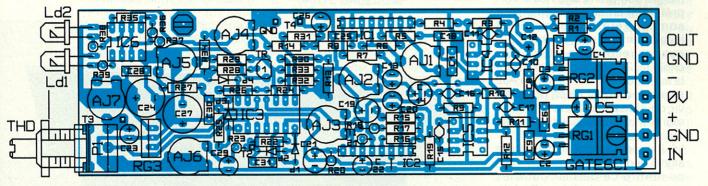

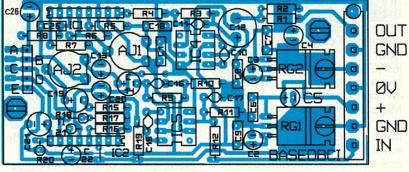

#### 180 R31 C7 100nF 56 100n 11 ╢ <del>†</del>|| 55 % 7815 RG2 7915 Ē RG1 ò ន្តន្ត 22.52 474 8EL 80 898 C27 IC6A LM393 R37 88 55 5 5 <u>ŏ</u> IC3A LM348 S23 88. IC6B LM393 2159 8 $\overline{\Sigma}$ Xão 380 £ 8 R14 6.8K R36 āΔ IC3B . 2호 22 pt 2 <u>5</u> 22pF 100r 2252 ICS NESS34 $\frac{8}{2}$ × R10 ŏ P.19 10분 품 축 C17 22pF 충 Figure 1

#### **CARTE GATE6**

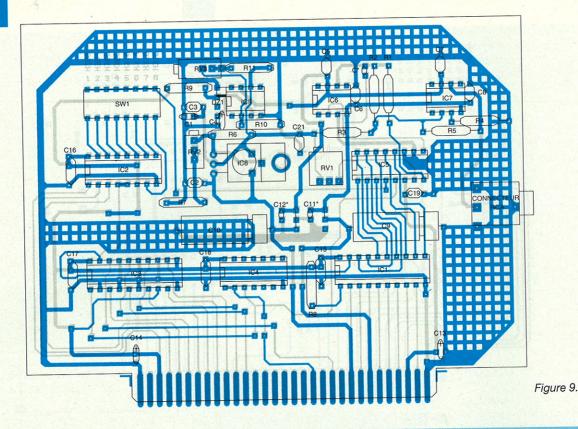

La figure 1 va servir à trois des cartes proposées ici. Les lecteurs qui ont construit les versions de 1988 ne verront de prime abord que bien peu de changements. Il n'y a, en effet, aucune raison pour tout bouleverser d'un montage qui donne entière satisfaction. Pour l'essentiel, les modifications sont de trois ordres.

1- Réduction du temps d'attaque. En studio, les 10 ms des premières versions étaient parfois jugées trop importantes. L'auteur pour sa part n'en a jamais ressenti le besoin, toutefois la modif a été faite et ce temps divisé envi-

ron par 3 (fast).

2- Décalage de la plage de seuil (THD) afin de pouvoir ouvrir à partir de - 55 dBU et non de - 40 comme cela avait été fait. Cette fois, c'est l'auteur qui a été gêné sur certains shunts à rallonge. Il était possible de s'en sortir en augmentant le temps de release, mais il s'avère beaucoup plus utile de décaler le seuil.

10 dB auraient suffi mais nous en avons donné 15 ce qui offre une plage comprise entre - 55 dBU et - 10, et THD à fond bloquant la porte ouverte. Notons au passage que le temps de release maxi est d'environ 8 secondes pour un affaiblissement de 90 dB.

3- Simplifications. Pour des raisons évidentes de place, quelques points ont dû subir des transformations. Par exemple, un ajustable qui permettait de caler parfaitement le RANGE maxi a été remplacé par une résistance, et l'indicateur de réduction de gain a été réduit à deux LED au lieu de huit, mais dans cette version uniquement.

Le choix des deux valeurs ne s'est pas fait sans mal, et il nous a semblé que - 4 dB et - 20 pouvaient convenir. Mais il sera facile de changer ces seuils en modifiant le réseau R35 à R37, et ce en fonction des réglages retenus. Il est évident que si on commande une réduction de gain de 15 dB, l'indication - 20 ne servira pas à grand-chose! Si on choisit le maxi (- 90 dB) il sera bon de déplacer la seconde LED vers - 50 ou - 60 dB, car cet indicateur est très utile pour mesurer, outre la fermeture de porte, le temps de release.

Il est certain que huit points sont beaucoup plus confortables car ils indiquent alors avec précision le réglage de RANGE, mais placer huit LED et un potentiomètre en

Figure 2a

Figure 2b

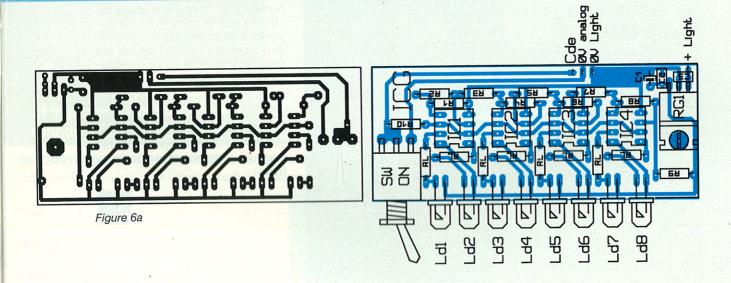

façade alors qu'on ne dispose que de 45 mm n'est pas évident. Un regard sur le dessin de la carte (figure 2) montre que nous n'avons pas gaspillé le «cuivre», et qu'un CI en simple face avec un strap suffit.

Les contraintes mécaniques que nous nous étions imposées (format et fixations compatibles avec les cartes L6N2) ainsi que le changement de tension pour allumer les LED (+ 5V pris sur RG3), interdisaient toute excentricité. En effet, un indicateur à huit LED consomme (toutes allumées) enà plus d'un demi-Ampère. Dans ce cas, il faudra prévoir une source d'alimentation LIGHT indépendante, comme cela avait été fait sur les précédentes cartes Euro-

On verra à ce sujet que sur les autres propositions (cartes 2 à 4) il a été prévu une régulation indépendante pour l'affichage, et qu'il sera autorisé de se prendre sur la

DO ET UNE

régulation + 15V, mais pour UN module seulement (pas plus !). Au delà, la ligne LIGHT sera dissociée.

Si on observe attentivement le schéma, on a vite fait d'isoler la chaîne purement audio, qui va de J2 à J1 en passant par IC5, IC1 et IC4, IC1 étant un VCA 2150A dbx. Ses excellentes performances, son faible prix, son boîtier single in line autorisant des implantations denses et le fait qu'il soit largement distribué, font qu'il reste malgré son grand âge notre VCA préféré. Il en est de même pour son confrère (détecteur RMS idéalement adapté), le dbx 2252, que l'on retrouve en tête de side chain (IC2). On remarquera pour la suite des événements, que AJ2 serait idéalement placé pour servir de Threshold dans un traitement en compresseur. Nous en reparlerons.

Ici, il va servir d'atténuateur sur le signal audio envoyé au 2252 afin de mettre ce dernier dans les conditions souhaitées. En fait, dans notre cas, il sera très faiblement atténuateur puisque le 2252 reste correct jusqu'à plus de 50 dBU et que nous voulons descendre à - 55. Il aurait été possible de le supprimer purement et simplement, mais il aurait fait défaut à ceux qui souhaitent revenir à la gamme de 1988 (- 40, + 5). Nous l'avons donc conservé. Idem pour AJ3 chargé de garantir un gain de 10 dans IC3 b : des résistances de précision auraient pu convenir, mais pour certains tests ou modifications, il est très pratique (par exemple pour piloter un VCA d'un autre type, etc.). Idem encore pour AJ7 destiné à régler la référence haute de THD (seuil le plus bas), et que l'on aurait pu fixer de telle sorte qu'on obtienne + 2,4V sur le point test 3. En fait, seule R27 a été figée afin qu'un maximum de + 560 mV sur test 4 ne puisse être dépassé quand AJ5 (range) est au maximum. 560/6 = - 93 dB pour le 2150. Il est très important de ne pas aller au-delà, car les docs dbx ne précisent jamais les tensions maximales de commande qui peuvent tuer ces VCAs. Aussi, tout ce qu'Alary peut vous assurer, c'est qu'il n'y a pas de problème pour les commandes de - 100 dB à + 40. Donc, il s'est donné pour limites respectivement + 600 mV et - 240 mV. A noter toutefois que dans aucun de nos montages nous n'avons fait donner de gain au 2150, tâche pour laquelle il n'est pas des plus performants (jusqu'à + 10 dB c'est correct, au-delà on dégrade la chaîne audio). Une certitude: + ou - VCC sur la broche de commande (3) et c'est la mort garantie pour un 2150. A éviter

Il faudra donc bien veiller à ne pas bricoler le pont R27+R29/R32 sans discernement et ne pas oublier aussi que IC3c, non inverseur, a un gain de 2.

Le fonctionnement est simple : si la tension négative produite par

Contrairement à ce qui avait été décrit dans le n° 496, la carte est ici prévue pour des modulations monophoniques. C'est en effet l'usage le plus courant en insertion sur une console, pour traiter par exemple chaque micro reprenant une batterie, ou encore des choristes. Une adaptation en stéréo serait aisée : il suffirait de doubler la chaîne audio et de prévoir un mélangeur au gain unité avant d'attaquer AJ2, mais il serait également possible de faire le mélange à l'entrée de IC3. Cette

IC2 (pour les seuils inférieurs à son point de basculement soit environ - 13 à - 15 dBU entre C19 et R15), inversée et multipliée par 10 dans IC3b est supérieure au seuil déterminé par P1, une tension positive +VCC traverse la diode D3, est dosée par AJ5 en fonction de l'atténuation souhaitée et va commander IC1 en atténuateur : la porte est alors fermée. Mais TR1 va ralentir le processus par la décharge de C27 dans R34/AJ7 (c'est le réglage de RELEASE). Si sur 3 de IC3 la tension est inférieure au seuil fixé par P1, c'est qu'une modulation supérieure au seuil est reconnue, alors il faut ouvrir la porte au plus vite. La tension négative présente en 1 de IC3 traverse D4 et fait conduire TR1, en même temps qu'en sortie de D3 on passe à 0 V : tout va donc dans le même sens pour obtenir 0 V sur test 4, soit un gain unité pour IC1. La porte est ouverte. Pendant ce temps, C27 se recharge pour le prochain RELEASE, etc.

méthode serait à réserver à ceux qui souhaiteraient coupler deux cartes, sans autres modifications que ne conserver qu'une seule side chain, un seul indicateur (ou en profiter pour s'offrir quatre valeurs différentes) et relier ensemble les broches de commandes des VCA. On pourrait aussi supprimer un jeu de régulateurs, mais à ce stade il serait plus raisonnable de dessiner une carte spéciale, ne pensez-vous pas ?

La réalisation pratique se limite à reproduire le circuit dessiné figure 2 et à l'implanter correctement.

#### Réglages

La méthode de réglage est la suivante :

1 - Ne placer sur supports que IC1, IC4 et IC5, et porter à 0 V la commande de IC1, puis chercher la distorsion minimum au moyen de AJ1. Vérifier que le gain de l'ensemble est de 1, à +/- 1 dB. 2 - Retirer IC1 et le pont cde/0 V,

et placer IC2 et IC3. Injecter une modulation à 1 kHz de - 55 dBU, mesurer sur test 1 et ajuster AJ2 pour obtenir - 240 mV.

3 - Mesurer ensuite en test 2 et caler AJ3 pour arriver à + 2,4 V . 4 - Obtenir + 2,4 V également en test 3 au moyen d'AJ7.

5 - Mettre RANGE au maxi (côté R27), RELEASE fast (côté R34), ATTACK fast (côté R23) et P1 à mi-course.

Vérifier que suivant la modulation on obtient 0 V sur 3 de IC1 quand le niveau dépasse le seuil (P1 à mi-course donne un seuil de - 30 dBU environ). Injecter donc par exemple 775 mV (0dBU) pour mesurer 0 V, puis couper la modulation et vérifier que la tension n'atteint pas + 600 mV en 3 du support de IC1.

6 - IC1 peut alors être implanté sans risque, mais profitez en encore pour tourner AJ4 dans l'auteur, vous avez implanté un peu trop vite et monté par étourderie un 547 au lieu d'un 557 en TR1, les tests de RELEASE ne fonctionneront pas! Inutile de mettre en place le VCA pour s'en assurer, un multimètre suffit. Idem si vous mesurez + 4 V alors que vous attendez au maxi 0,6 V, si c'est sur la broche 3 d'un support de VCA, il est préférable que ce dernier ne soit pas engagé.

#### CARTE BASEDBCI

Traduction: BASE = carte d'étude, DB = pour dbx, CI: c'est un circuit imprimé. Ces noms tordus et porteurs d'une pseudo extension interne ont une raison simple: éviter tant que faire se peut que les .bak se croisent les doigts avec les schémas! En effet, si on donnait par exemple

BASEDBX.SCH pour le schéma et BASEDBX.CIR pour le circuit imprimé, sur une même disquette sans sous-répertoire il n'y aurait plus qu'un bak et, bien évidemment, pas celui qu'il faudrait.

En cherchant bien, on trouvera sur le côté composants des cartes le nom du fichier sans extension à télécharger : par exemple sur la figure 2, on peut lire «GATE6C» (sous RG1).

La notion de «BASE» a été introduite par votre serviteur dans ERP en janvier 1989, et ce à la demande de nombreux lecteurs qui souhaitaient manipuler au plus vite – à leur idée – autour de circuits particuliers, sans devoir pour cela développer des cartes d'évaluation.

BASEDBCI – figure 3 – vient s'ajouter à la liste. Un rapide coup d'œil permet de constater qu'il s'agit d'une coupe franche dans la figure 2. En observant le schéma figure 1, on découvrira les 5 points d'accès reportés sur deux connecteurs en parallèle :

A: cde (à gauche de R8)

B:0V

C: -VCC = -15V reg

D : sortie 7 du 2252 E : +VCC = + 15V reg

Cette formule réduit considérablement le temps qu'il faut pour mettre en place les éléments irréductibles d'un système à VCA + détecteur RMS dbx, et rend plus confortable l'étude du traitement en continu à proprement parler.

l'autre sens. Envoyer du 0 dBU. puis couper l'injection: il devrait falloir environ 8 secondes pour atteindre la tension maxi (+ 560 mV). Tourner alors AJ5 pour que Ld2 s'éteigne tout juste. On devrait alors mesurer environ + 120 mV sur 3 de IC1. Si vous trouvez 130 ou 110 c'est bon : les diviseurs de tension R35/36/37 sont réalisés avec des valeurs approximatives conduisant à des écarts tout à fait tolérables. 6 mV par dB, ne l'oubliez pas ! Si la LED - 20 s'allume pour - 21 ou -19 il n'y a pas de quoi faire un drame, surtout si ce n'est qu'un «passage» vers - 70 ou -90 dBU...

Cette méthode est à retenir pour TOUT ce qui va suivre. Avouez qu'elle est simple et prudente? Surtout ne jamais faire l'impasse qui consiste à dire: «cette étape ne fonctionne pas, mais je vais quand même passer à la suivante».

Chercher l'erreur. Souvent c'est une grosse bêtise : si, comme

Figure 3a

Figure 3b

Si de plus on a pris soin d'implanter au mieux une telle «base» de travail, rien n'interdit ensuite de la considérer comme un sous-ensemble prêt à l'emploi (nous allons le démontrer), ou comme un élément de dessin à incorporer presque tel quel dans une carte plus importante (voir figure 2).

Le serveur ERP permettant de télécharger ces dessins (LAYO), chacun peut alors gagner un temps précieux et disposer d'un fichier original - triturable à souhait - quelques minutes seulement après avoir lu ces lignes!

C'est magique...

Pour certaines applications, AJ2 pourra avantageusement être remplacé par trois cosses afin de libérer totalement l'envoi à IC2 et rendre possible (entre autres) des tests de prélèvements pré ou post VCA. Par ailleurs, si vous avez un peu d'humour et de curiosité, pourquoi ne pas tenter les effets directs d'une liaison sans intermédiaire entre la sortie de IC2 et cde de IC1 ? Attention : au labo, pas avec 10 kW de puissance dans le dos! Le repérage des composants est toujours conforme à la figure 1.

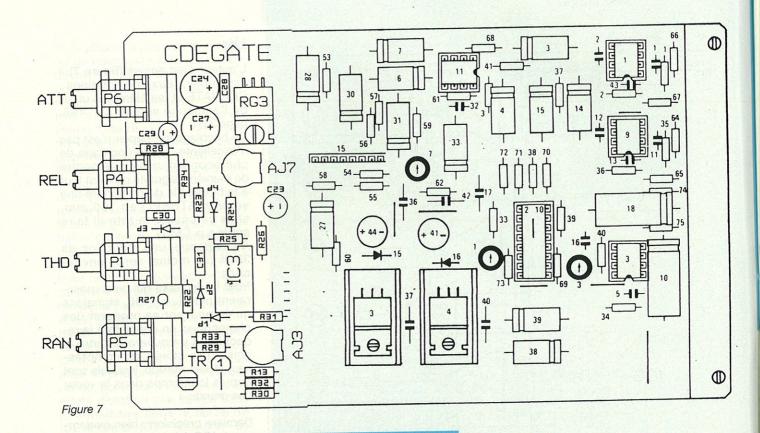

#### CARTE CDEGATE

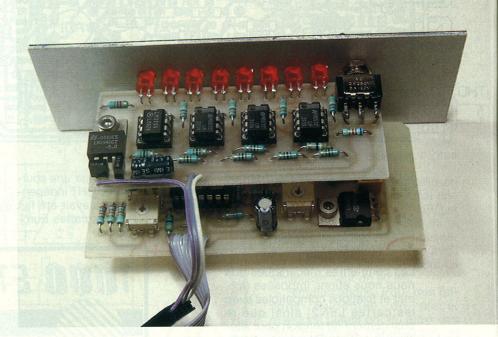

Ce module va typiquement exploiter BASEDBCI. Comme le montre la figure 4, il porte tous les composants de la «side chain» qui avaient été exclus dans la BASE, mais propose cette fois en façade les réglages utiles, et ce de la même façon que la précédente version Europe.

Une photographie présente d'ailleurs un ensemble monté sur une face avant d'essai habillée d'un morceau de lexan référencé

jadis NGSE.

A l'évidence, on constate que le dessin est préparé pour un bac Europe 3 U, et qu'il suffirait de l'étendre sur la droite pour le finaliser.

Un raccordement par nappe est prévu pour lier cette carte à BASEDBCI, ce qui offre la possibilité d'inclure l'ensemble dans un rack 3U classique, de profondeur 160 mm, et d'y placer jusqu'à 10 pièces plus les alims ! Inutile d'insister sur l'intérêt d'un tel objet en studio.

Mieux encore, le couplage des deux cartes (plus l'indicateur que nous verrons ensuite), permet aussi d'inclure directement dans une console un module complet dans un espace de 50 x 100-

Figure 4a

Figure 4b

x 75 mm², soit l'équivalent de trois boîtes de cassettes audio placées côte à côte.

La procédure de réglage est rigoureusement identique à celle de GATE6, à un détail près : afin de ne pas bouleverser la nomenclature, AJ4, 5 et 6 seront à renommer P4, P5 et P6.

Pour mémoire, P4 et P6 = fast à droite, P1 = - 55 dBU à gauche, et RANGE maxi (P5) = - 90 dB à droite.

#### ICG. INDICATEUR 8 POINTS

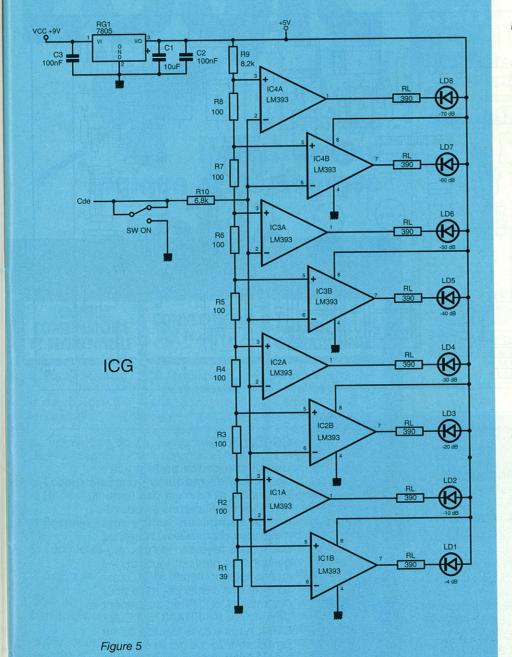

Le schéma de ce nouvel indicateur est visible figure 5. Il n'y a pas grand-chose à dire sinon qu'il est totalement compatible avec les anciennes versions NGSE (et LCSE), qu'il utilise cette fois des LM393 (sorties collecteur ouvert), et dispose de sa propre référence + 5 V. Le calcul du réseau R1 à R9 a été fait de sorte qu'il soit possible de mesurer directement sur la ligne cde (sans ampli intermédiaire).

Nous en verrons les effets «secondaires», mais passons tout d'abord à la figure 6. Quatre points de liaisons sont nécessaires : cde , 0 V analog et +/0 light. Les deux premiers sont à raccorder normalement au second connecteur de BASEDBCI. Pour les deux autres (light), deux cas sont à considérer :

1- On ne construit qu'un seul module. Il est alors permis de relier 0 analog à 0 light, et + light au + 15 V régulé. Le second connecteur dispose de tout ce qu'il faut. 2- On envisage un bataillon de gate(s), et il faut alors dissocier la section LIGHT et prévoir une alimentation séparée. Il n'est pas nécessaire de dépasser 9 V non régulés, puisque cette fois on régule à + 5.

L'assemblage mécanique de ICG sur CDEGATE se contente d'une entretoise MF15 + deux rondelles ép 1 mm, dont une vis profite pour plaquer RG1 sur la carte

ICG.

#### Idée

L'auteur s'est amusé (figure 7) à assembler deux implantations : CDEGATE et les éléments utiles de l'ancienne version (N° 496, page 31).

Ce bricolage sur papier n'est pas d'excellente qualité (montage de photocopies), mais il démontre de manière flagrante qu'il est tout à fait possible de construire une version STEREO en 160 mm, sans se casser la tête ni faire appel aux CMS!

A l'évidence, une réduction de 30 % (au moins) serait encore aisée.

Pour les lecteurs qui ne disposeraient pas du n° 496, signalons qu'ils peuvent se procurer des photocopies en contactant la rédaction. Il y trouveront, outre le noise-gate stéréo, un compresseur stéréo Europe, lesquels sont depuis longtemps dans la «cour des grands».

Dernière précision : bien évidemment, ICG (réseau à re-calculer) est adaptable sans problème au compresseur.

NOTA: page 41 du n° 496 il faut corriger =

R58 = 180 Ohm (et non kOhm) C30 = 470 pF (et non MF enfin IC12 à 13 = TL071 (et non TL075).

Figure 6b

#### NOMENCLATURE GATE6

Résistances

$R1 = R4 = R8 : 10 \Omega$

$R2 = R9 \text{ à } R12 = R24 : 10 \text{ k}\Omega$

$R3 = R7 = R30 = R32 : 22 \text{ k}\Omega$

R5: 3,3 k $\Omega$

$R6 = R31 : 47 \Omega$

R13: 180  $\Omega$

R14: 6,8 k $\Omega$

R15:33 k $\Omega$

R16:22  $\Omega$

$R17 = R18 : 10 M\Omega$

R19: 470 k $\Omega$

$R20 = R33 : 1k\Omega$

R21:1,5 M $\Omega$

R22: 220  $k\Omega$

R23:390  $\Omega$

$R25 = R28 : 2,2 k\Omega$

R26:68  $k\Omega$

R27: 5,6 k $\Omega$

$R29 = R35 : 39 k\Omega$

$R34:100 \Omega$

R36: 820 Ω

R37: 220  $\Omega$

$R38 = R39 : 330 \Omega$

**Ajustables Phier**

$AJ1 = AJ3 = AJ4 = AJ7 : 47 k\Omega$

AJ2:  $10 \text{ k}\Omega$

AJ5:  $100 \text{ k}\Omega$

AJ6: 22 k $\Omega$

#### Potentiomètre Sfernice

P1: 22 kΩ A P11

#### Semiconducteurs

D1 à D4: 1N4148

IC1: dbx 2150

IC2: dbx 2252

IC3: LM348

IC4 = IC5 : NE 5534

IC6: LM 393

RG1:7815

RG2: 7915

RG3: 7805

TR1: BC557

LD1: LED verte; LD2: LED rouge

Connecteur NFOM 7 points.

#### **Condensateurs**

$C1 = C6 \text{ à } C9 = C18 = C25 = C28 = C30 = C31 : 0.1 \mu F MILFEUIL$

C2 à C5 : 22 μF 25V vertical C10 = C11 = C15 à C17 : 22 pF

C12 = C27 : 100 µF vertical

C13 = C14 = C13 à C23 : 10 µF 25V vertical

C24: 220 uF 25V vertical C26 : C29 = 2,2  $\mu$ F 25V vertical

#### CONCLUSION

Ces quatre cartes portent votre collection de modules pour la sono à 23, et ce n'est pas terminé. Nous continuerons à vous offrir de temps en temps nos meilleures «trouvailles». N'hésitez pas à nous faire part de vos suggestions, en oubliant toutefois les inserts téléphoniques SVP : c'est un sujet très demandé, mais pour des raisons évidentes de respect des «lois» de FRANCE TELE-COM, nous avons décidé de ne jamais aborder ce genre de montage. Lorsque nous avons besoin d'un insert, on sort le Néophone homologué! Signalons (sous réserves) que la société E2A a développé jadis une petite carte insert pour les QUEST etc. Il est peut-être possible de se la procurer en tant que module?

Jean Alary

Remerciements au Studio du Moulin de Poustagnacq - 40990 Saint Paul les Dax, pour ses remarques judicieuses et constructives.

# Transmission vidéo sur paire torsadée

Dans les années 80, la réception des programmes de TV étrangers, sauf dans les régions frontalières, relevait des hasards de la propagation. Le téléspectateur moyen, dans le meilleur des cas, avait à sa disposition six programmes en principe différents. Ces programmes sous la forme de signaux HF, disponibles simultanément aux bornes de l'antenne, étaient acheminés au téléviseur via un câble coaxial. Le plan de fréquence taillé dans les bandes I, III, IV et V compte environ 60 canaux et seul 10% du plan est occupé par les six programmes définis précédemment. L'ère de la transmission par satellite a considérablement modifié ces données et l'on peut disposer couramment de plusieurs dizaines de programmes. Dans les lignes qui suivent, nous allons voir que la distribution des signaux dans les collectivités peut être envisagée selon des principes bien différents.

#### De très nombreuses sources audio-vidéo

Les sources audio-vidéo dont on peut disposer aujourd'hui sont d'origine diverse : diffusion hertzienne dans la bande UHF, réception directe par satellite, ou production locale : caméra ou magnétoscope. Dans le cas des immeubles d'habitation, ces caméras ou «chaînes locales» sont destinées soit à la télésurveillance soit à des portiers vidéo. Dans le cas des hôtels, les magnétoscopes sont affectés à la diffusion de films.

Disposer de plusieurs dizaines de sources au niveau d'une tête de réseau ne présente donc aucun caractère exceptionnel. La question que nous nous posons alors est : quels sont les procédés de distribution que l'on peut envisager?

Dans les petites et moyennes collectivités, le procédé le plus répandu, celui que chacun d'entre nous connaît, est la distribution par câble coaxial et nous allons nous intéresser brièvement à ce type de télédistribution pour en connaître ses avantages, ses inconvénients et finalement ses limites.

Nous aborderons ensuite un second procédé de distribution, sur paire torsadée.

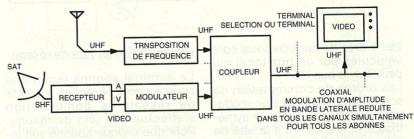

#### DISTRIBUTION PAR VOIE HERTZIENNE

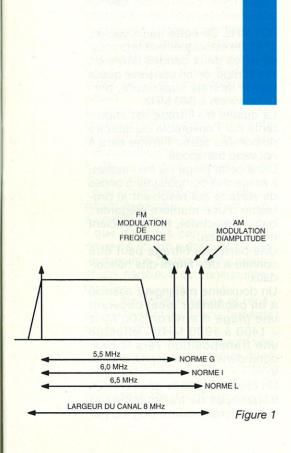

Le signal vidéocomposite accompagné d'un signal audio a un spectre représenté par le schéma de la figure 1.

L'écart porteuse image-porteuse son est fonction de la norme et vaut : 5,5-6,0 ou 6,5 MHz. La modulation est du type modulation d'amplitude et pour réduire l'occupation spectrale l'une des deux bandes latérales est atténuée.

Le cas de la transmission audio est simplifié au maximum; une transmission stéréophonique, par deux sous-porteuses, ou en NICAM, ne change en rien les résultats suivants.

Dans le cas de la figure 1, seule la bande latérale supérieure est conservée et la modulation est dite modulation d'amplitude à bande latérale réduite.

La sous-porteuse audio est modulée soit en amplitude soit en fréquence.

Pour tenir compte du résidu de bande latérale inférieure vidéo et de la bande latérale supérieure dues à la modulation audio, la largeur du canal a été fixée à 8,00 MHz.

Ce premier chiffre est important car il va nous faire découvrir la limitation du nombre de canaux.

Dans les bandes UHF IV et V, on dénombre 48 canaux de 8 MHz numérotés de 21 à 69.

Pour le canal 21, la porteuse vision vaut 471,25 MHz.

Si l'on compte six canaux dans la bande UHF III, on dispose de 54 canaux disponibles simultané-

Ce chiffre peut paraître largement suffisant dans la plupart des cas, mais l'exploitation simultanée des 54 canaux est, pour des raisons que nous allons découvrir, impensable et impossible.

En théorie, on admet que toute l'information relative aux signaux vidéo et audio se situe à l'intérieur du canal de 8 MHz.

Dans la pratique, ceci est faux et dépend surtout de la qualité du filtrage. On admet donc que les canaux voisins peuvent être légèrement pollués par le canal utile. Pour éviter toute interférence par voie hertzienne en UHF, on utilise un canal sur trois ou un canal sur deux.

Si, aux 54 canaux précédents, on applique la même règle, on ne dispose plus que de 27 canaux. Par ailleurs, les canaux utilisés en UHF pour acheminer les émissions jusqu'à la tête de réseau ne peuvent en général être réutilisés directement dans le système de télédistribution.

Une émission reçue sur le canal 22 ne peut être redistribuée sur le canal 22; une telle pratique se traduirait inévitablement par un écho. Il existe d'autres restrictions dues plus particulièrement aux modulateurs et à leur principe de fonctionnement.

Nous allons passer en revue assez rapidement ces limitations.

#### Limitations dues aux modulateurs

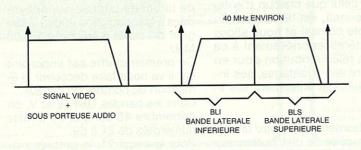

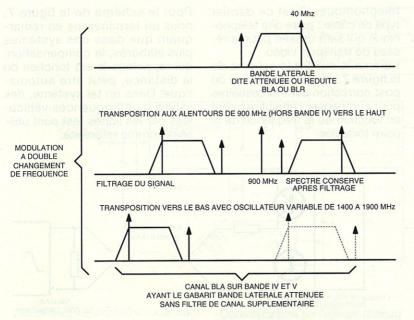

Le schéma de la figure 2 donne l'aspect d'un signal vidéo en bande de base accompagné de la sous-porteuse audio et l'aspect de ce même signal transposé par exemple à 40 MHz.

Si la transposition s'effectue par exemple dans la bande UHF, on a le spectre d'une modulation d'amplitude classique et non celui d'une modulation d'amplitude à bande latérale réduite.

Dans ces conditions, lorsqu'un signal est transmis sur le canal N, le canal N-1 est inutilisable et il est évident qu'un filtrage à cette fréquence est extrêmement déli-

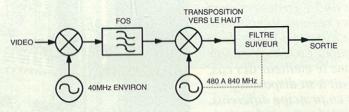

Une première solution est donnée par le synoptique de la figure 3. sites étant éloignés d'environ 40 MHz du signal utile, leur filtrage est rendu plus aisé. Bien que cette structure ne soit pas idéale, c'est elle, pour son compromis prix/performance, qui est la plus répandue. Sa mise en œuvre exige la présence d'un filtre de

Figure 3

Comme précédemment, figure 1, le signal vidéocomposite module en amplitude une porteuse au voisinage de 40 MHz.

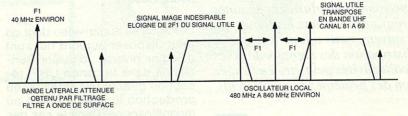

En sortie du modulateur, on récupère le spectre de la figure 2. L'opération suivante consiste à filtrer le signal. Pour cela, on utilise un filtre à ondes de surface qui permet de ne conserver qu'une seule des bandes latérales. Dans notre cas - figure 4 - la bande latérale inférieure est conservée.

canal s'intercalant entre le modulateur et le réseau. Le synoptique de la figure 3, par son filtre suiveur, reste malgré tout délicat dans sa mise en œuvre et l'on cherche donc une autre solution. La dernière solution est illustrée par les différents spectres de la figure 5.

Une bande latérale inférieure, en VHF aux alentours de 40 MHz, est transposée vers le haut grâce un oscillateur à environ

Figure 4

Cette bande latérale est transposée vers le haut grâce à un mélangeur recevant un oscillateur local ajustable de 420 à 840 MHz environ.

Le résultat de la transposition nous donne deux bandes latérales et l'oscillateur alors que seule la bande latérale supérieure constitue le signal utile.

Lorsque la distribution est effectuée sur le canal N, le canal N-11 est brouillé par la bande latérale inférieure et les canaux N-5 et N-6 peuvent être perturbés par l'oscillateur local. Les signaux para900 MHz. De cette transposition, il résulte classiquement la porteuse et les deux bandes latérales. Par filtrage, on ne conserve que la bande latérale supérieure, porteuse vision à 940 MHz.

La qualité du filtrage est importante car l'ensemble du spectre disponible après filtrage sera à nouveau transposé.

Dans cette plage de fréquences, il existe des composants à ondes de surface qui résolvent le problème d'une manière élégante : bonne sélectivité, fort coefficient de surtension.

Une partie du filtrage peut être confiée à des filtres dits hélicoï-

Un deuxième mélangeur associé à un oscillateur local couvrant une plage d'environ 500 MHz – 1400 à 1900 MHz – effectue une transposition vers le bas, donc dans les bandes UHF IV et

Un choix astucieux des diverses fréquences de transposition et une programmation du PLL par

Figure 2

Figure 5

microcontrôleur permet la sélection directe des canaux 21 à 69. Avec un oscillateur couvrant 950 MHz à 1900 MHz, le modulateur peut couvrir les bandes III, IV et V, les canaux S et les canaux interbande : vaste programme.

Dans cette configuration, un filtre de canal est inutile. Seul un filtre passe-bande, bande IV et V, peut éventuellement améliorer la réponse spectrale en bande III. Même si la structure de ce modulateur semble plus contraignante et plus coûteuse que les configurations présentées antérieurement, elle doit être préférée pour la meilleure pureté spectrale.

Cette configuration élimine l'emploi de filtre de canal ou multicanal et évite tout problème de stock sur des filtres très spécifiques.

En contrepartie, la pureté spectrale est en principe suffisante dans les bandes IV et V pour utiliser la totalité des canaux.

En guise de conclusion et de résumé, nous retiendrons :

- que le nombre de canaux disponibles en bandes IV et V est limité à environ 50;

- que pour des capacités supérieures à 50, on a obligatoirement recours aux canaux VHF bande let aux canaux S ou canaux interbande :

- que les amplificateurs et répéteurs devront avoir une linéarité exceptionnelle;

- que les modulateurs auront une pureté spectrale obtenue avec des modulateurs à double changement de fréquence dont le principe a été décrit précédemment.

Dans ces conditions, un système de télédistribution dans une petite collectivité pourra donner des résultats acceptables.

Par résultats acceptables, on entend absence d'échos, de moirages et, en général, un rapport signal sur bruit supérieur à 50 dB. Le signal est acheminé jusqu'à l'usager. On prendra toutes les précautions pour que le niveau du signal reste utilisable à l'arrivée chez l'usager et on s'en tiendra à une norme définissant parfaitement les limites à respecter. Finalement, on remarque, et nous arrivons enfin aux points intéressants, que la transmission de signaux audio et vidéo en UHF et MABLR - modulation d'amplitude à bande latérale réduite - est très contraignante.

Les contraintes sont d'ordre technique et principalement dues aux fréquences élevées. Ces contraintes ont bien évidemment une influence directe sur le coût d'une installation.

Le coût d'une telle installation est dû, d'une part, au matériel, matériel sophistiqué mettant en jeu des techniques UHF, et, d'autre part, au personnel, nécessairement qualifié pour maîtriser ces techniques, chargé de l'installation et de la maintenance d'un tel réseau de distribution.

Lorsqu'un réseau est peu chargé, cas des six chaînes nationales, la transmission et la distribution en UHF reste la solution la moins coûteuse.

On notera enfin que les réseaux de distribution en UHF vieillissent en général mal et que les mises à niveau doivent être effectuées régulièrement.

Pour des réseaux plus chargés, la limite, nous le verrons, est assez difficile à définir, un autre mode de transmission, transmission en bande de base, se présente comme une solution élégante répondant au problème posé.

#### TRANSMISSION EN BANDE DE BASE SUR PAIRE TORSADÉE

A partir de l'énumération des défauts de la transmission en UHF on cherche à établir les spécifications d'un réseau plus performant.

Pour éliminer tous les problèmes dus à l'emploi des UHF, le signal sera donc transmis en bande de base.

La structure du système de transmission et de distribution se conçoit simplement à partir de cette première règle.

Qui dit bande de base dit aussi un seul et unique signal à un instant donné. Ceci ne pose pas d'inconvénient majeur si on admet que le téléspectateur, à un instant donné, ne peut regarder qu'un seul et unique programme.

Le média n'étant capable de transporter simultanément qu'un seul canal, la sélection du programme s'effectuera donc à la source : à la tête de réseau.

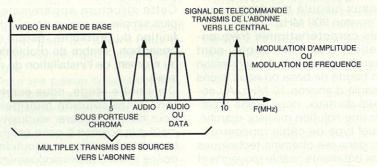

Le spectre du signal transmis sur le média, de la tête de réseau vers l'abonné, aura donc l'allure donnée à la **figure 6**.

Figure 6

Sur cette figure, on a la superposition de quatre signaux principaux:

- le signal vidéo ;

- une première sous-porteuse modulée par le signal audio ;

- une seconde sous-porteuse modulée par un signal audio ou des données.

Ces trois premiers signaux sont transmis de la tête de réseau vers l'abonné.

Le quatrième signal est une sousporteuse modulée par les signaux de télécommande de l'abonné vers le terminal.

Sans entrer dans le détail du système que nous allons découvrir progressivement, on en comprend intuitivement le fonctionnement.

L'utilisateur, abonné ou téléspectateur, agit sur sa télécommande. comme dans le système classique, pour sélectionner le programme.

Cette information est interprétée par le récepteur et «remonte» jusqu'à la tête de réseau sur une sous-porteuse aux environs de 10 MHz

La tête de réseau exploite l'information, la décode et envoie sur le média le programme vidéo + audio demandé.

Tout se passe comme si le récepteur de télévision était découpé en deux parties distinctes éloignées l'une de l'autre.

Le sous-ensemble récepteur est disposé à la tête de réseau et les sous-ensembles vidéo chez l'abonné.

Cette structure résoud d'emblée tous les problèmes de surcharge de réseau. La capacité maximale de programmes pouvant être transmis sur le média ne dépend plus ni du média lui-même ni du type de transmission. Avec ce procédé, cette notion n'a plus de sens et n'existe plus.

#### Choix du média

Dans un réseau de distribution UHF, le média est un câble coaxial capable de véhiculer des signaux jusqu'à des fréquences d'environ 900 MHz.

Les caractéristiques fréquentielles d'un tel câble sont luxueuses pour la transmission en bande de base où nous avons besoin d'environ 10 MHz. Au coaxial douteux, nous allons préférer une solution meilleur marché. Quel type de câble rencontre-ton dans les chemins techniques des bâtiments : câble moyenne et basse tension, mais aussi câble

téléphonique. C'est ce dernier type de câble : paire dite téléphonique qui sera utilisée pour le réseau de transport vidéo.

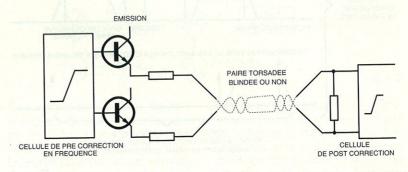

Comme le montre le schéma de la figure 7, des cellules de pré ou post correction sont nécessaires pour compenser l'affaiblissement en fonction de la fréquence de la paire torsadée.

Pour le schéma de la figure 7, nous en terminerons en remarquant que dans des systèmes plus élaborés, la compensation, qui rappelons-le est fonction de la distance, peut être automatique. Dans un tel système, des salves multifréquences véhiculées par les lignes test sont utilisées comme référence.

Figure 7

Une liaison comme celle représentée à la figure 7 pourra s'effectuer sur des distances de plusieurs centaines de mètres, voire milliers de mètres.

Ces distances permettent de résoudre quasiment tous les cas de transport dans les petites et moyennes collectivités.

La correction en fréquence sera soignée dans la bande vidéo, environ jusqu'à 5 MHz, mais la réponse en fréquence n'a plus de véritable intérêt au-delà.

Ceci sera particulièrement vrai si l'on utilise la modulation de fréquence pour les trois sous-porteuses au-delà de 5 MHz.

Une simple paire torsadée répond donc, pour un modeste coût, au problème du choix du média, pour ce réseau.

A ce stade de la définition du réseau, on peut déjà entrevoir les différentes variantes. La paire torsadée étant un support à faible coût, on peut imaginer que chaque abonné reçoit quatre paires parfaitement dédiées : vidéo, audio 1, audio 2 et télécommande.

Cette structure apparemment plus simple, au moins pour la définition du problème, risque de poser bon nombre de problèmes au moment de l'installation du réseau.

Dans notre étude, nous écarterons cette solution multipaire pour nous consacrer exclusivement à la solution à paire unique. La solution multipaire a toutefois donné lieu à des développements industriels.

Nous en savons désormais suffisamment pour entrer dans le détail d'un tel réseau et découvrir quelques subtilités de son fonctionnement.

#### Le terminal abonné

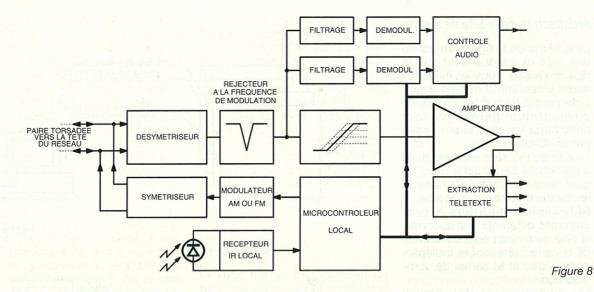

Le terminal abonné est en fait le récepteur situé chez l'usager ou, si ce terme vous convient mieux, le téléspectateur ou encore foyer. Le synoptique de ce terminal est donné à la figure 8.

Le signal reçu est préalablement désymétrisé et on place en sortie un filtre réjecteur calé sur la sousporteuse du signal de télécommande. En sortie de ce filtre, on récupère le signal vidéocomposite et le ou les sous-porteuses audio.

Après élimination des sous-porteuses audio et compensation en fréquence du câble, on obtient un signal vidéocomposite codé PAL ou SECAM.

Après filtrage et démodulation, on récupère les signaux audio. Il est clair que les fonctions mises en œuvre dans cette chaîne sont simples et ne posent aucun problème technique; ces solutions sont à faible coût.

Un microcontrôleur local gère le sous-système terminal abonné. Sa fonction est simple. Il est principalement chargé du décodage des informations issues de la télécommande de l'abonné.

Il effectue le tri des informations : contrôle local, son + ou son -, par exemple, ou ordre de commutation de source.

Les ordres de contrôle local sont véhiculés par un bus local qui peut être le bus I2C.

Les ordres de commutation de source sont envoyés à un modulateur FM ou AM puis à un symétriseur et finalement à la tête de réseau via la paire torsadée.

Sur le schéma synoptique de la figure 8, on remarque finalement un bloc noté télétexte.

Ce bloc permet bien sûr d'exploiter le télétexte si cette fonction est inexistante dans le téléviseur ou moniteur associé mais il permet surtout deux facilités supplémentaires.

Le bloc télétexte peut être utilisé comme générateur de caractères. Il assure alors toutes les fonctions d'affichage lors du dialogue abonné-terminal abonné. Ex: affichage sur l'écran du message: vous avez demandé le canal 39, veuillez confirmer, etc. Ce bloc pourra être utilisé pour transmettre des informations numériques – hors télétexte – de la tête de réseau vers le terminal abonné.

Cette caractéristique, très importante, a d'énormes conséquences sur les fonctionnalités du système et fera l'objet d'un développement ultérieur.

Le terminal abonné est un ensemble simple ne faisant appel qu'à des techniques de basse fréquence. Cette caractéristique est rassurante quant à son coût, sa fiabilité et sa maintenance aisée.

Le seul inconvénient du système est l'impossibilité de visionner un canal X en enregistrant le canal Y. Le faible coût de la liaison peut permettre de remédier à ce défaut en attribuant deux paires – deux liaisons – à l'abonné qui le souhaite.

#### Commutation en tête de réseau

Le terminal abonné reçoit une source parmi N reçues à la tête de réseau. La commutation s'effectue à la tête de réseau. Pour que chaque abonné soit indépendant, un système de commutation est dédié à chaque abonné.

de, le démoduler et extraire l'information.

L'information est décodée par un microcontrôleur qui aura comme charge, non seulement la gestion du commutateur, mais aussi le dialogue avec un PC de gestion centralisée.

A ce stade de la description du réseau, il est clair que tous les

Figure 9

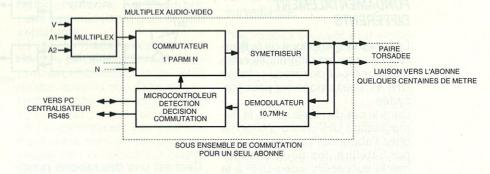

Le schéma synoptique de la figure 9 donne l'essentiel du sous-ensemble de commutation chargé de deux actions essentielles.

La première chose est d'assurer la commutation. On dispose donc d'un commutateur analogique recevant autant de multiplex audio + vidéo qu'il y a de programmes à distribuer.

Ce signal est transmis à un circuit symétriseur qui délivre deux signaux symétriques adaptés à la ligne.

Pour les paires torsadées utilisées dans ce type d'application l'impédance caractéristique vaut quelques centaines d'ohms.

La deuxième fonction du sousensemble de commutation consiste à recevoir le signal de sous-porteuse de télécommansous-ensembles mis en jeu font appel à des technologies banalisées : vidéo, microcontrôleur et des fréquences inférieures à 12 MHz.

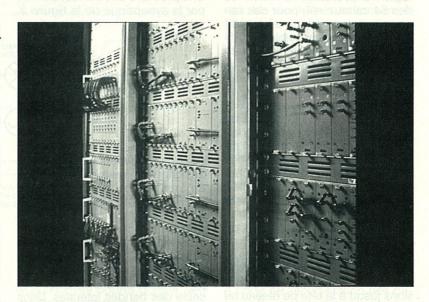

Malgré cela, et comme pour un réseau UHF, la gestion par exemple d'un réseau d'une centaine d'abonnés fera appel à un matériel assez conséquent.

Même si ceci ne semble pas avoir d'importance, on ne perdra pas de vue qu'il s'agit d'un réseau de distribution, donc de matériel dit professionnel et non de quelques cartes enfichées dans un PC.

Pour cette raison, le choix du réseau : coaxial ou paire torsadée ne dépend pas seulement du nombre de programmes à transmettre et ne peut pas être réduit à un seul et unique problème de coût.

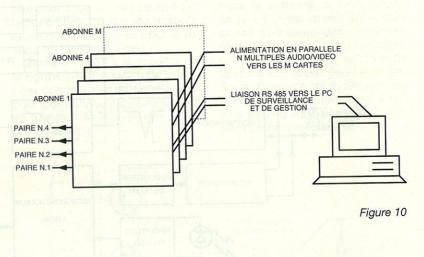

#### Architecture de la tête de réseau

Le schéma de la figure 10 donne une idée de ce que peut être la tête de réseau. Tous les multiplex audio-vidéo sont envoyés simultanément à toutes les cartes de commutation gérées par leur contrôleur local et supervisées par le PC central.

Le rôle du PC sera examiné dans un prochain paragraphe dans lequel nous tenterons d'examiner les fonctionnalités du système.

Si le réseau distribue N programmes différents à M abonnés, la tête de réseau sera constituée de N cartes réalisant le multiplex audio-vidéo et M cartes de commutation.

Les signaux seront véhiculés sur M paires torsadées et reçues par M terminaux dédiés aux M abonnés.

Ce raisonnement ne prend pas en compte le cas spécial des abonnés ayant deux lignes, mais il est clair que des cas spéciaux ne posent pas de problèmes particuliers

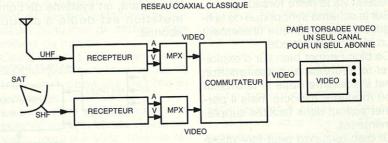

#### DEUX RÉSEAUX FONDAMENTALEMENT DIFFÉRENTS

Le schéma synoptique de la figure 11 montre les différences entre les deux types de réseau : réseau UHF et réseau vidéo sur paire torsadée.

Dans le cas du réseau UHF, la démodulation UHF/vidéo s'effectue chez l'abonné. Pour la réception par satellite, les deux changements successifs vidéo-UHF à la tête de réseau et UHF-vidéo chez l'abonné sont en principe inutiles et dégradent le signal.

Le câble coaxial est unique, par division de puissance successive, la même source délivre les signaux UHF à tous les abonnés. La sélection de la source à démoduler s'effectue finalement chez l'abonné.

Dans le réseau vidéo sur paire torsadée, chaque abonné est propriétaire de sa ligne qui, à un instant donné, ne véhicule qu'un et un seul signal.

La démodulation s'effectue à la tête de réseau. Le réseau ne traite que des signaux vidéo, le terminal est réduit à sa plus simple expression : un moniteur.

Si le schéma de la figure 11 montre que les deux réseaux sont très différents, elle montre aussi que le remplacement d'une installation existante par une autre est difficilement envisageable.

Figure 11

Ceci est une des raisons principales pour laquelle le réseau vidéo est surtout appliqué aux immeubles récents.

#### **FONCTIONNALITÉS**

Pour aborder l'énumération des fonctionnalités d'un tel système, nous prendrons par exemple le cas d'un immeuble câblé comportant 128 abonnés.

#### Fonction de base

Le réseau vidéo sur paire torsadée ne peut faire moins que le réseau UHF, en conséquence, il est capable de transmettre les six canaux disponibles partout, ou presque, en France.

Dans le cas d'une chaîne cryptée, on peut de nouveau admettre que chaque abonné dispose de son décodeur.

Ceci est valable pour une chaîne

mais devient absurde dès que l'on est en présence de trois, quatre ou plus de systèmes de cryptage différents, comme cela est le cas par satellite.

Ceci sert donc d'introduction à la première originalité du système.

#### Contrôle d'accès

Si le décrypteur est placé en tête de réseau, les signaux audio et vidéo décryptés peuvent être transmis à tous les abonnés sans aucun contrôle.

Dans ce cas, il n'y a aucune distinction entre les abonnés payants et les autres... Ce cas de figure ne peut être employé.

Si, dans un système, plus évolué, le PC transmet à chaque microcontrôleur de gestion de commutation dédié à chaque abonné une table de commutation, d'interdiction et de redirection, le problème est résolu de manière fort élégante.

Le fonctionnement du système serait le suivant. Un abonné A souhaite visualiser la chaîne 4. Il s'est dûment acquitté de son abonnement et appuie sur la touche 4 de sa télécommande.

L'information remonte jusqu'à la tête de réseau, est analysée et décodée par le microcontrôleur. Le microcontrôleur, après examen de la table transmise par le PC, constate que ce canal est autorisé pour cet abonné, agit en conséquence et envoie les ordres ad-hoc aux commutateurs. Si par contre l'abonné B n'a pas souscrit à la chaîne 4, les opérations se déroulent de la manière suivante : réception et décodage de la demande du canal 4 à la tête de réseau. Après examen du statut de cet abonné au câble, mais pas au canal 4, le microcontrôleur redirige cette demande vers un canal spécialisé. Ce canal spécialisé peut être une mire incluant le message : désolé de ne pouvoir vous fournir cette émission pour laquelle, etc.

L'exemple de deux abonnés au câble ou plutôt à la paire torsadée, peut bien évidemment s'appliquer à l'ensemble du réseau des M abonnés.

Cette procédure s'applique bien sûr aux émissions dites terrestres mais bien évidemment aussi aux émissions transmises via satellite. Le réseau se charge alors de toutes les possibilités de cryptage: Eurocrypt, Vidéocrypt, Nagravision, etc. qui nous gâchent le paysage.

A ce stade, le gain en matériel est substantiel car un seul décrypteur est placé en tête de réseau.

Cette caractéristique propre au réseau sur paire torsadée est un premier avantage sur le réseau UHF.

Sur le réseau UHF, le média étant commun à tous les récepteurs, la distinction entre abonnés est impossible. Pour palier cet inconvénient, chacun se doit d'avoir un décrypteur.

#### Audimétrie en temps réel

Grâce au signal de télécommande – sous-porteuse – il est facile de savoir si le terminal de l'abonné est hors tension.

D'autre part, à chaque instant, le microcontrôleur a la connaissance du canal en service puisqu'il est le seul à en assurer la commutation.

Dans ces conditions, il est extrêmement simple de concevoir pour le PC une procédure de

scrutation et de surveillance de tous les abonnés. On imagine facilement les différentes représentations – histogrammes, camemberts, etc. – que l'on pourra proposer à partir des données d'audimétrie en temps réel.

Il ne nous appartient pas d'épiloguer sur ce que l'on pourra faire de ces données, mais simplement que la fonction peut être implémentée dans un tel réseau et qu'elle est quasiment envisageable aussi facilement dans le réseau UHF.

#### Pay per view

Si vous n'êtes pas content du titre, vous pouvez le remplacer par paiement à la carte. C'est quasiment pareil. Le paiement à la carte est donc une caractéristique qui découle naturellement des deux précédentes : audimétrie en temps réel et contrôle d'accès.

Evidemment, dans le cas de l'immeuble de 128 abonnés pris comme exemple, le pay per view peut paraître inadapté.

Si l'on remplace immeuble par hôtel et abonné par chambre, cette caractéristique peut devenir importante

Le réseau n'étant plus limité en nombre de canaux, il est facile de concevoir la diffusion de trois, quatre, cinq ou plus films sur autant de canaux et un paiement en fonction de ce que l'on regarde. Le PC centralisant ces informations utilise dans ce cas une passerelle vers le calculateur chargé de la comptabilité.

#### Messagerie

Puisque nous sommes dans les hôtels, restons-y. Avec les synoptiques tête de réseau et terminal abonné définis aux figures 8, 9, 10, un service de messagerie se conçoit simplement.

Les messages sont stockés à la tête de réseau et le seul moyen d'introduction et de mémorisation est le PC.

Le message a une forme généra-

de (origine)...

à (destination) : M. X chambre 340, comprendre abonné 110 par exemple.

La demande d'examen des messages est toujours issue du destinataire – l'abonné –.

Cette demande sera stockée par le microcontrôleur chargé de la commutation.

Le PC, scrutant tour à tour chaque abonné, prend connaissance de cette demande et transmet les messages.

La transmission des messages peut s'effectuer de deux manières différentes.

Une page de télétexte est générée localement et envoyée au destinataire sur un canal particulier auquel les autres abonnés n'ont pas accès - en tous cas pendant le même laps de temps -.

Cette première solution est un peu restrictive et on lui préférera la suivante.

Les messages sont envoyés au terminal abonné sous forme de données et celles-ci sont exploitées par la circuiterie télétexte.

Il apparaît clairement qu'un dialogue est établi entre le terminal et la tête de réseau. Les deux microcontrôleurs peuvent presque échanger des données à l'insu de l'abonné.

Cet échange sera utilisé pour contrôler la liaison et s'assurer que les transmissions s'effectuent sans erreurs.

#### Autres applications de surveillance.

Des canaux peuvent être monopolisés par des canaux destinés à la vidéosurveillance mais ceci ne relève pas d'une originalité extrême. Evidemment, seuls certains abonnés auront accès à ces images. La plus intéressante des applications de surveillance est probablement le vidéo-portier d'immeuble d'habitation ou de bureau.

Le visiteur sonnant à la porte principale est vu par la seule personne visitée.

Cette application ne pose pas de problème et la configuration du réseau décrit précédemment est adaptée à ce vidéo-portier.

Il est clair que le visiteur, par sa pression sur la sonnette a modifié la table de contrôle d'accès des canaux. A cet instant, seul le destinataire a accès au canal vidéoportier qui peut même être forcé à partir de la tête de réseau.

Toujours dans le cadre de la surveillance, la tête de réseau peut être employée comme signal d'alerte, évacuation totale, partielle ou appel sélectif de personne. Dans le sens abonné vers tête de réseau, le canal numérique : liaison télécommande peut aussi véhiculer des informations de sécurité : violation de domicile, de la chambre, incendie, etc.

Le réseau joue alors le rôle d'un réseau de télésurveillance classique.

Il est important de bien voir l'intérêt de cette paire torsadée dans le temps. Il suffit simplement de prévoir le réseau en étoile à l'origine. Toutes les options que nous avons énumérées peuvent être implantées au fur et à mesure de l'exploitation du réseau.

Il est clair, par exemple, que la télésurveillance ne remet pas en cause un réseau existant. Son installation ne nécessite que quelques capteurs et une couche de logiciel supplémentaire à la tête de réseau.

Cette caractéristique est très importante pour pouvoir étaler l'investissement dans le temps. Seul un réseau évolutif permet cet étalement.

#### Télécommande, Téléachat, Télépaiement

Ces trois applications sont destinées particulièrement aux hôtels. Pour la télécommande, l'abonné peut sélectionner son petit déjeuner, son menu ou autre.