ORDER NO. ARP 1502

# CCLD-1030

- This service manual is applicable to the KUC type.

- For the circuit description, refer to CLD-3030 Service Guide (ARP1560).

# **CONTENTS**

| 1. | SAFETY INFORMATION            | 2  |

|----|-------------------------------|----|

|    | PACKING                       |    |

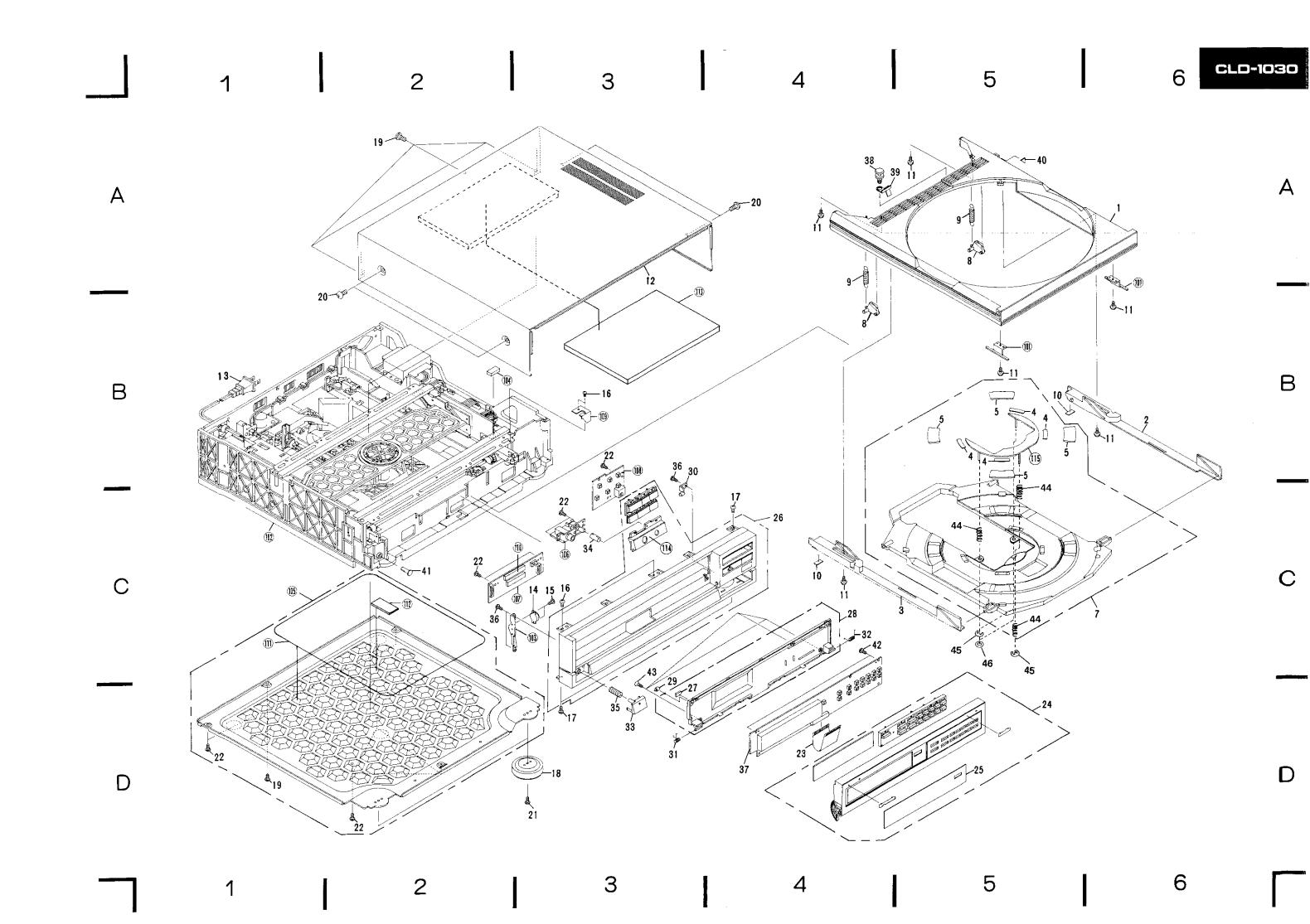

|    | EXPLODED VIEWS AND PARTS LIST |    |

|    | 3.1 EXTERIOR AND FRONT VIEW   | 4  |

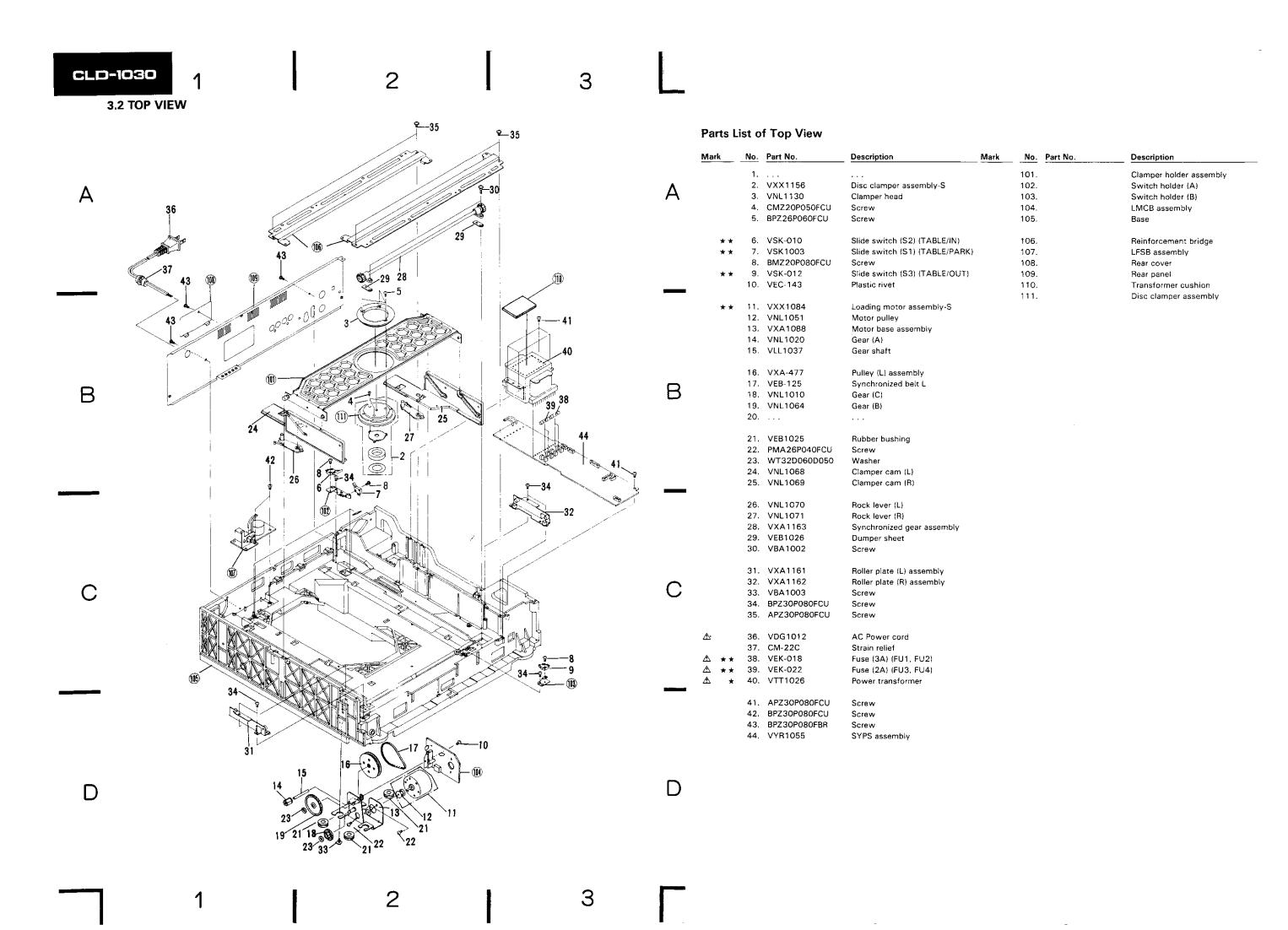

|    | 3.2 TOP VIEW                  | 7  |

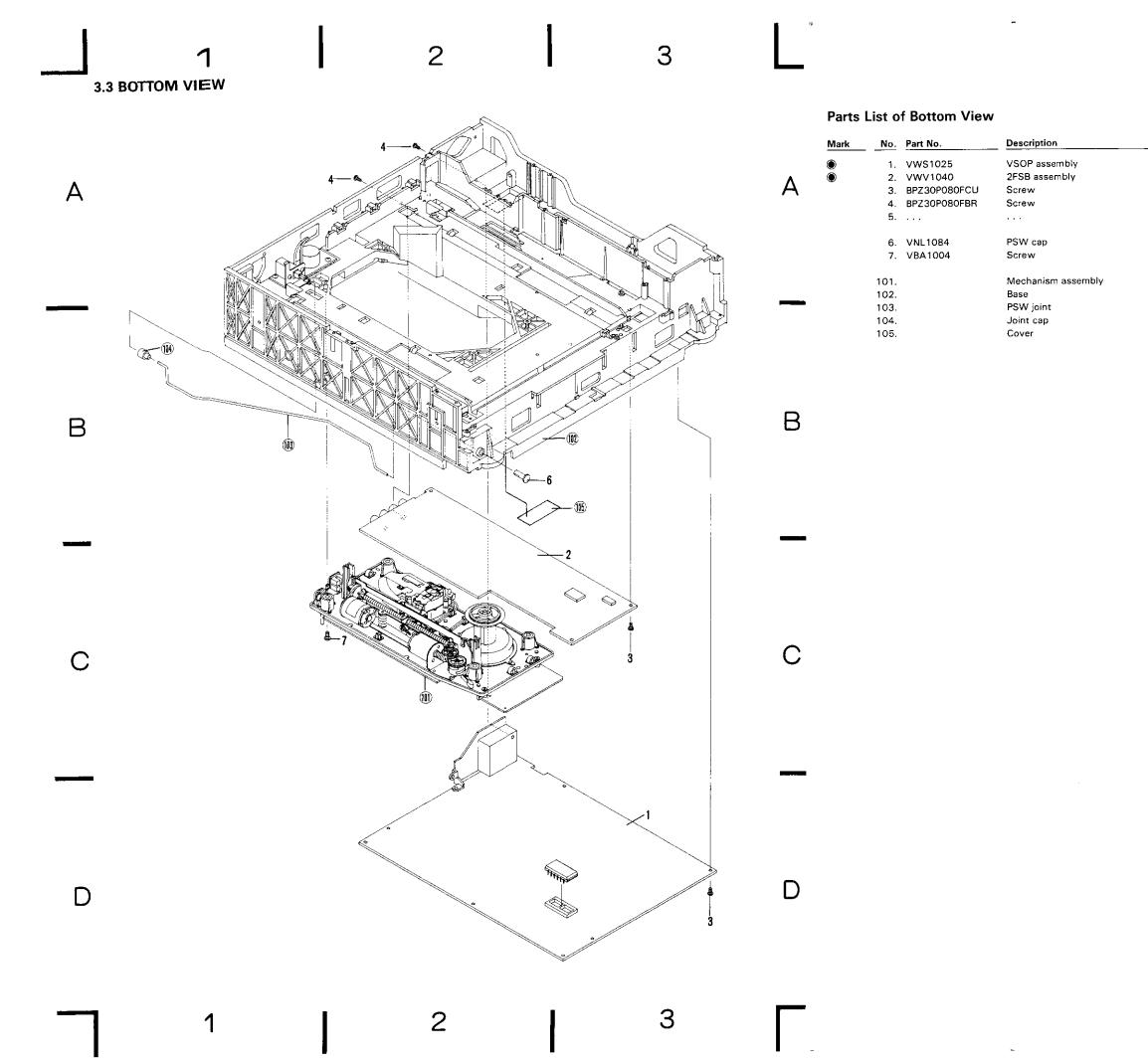

|    | 3.3 BOTTOM VIEW               | 9  |

|    | 3.4 MECHANISM ASSEMBLY VIEW   | 11 |

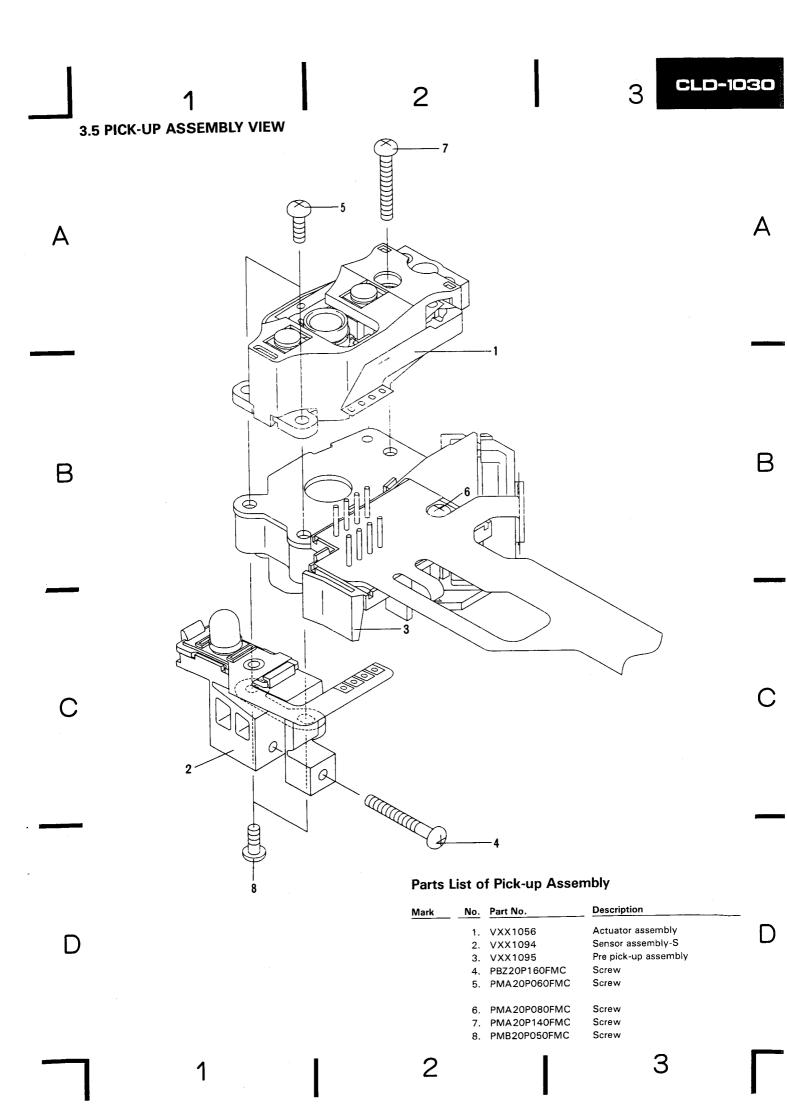

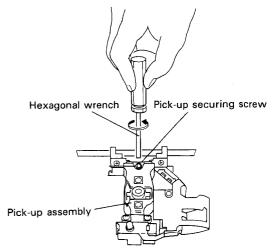

|    | 3.5 PICK-UP ASSEMBLY VIEW     | 13 |

|    | 3.6 REMOTE CONTROL UNIT       |    |

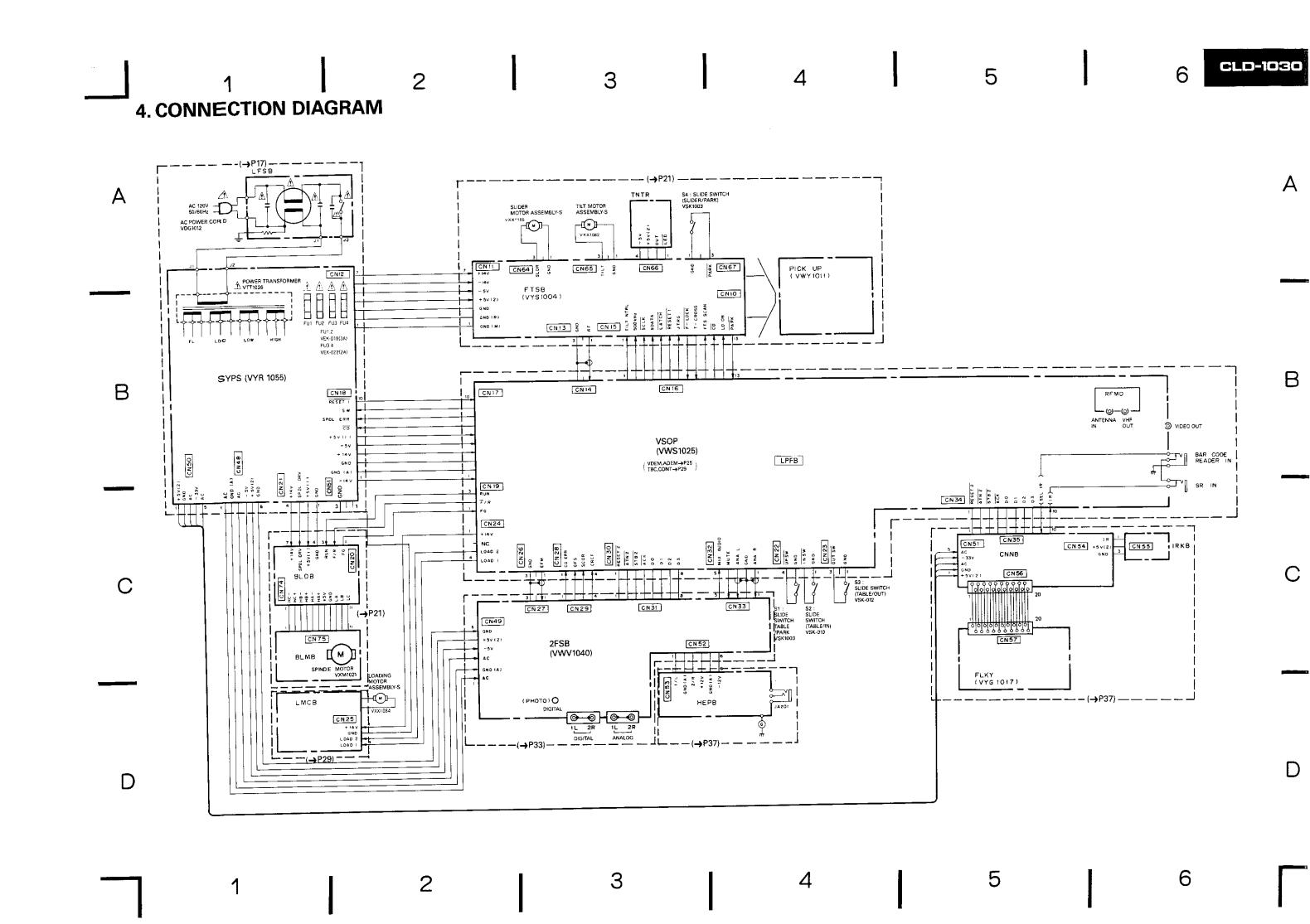

| 4  | CONNECTION DIAGRAM            | 15 |

|    | SCHEMATIC DIAGRAM AND         |    |

| J. | P.C. BOARD PATTERNS           |    |

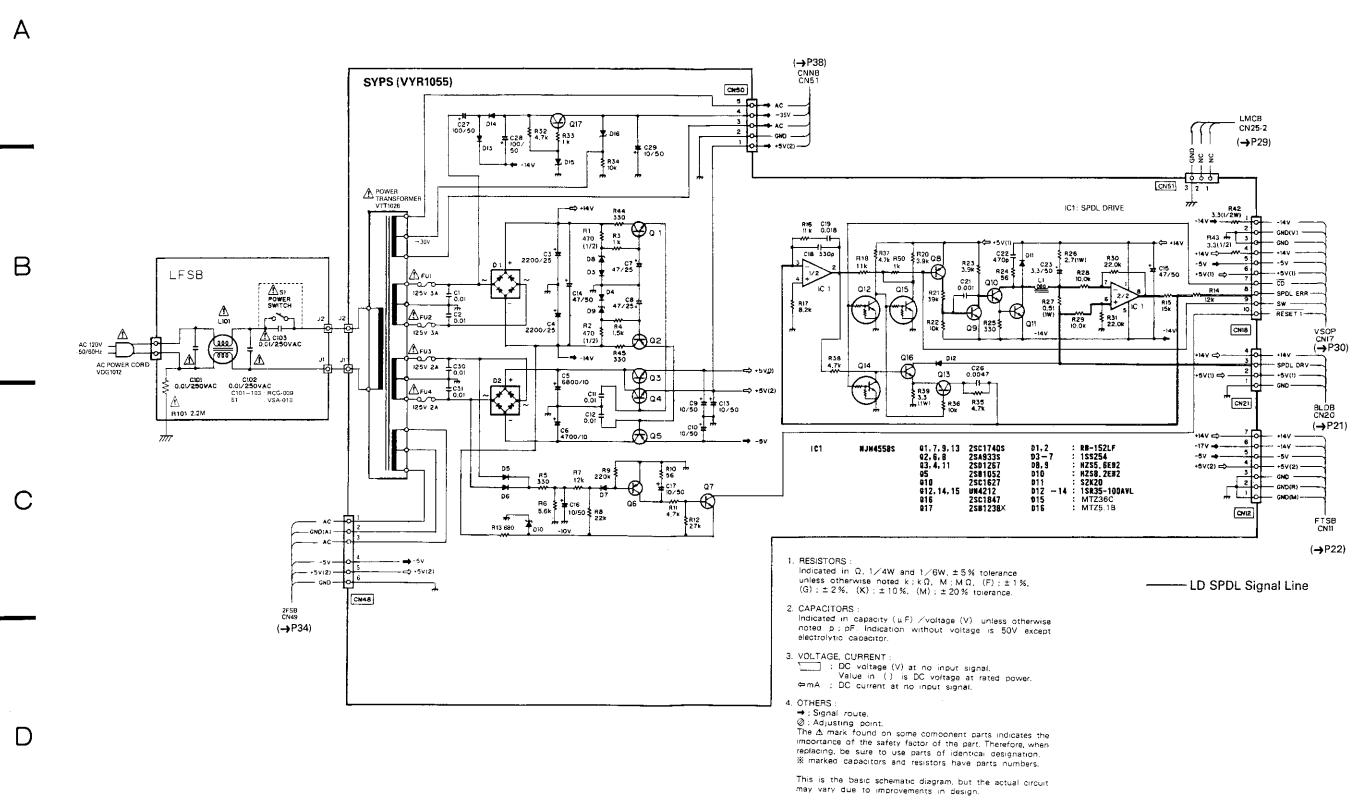

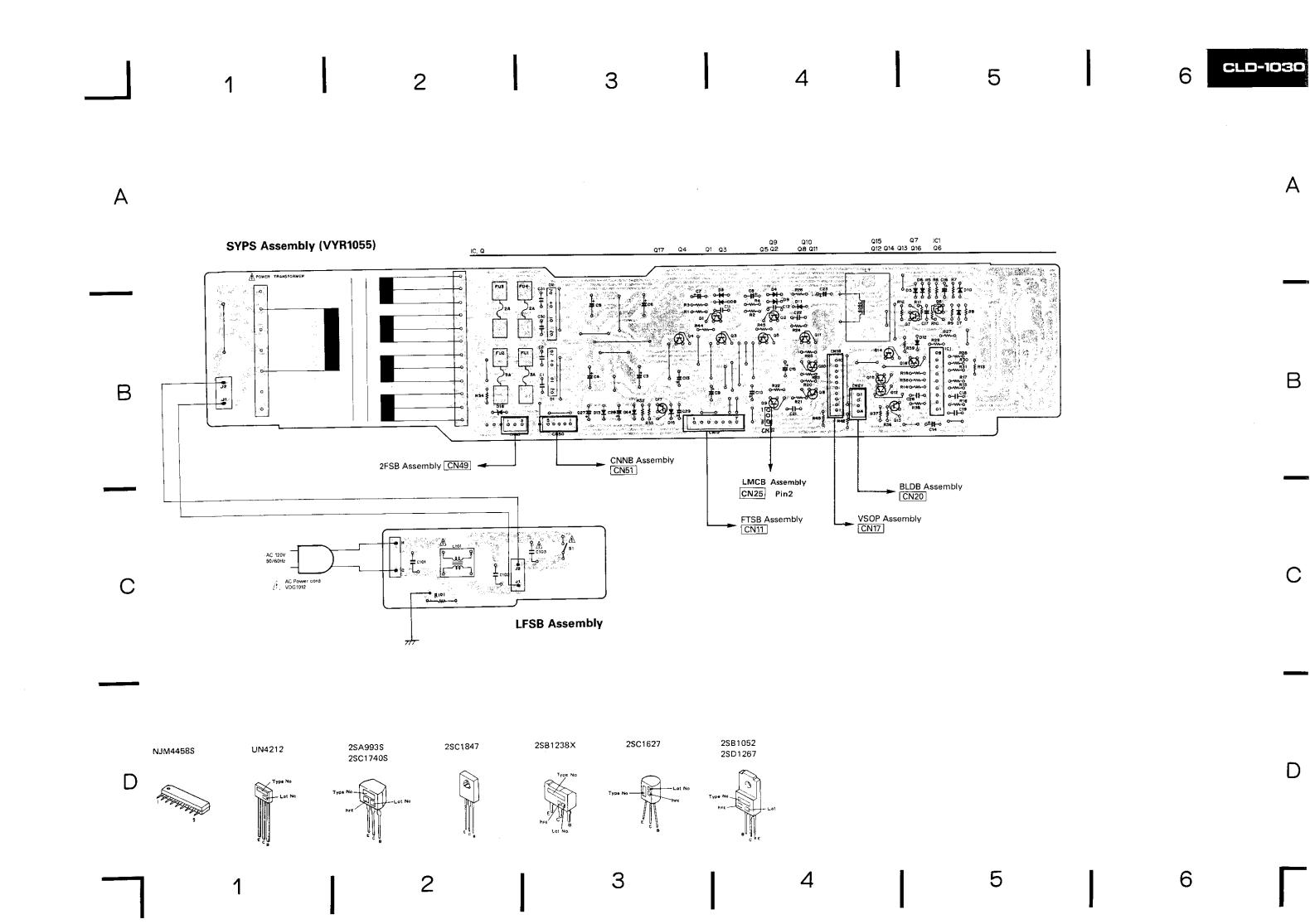

|    | 5.1 LFSB AND SYPS ASSEMBLY    | 17 |

|    | 0.1 2.02 /                    |    |

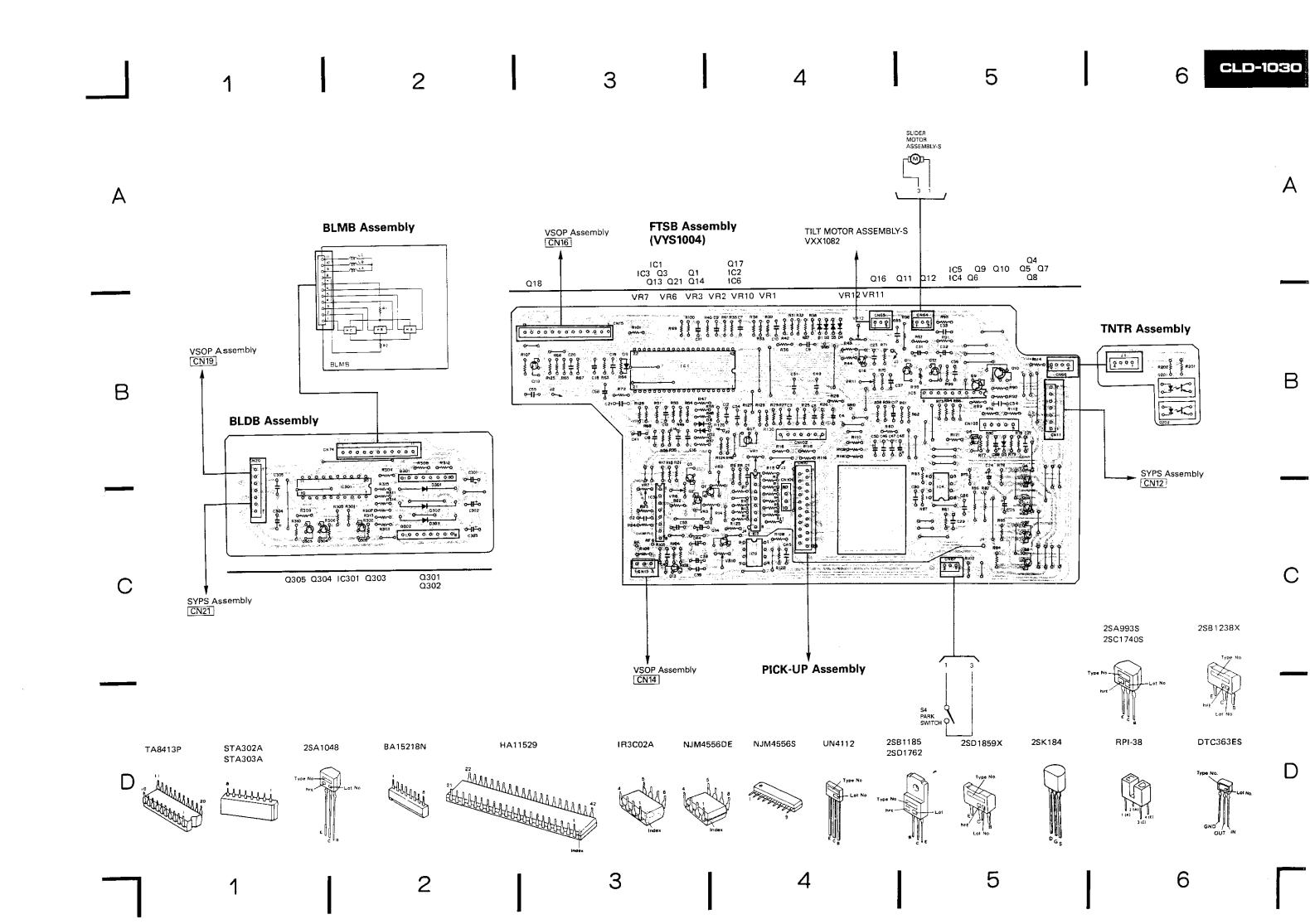

|    | 5.2 BLDB, BLMB, FTSB, TNTR AND |    |

|----|--------------------------------|----|

|    | PICK-UP ASSEMBLY               | 21 |

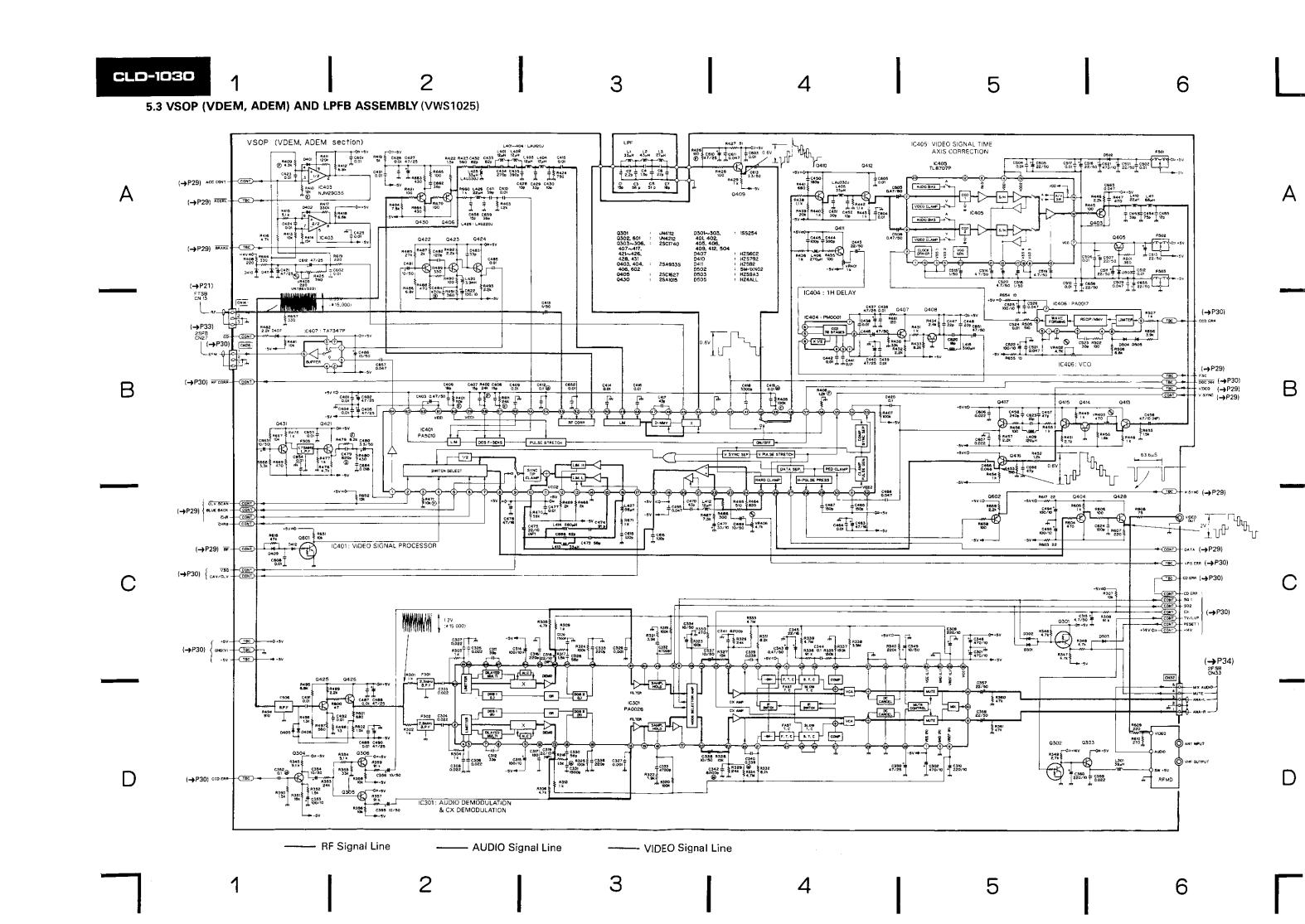

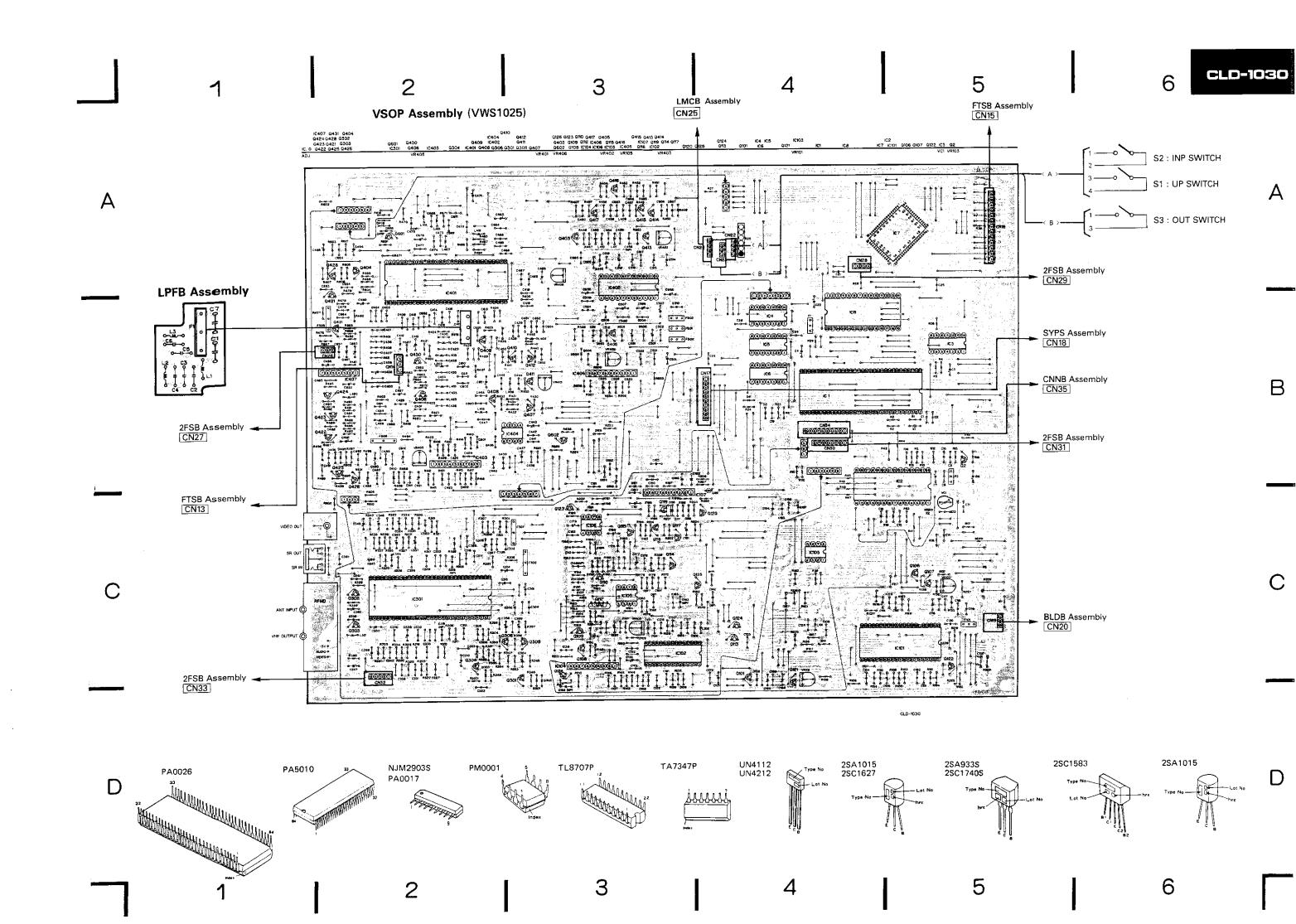

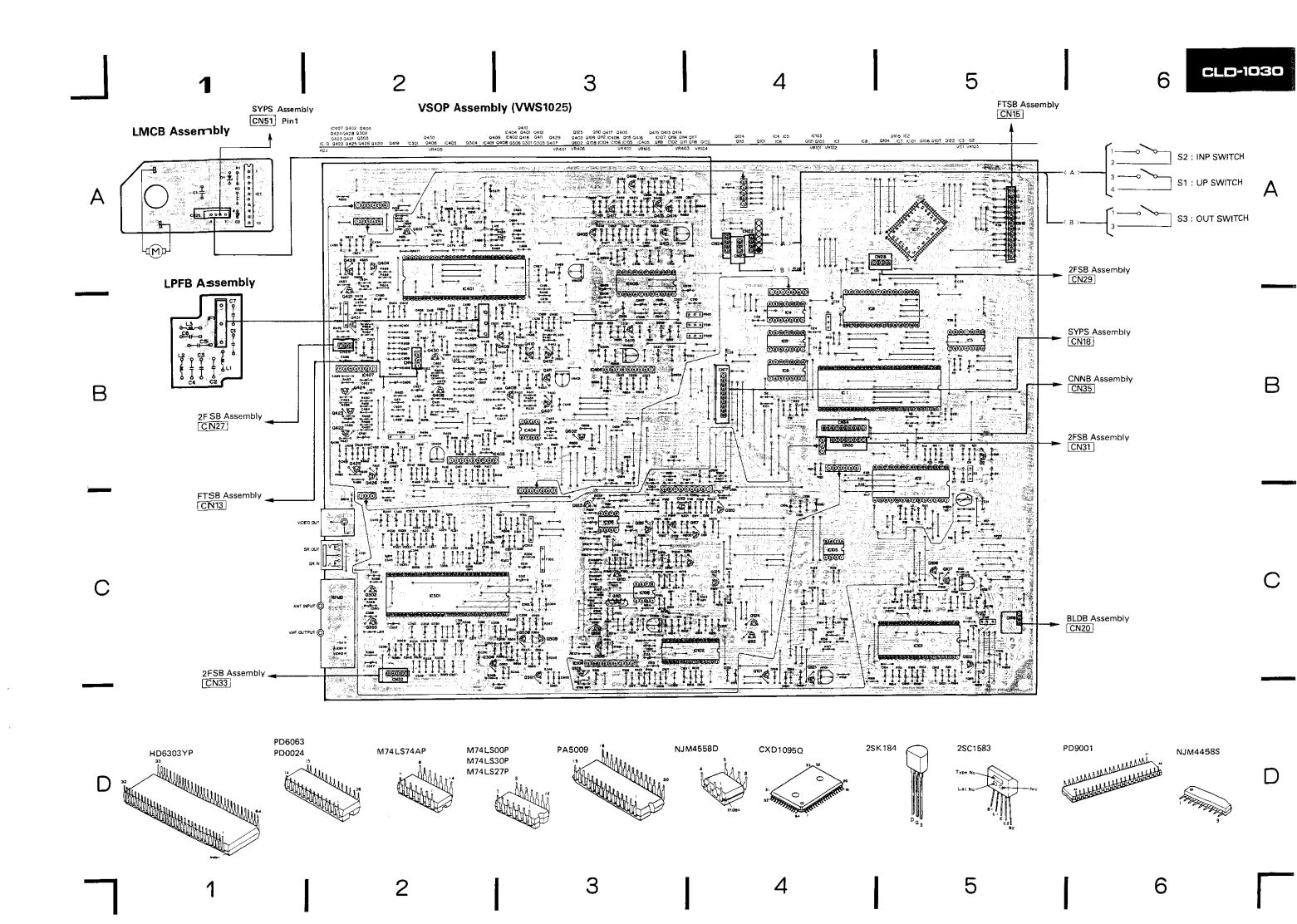

|    | 5.3 VSOP (VDEM, ADEM) AND LPFB |    |

|    | ASSEMBLY                       | 25 |

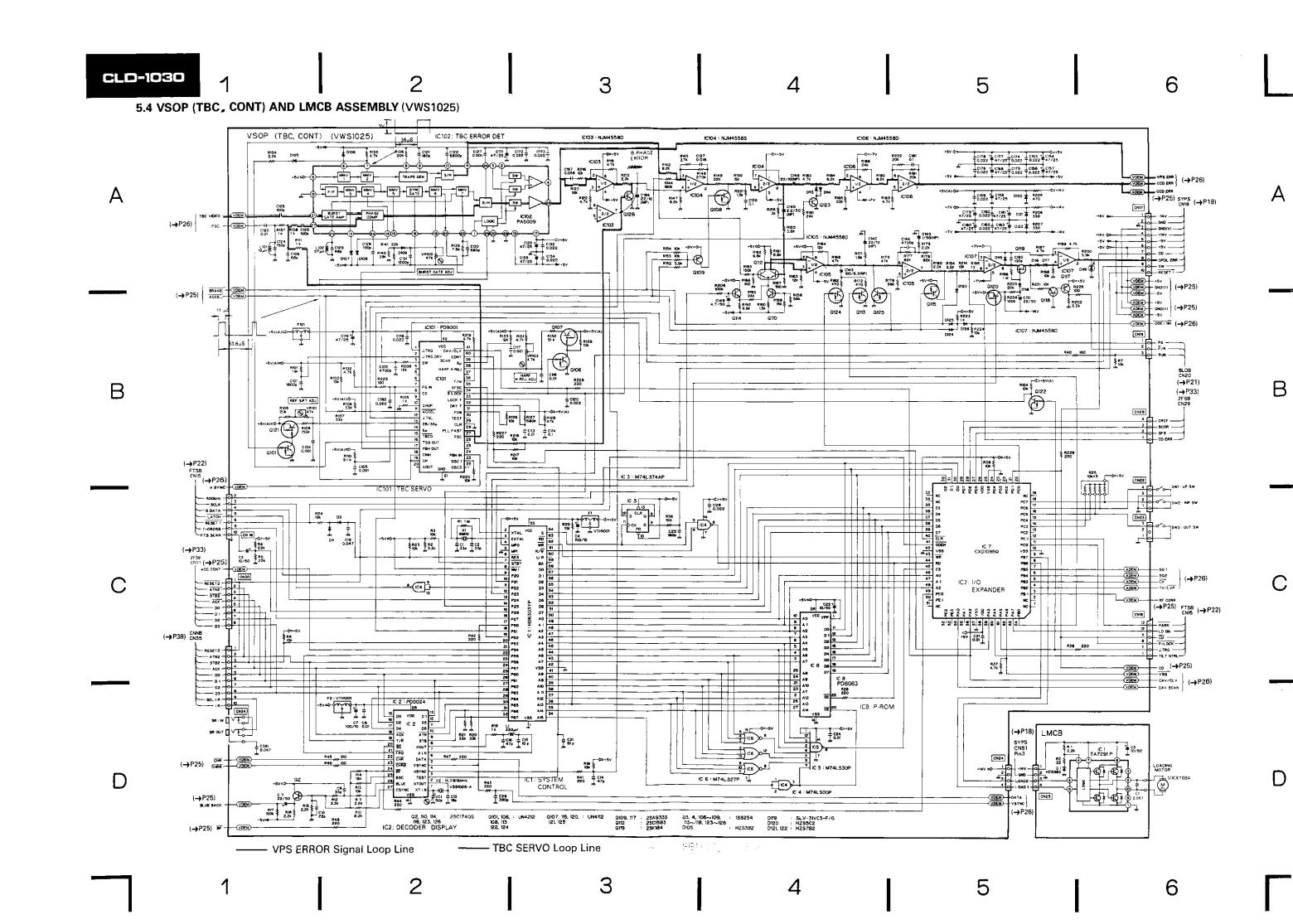

|    | 5.4 VSOP (TBC, CONT) AND LMCB  |    |

|    | ASSEMBLY                       | 29 |

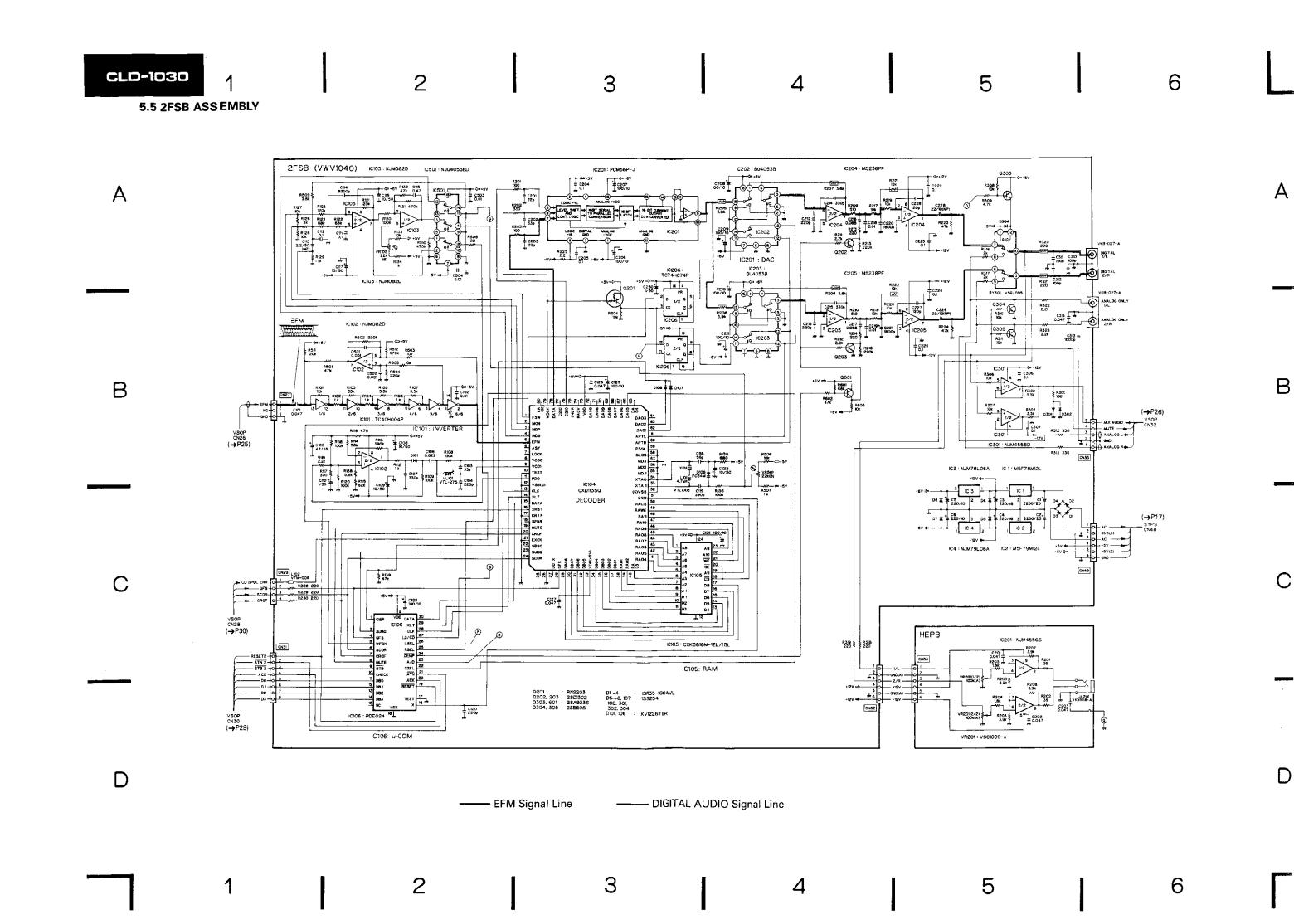

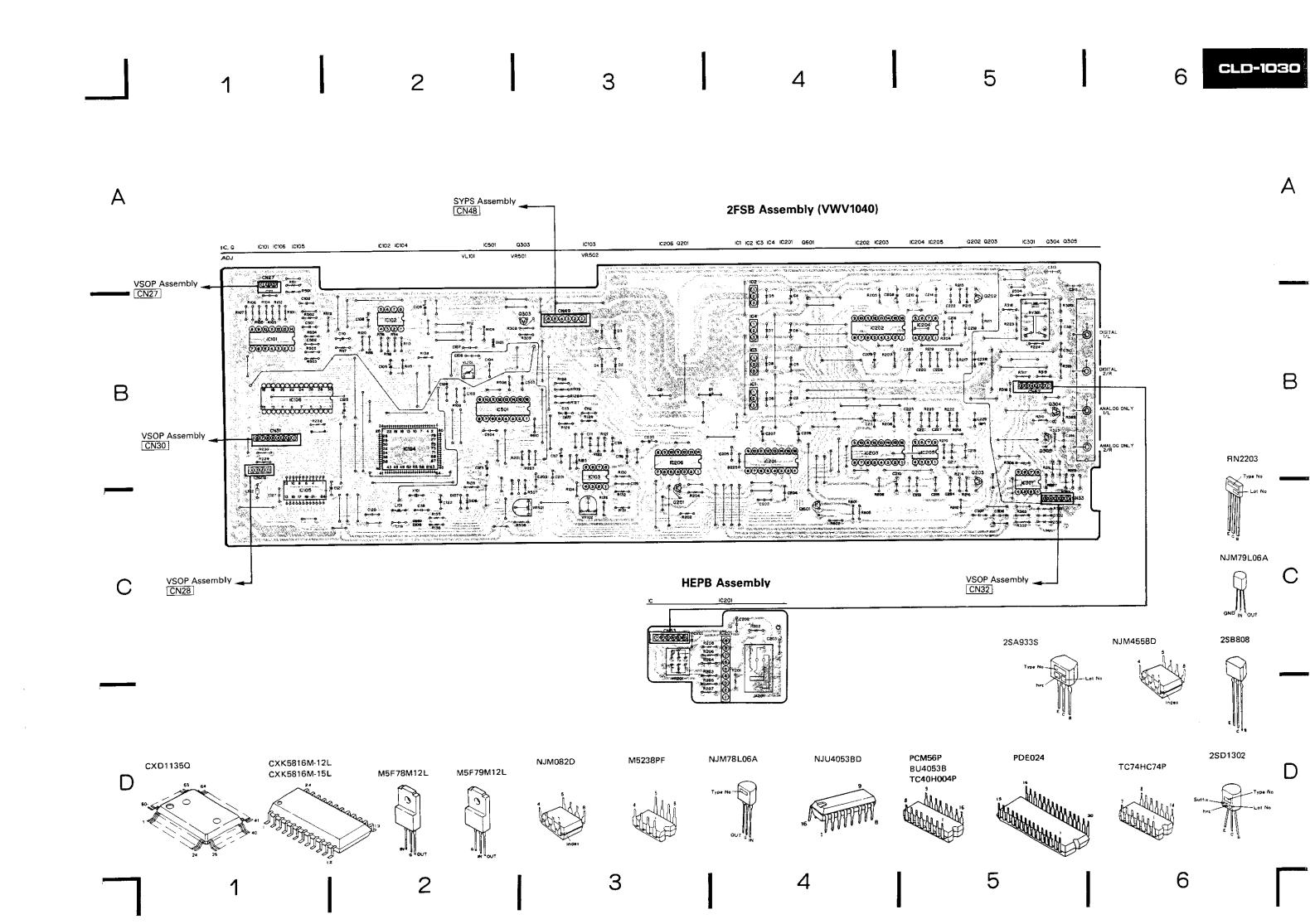

|    | 5.5 2FSB ASSEMBLY              | 33 |

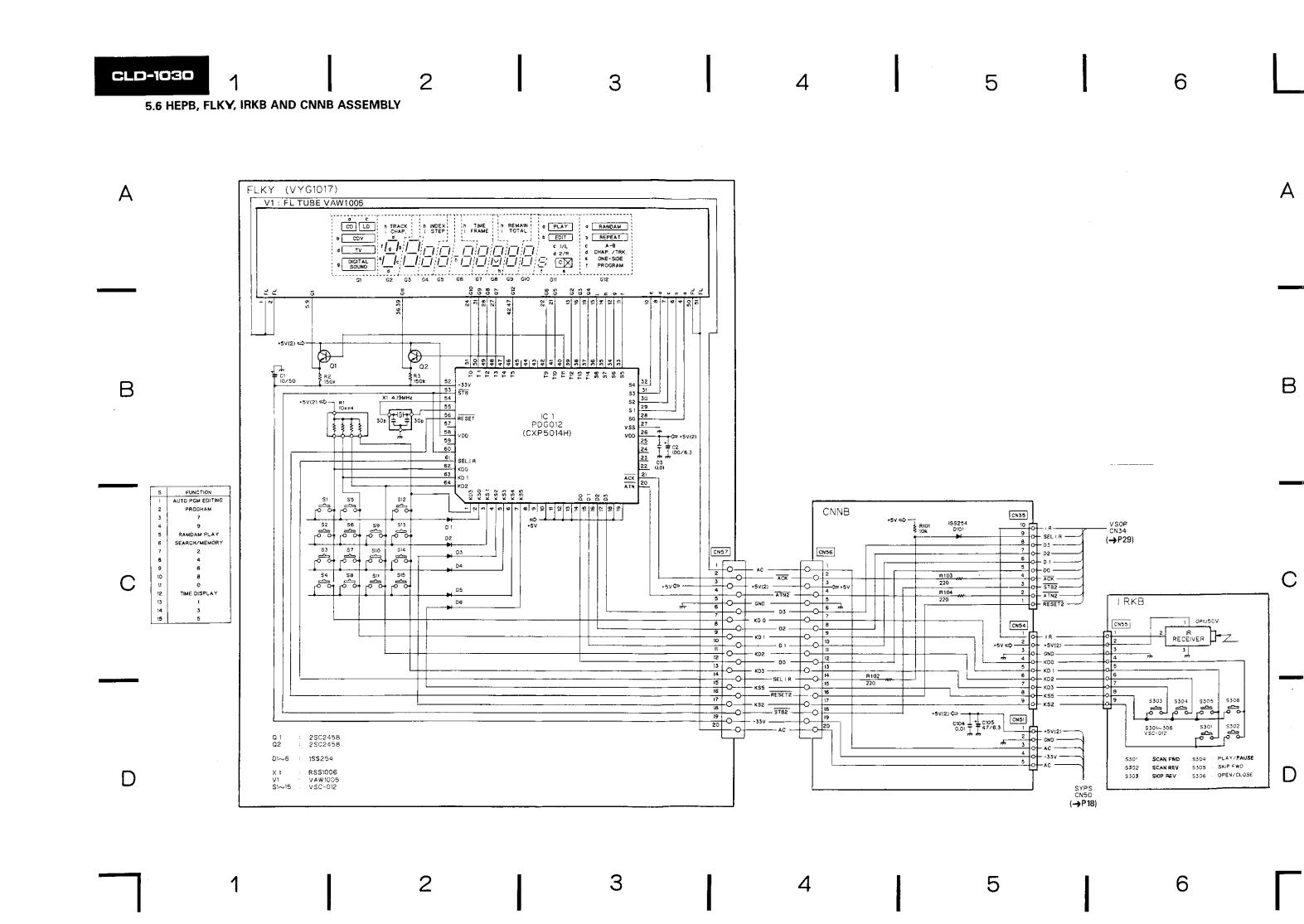

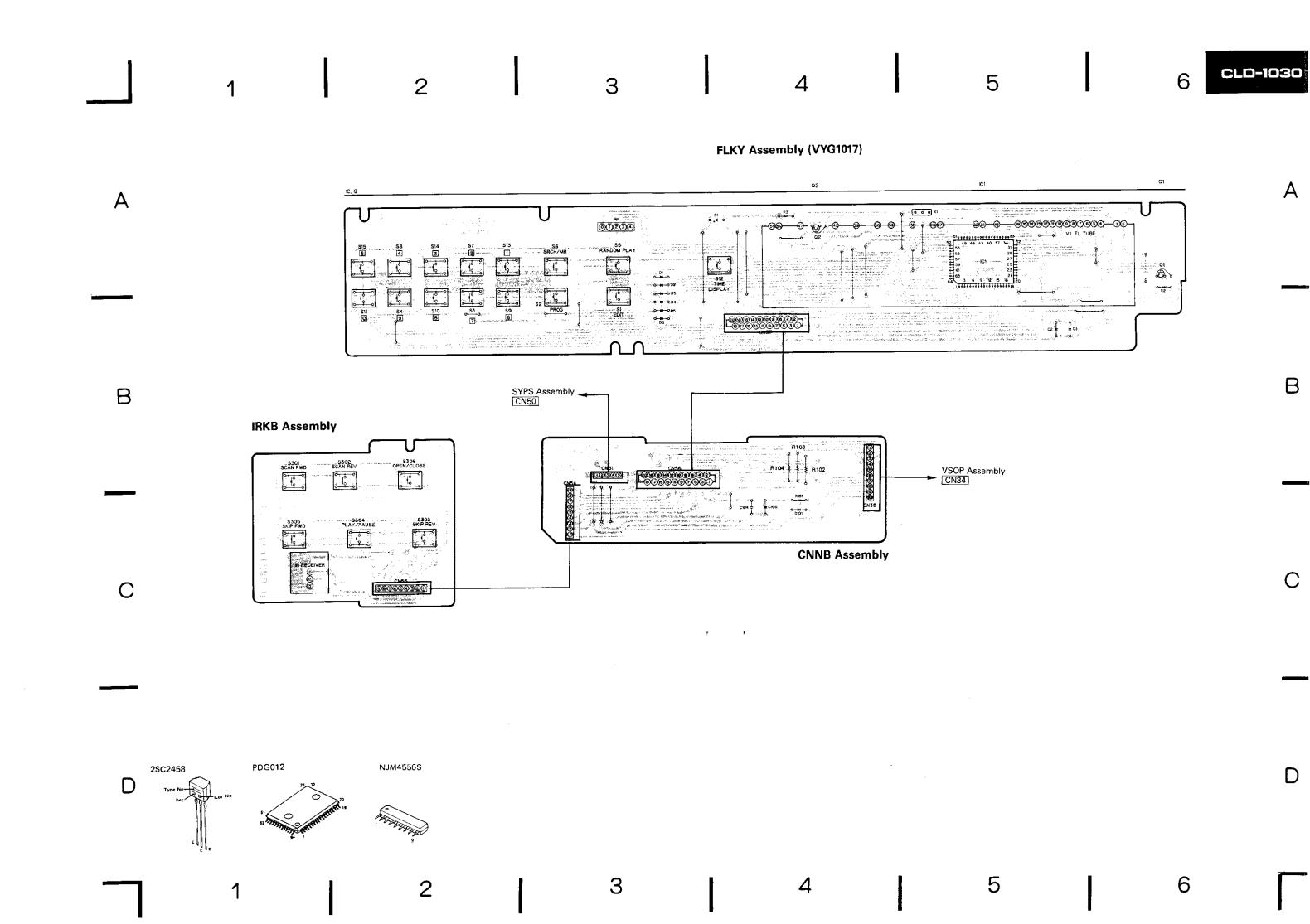

|    | 5.6 HEPB, FLKY, IRKB AND CNNB  |    |

|    | ASSEMBLY                       | 37 |

| 6. | ELECTRICAL PARTS LIST          | 41 |

| 7. | PICK-UP ASSEMBLY REPLACEMENT   |    |

|    | PROCEDURES                     | 48 |

| 8. | ADJUSTMENTS                    |    |

# 1. SAFETY INFORMATION

#### -(FOR USA MODEL ONLY)-

#### 1. SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

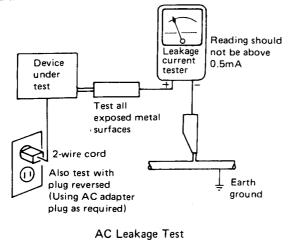

#### LEAKAGE CURRENT CHECK

Measure leakage current to a known earth ground (water pipe, conduit, etc.) by connecting a leakage current tester such as Simpson Model 229-2 or equivalent between the earth ground and all exposed metal parts of the appliance (input/output terminals, screwheads, metal overlays, control shaft, etc.). Plug the AC line cord of the appliance directly into a 120V AC 60Hz outlet and turn the AC power switch on. Any current measured must not exceed 0.5mA.

ANY MEASUREMENTS NOT WITHIN THE LIMITS OUT-LINED ABOVE ARE INDICATIVE OF A POTENTIAL SHOCK HAZARD AND MUST BE CORRECTED BEFORE RETURNING THE APPLIANCE TO THE CUSTOMER.

#### 2. PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in the appliance have special safety related characteristics. These are often not evident from visual inspection nor the protection afforded by them necessarily can be obtained by using replacement components rated for voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in this Service Manual.

Electrical components having such features are identified by marking with a  $\triangle$  on the schematics and on the parts list in this Service Manual.

The use of a substitute replacement component which does not have the same safety characteristics as the PIONEER recommended replacement one, shown in the parts list in this Service Manual, may create shock, fire, or other hazards.

Product Safety is continuously under review and new instructions are issued from time to time. For the latest information, always consult the current PIONEER Service Manual. A subscription to, or additional copies of, PIONEER Service Manual may be obtained at a nominal charge from PIONEER.

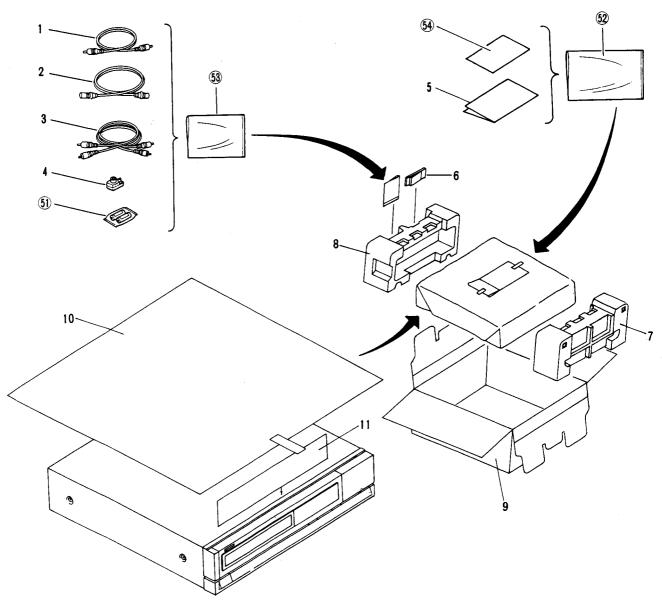

# 2. PACKING

# Parts List of Packing

| Mark | No.   | Part No.  | Description                      | Mark | No. | Part No. | Description      |

|------|-------|-----------|----------------------------------|------|-----|----------|------------------|

|      | 1.    | VDE-056   | Video cable                      |      | 9.  | VHG1026  | Packing case     |

|      | • • • | (VDE1004) |                                  |      | 10. | VHL1006  | Packing sheet    |

|      | 2.    | VDE1001   | RF antenna cable                 |      | 11. | VHL1008  | Protection sheet |

|      |       | (VDE-054) |                                  |      |     |          |                  |

|      | 3.    | VDE-055   | Audio cable                      |      | 51. |          | Battery UM-4     |

|      |       | (VDE1005) |                                  |      | 52. |          | Polyethylene bag |

|      |       | ,         |                                  |      | 53. |          | Polyethylene bag |

|      | 4.    | VKX1001   | Antenna adaptor                  |      | 54. |          | Caution card     |

|      | 5.    | VRB1008   | Operating instructions (English) |      |     |          |                  |

|      | 6.    | VXX1122   | Remote control unit              |      |     |          |                  |

|      | 7.    | VHA1027   | Pad (F)                          |      |     |          |                  |

|      | 8.    | VHA1028   | Pad (R)                          |      |     |          |                  |

# 3. EXPLODED VIEWS AND PARTS LIST

# 3.1 EXTERIOR AND FRONT VIEW

#### NOTES:

- Parts without part number cannot be supplied.

- ullet The  $\underline{\mathbb{A}}$  mark found on some component parts indicates the importance of the safety factor of the part. Therefore, when replacing, be sure to use parts of identical designa-

- For your parts Stock Control, the fast moving items are indicated with the marks ★★ and \*.

- \* \* GENERALLY MOVES FASTER THAN \*

- This classification shall be adjusted by each distributor because it depends on model number, temperature, humidity, etc.

Parts marked by "©" are not always kept in stock. Their delivery time may be longer

- than usual or they may be unavailable.

## Parts List of Exterior and Front View

38. VEC1059

39. VBK1009

40. VEB1045

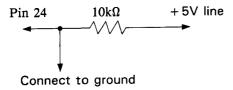

Plastic rivet

Switch spring

Stop dump rubber

| Vlark        | No.   | Part No.                                | Description            | Mark | No.    | Part No.     |            | Description            |

|--------------|-------|-----------------------------------------|------------------------|------|--------|--------------|------------|------------------------|

|              | 1.    | VNK1090                                 | Carry                  |      | 41.    | VNL1084      |            | PSW cap                |

|              |       | VNL1061                                 | Rack gear (R)          |      | 42.    | BPZ26P06     | OFCU       | Screw                  |

|              |       | VNL1060                                 | Rack gear (L)          |      | 43.    | CPZ26P10     | OFZK       | Screw                  |

|              | _     | VEC1130                                 | Disc pad (Z)           |      | 44.    | VBH1047      |            | Sub container spring   |

|              |       | VEC1115                                 | Disc pad               |      | 45.    | WT16D06      | 0D025      | Wsher                  |

|              | 0.    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | •                      |      | 46.    | WA22N05      | 50W020     | Nylon washer           |

|              | 6.    | VBH1047                                 | Sub container spring   |      |        |              |            |                        |

|              | 7.    | VXX1143                                 | Container assembly-S   |      | 101.   |              |            | Rack holder            |

|              | 8.    | VNL1062                                 | Stopper                |      | 102.   |              |            | Base assembly          |

|              | 9.    | VBH1021                                 | Stopper spring         |      | 103.   |              |            | Dumper holder plate    |

|              | 10.   | VEB1041                                 | Rack Dump rubber       |      | 104.   |              |            | Insulator cushion      |

|              |       |                                         |                        |      | 105.   |              |            | Bottom plate assembly  |

|              | 11.   | IBZ30P080FCU                            | Screw                  |      |        |              |            |                        |

|              | 12.   | VXX1125                                 | Bonnet assembly-S      |      | 106.   |              |            | HEPB assembly          |

| <u>^</u>     | 13.   | VDG1012                                 | AC Power cord          |      | 107.   |              |            | CNNB assembly          |

|              | 14.   | REC1005                                 | Dumper assembly        |      | 108.   |              |            | IRKB assembly          |

|              | 15.   | PMZ20P040FCU                            | Screw                  |      | 109.   |              |            | Stop plate             |

|              |       |                                         |                        |      | 110.   |              |            | Cushion (A)            |

|              | . 16. |                                         | Screw                  |      |        |              |            |                        |

|              | 17.   | APZ30P080FCU                            | Screw                  |      | 111.   |              |            | Insulator sheet        |

|              | 18.   | VXA1094                                 | Insulator assembly     |      | 112.   |              |            | Spacer                 |

|              | 19.   | BBT30P060FBR                            | Screw                  |      | 113.   |              |            | Cushion (B)            |

|              | 20.   | BPZ40P100FBR                            | Screw                  |      | 114.   |              |            | Jack panel             |

|              |       |                                         |                        |      | 115.   |              |            | Sub container assembly |

|              | 21.   | APZ30P140FCU                            | Screw                  |      |        |              |            |                        |

|              | 22.   | BPZ30P080FCU                            | Screw                  |      |        |              |            |                        |

|              | 23.   | VDA1051                                 | Fuji card              |      |        |              |            |                        |

|              | * 24. | VXX1126                                 | Front door assembly-S  |      |        |              |            |                        |

|              |       | VXX1196                                 |                        |      |        |              |            |                        |

|              | 25.   | VNK1125                                 | FL panel (X)           |      |        |              |            |                        |

|              | 26.   | VXX1124                                 | Front panel assembly-S |      | *NOTE  |              |            |                        |

|              | 27.   | VEB1033                                 | Door dump rubber       |      |        |              |            |                        |

|              | 28.   | VXX1081                                 | Door cover assembly-S  |      | Front  | door assemb  | bly-S      |                        |

|              | 29.   | VNL1042                                 | Roller                 |      | Sori   | al No.       | Part No.   |                        |

|              | 30.   | VXA1166                                 | Hinge assembly         |      | 36116  | ai 140.      | Fait NO.   |                        |

|              |       |                                         | <b>5</b>               |      | 390    | 3001         |            |                        |

|              | _     | VBH1048                                 | Door spring (L)        |      |        | 3903100      | VXX1126    | 5                      |

|              |       | VBH1049                                 | Door spring (R)        |      |        |              |            |                        |

|              |       | VNK1105                                 | Power button           |      | 3903   | 3101         |            |                        |

|              |       | VNK1106                                 | Volume knob            |      | 1 ~    |              | VXX1196    | 5                      |

|              | 35.   | VBH1019                                 | Power spring           |      |        |              |            |                        |

|              |       | PD700B080EC!!                           | Saraw                  |      | The d  | ifference be | tween VX   | X1126 and VXX1196      |

|              |       | BPZ30P080FCU                            | Screw                  |      | is the | color of the | FL filter. |                        |

| lacktriangle | 37.   | VYG1017                                 | FLKY assembly          |      |        |              |            |                        |

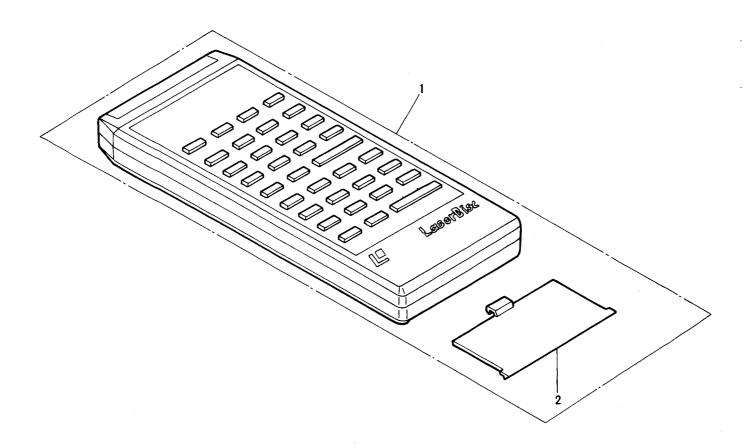

# 3.6 REMOTE CONTROL UNIT

# Parts List of Remote control unit

| Mark | No. | Part No. | Description         |

|------|-----|----------|---------------------|

|      | 1.  | VXX1122  | Remote control unit |

|      | 2.  | PNW1153  | Battely cover       |

| /lark                                                        | Symbol & Descri                      | ption                                | Part No. OTHERS            |       |                                              |                                           |  |

|--------------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------|-------|----------------------------------------------|-------------------------------------------|--|

|                                                              | C139, C181, C3                       | 44, C352, C412,                      | CFTXA104J50                | Mark  | Symbol & Description                         | Part No.                                  |  |

|                                                              | C420                                 |                                      |                            | *     | X1 Ceramic resonator                         | KBR-4.0MS                                 |  |

|                                                              | C19, C361, C46                       |                                      | CGCYX473M25                |       | X2 Crystal resonator                         | VSS1005                                   |  |

|                                                              | C521, C526, C6                       | 11, C657, C665,                      |                            |       |                                              |                                           |  |

|                                                              | C669                                 |                                      | <b></b>                    |       | RFMD                                         | VWL1008                                   |  |

|                                                              | C332, C333                           |                                      | CKCYB472K50                |       | Pin jack (VIDEO)                             | VKB-014                                   |  |

|                                                              |                                      |                                      |                            |       | IC socket (28 Pin)                           | VKH1001                                   |  |

|                                                              |                                      | 123, C401, C404,                     | CKCYF103Z50                |       | Mini pin jack (2P)                           | VKN1034                                   |  |

|                                                              | C409, C410, C4                       |                                      |                            |       |                                              |                                           |  |

|                                                              |                                      | 431, C436, C438,                     |                            |       |                                              |                                           |  |

|                                                              |                                      | 42, C464, C477,                      |                            | 2FSB  | Assembly (VWV1040)                           |                                           |  |

|                                                              | C485, C487, C4                       | 189, C491, C492,<br>506, C510, C512, |                            | SEMIC | ONDUCTORS                                    |                                           |  |

|                                                              | C517, C524, C6                       |                                      |                            | 88    | Cumbal & Description                         | Part No.                                  |  |

|                                                              | C652-C654                            | ,01 0001,                            |                            | Mark  | Symbol & Description                         | BU4053B                                   |  |

|                                                              | C052-C05+                            |                                      |                            |       | IC202, IC203                                 |                                           |  |

|                                                              | C615                                 |                                      | CKPUYB101K50               |       | IC104                                        | CXD1135Q<br>CXK5816M-12L                  |  |

|                                                              | C127, C326, C3                       | 327                                  | CKPUYB102K50               | **    | IC105                                        | (CXK5816M-15L)                            |  |

|                                                              | C130                                 |                                      | CKPUYB681K50               |       |                                              | (CXK3010W13E)                             |  |

|                                                              | C605                                 |                                      | CKPUYF103Z25               |       | IC1                                          | M5F78M12L                                 |  |

|                                                              |                                      |                                      |                            | # #   | 101                                          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,   |  |

|                                                              |                                      | 20, C132, C134,                      | CKPUYF223Z25               | **    | IC2                                          | M5F79M12L                                 |  |

|                                                              | C153, C156, C                        | 159, C160, C162,                     |                            |       | IC204, IC205                                 | M5238PF                                   |  |

|                                                              | C172-C176, C                         | 178, C182,                           |                            |       | IC102, IC103                                 | NJM082D                                   |  |

|                                                              |                                      | :359, C606, C607                     |                            |       | IC301                                        | NJM4558D                                  |  |

|                                                              | C104, C105, C                        | 117                                  | CQMA102J50                 |       | IC3                                          | NJM78L06A                                 |  |

|                                                              |                                      |                                      | 00144400450                |       |                                              |                                           |  |

|                                                              | C419, C113, C                        | 116, C608                            | CQMA103J50                 | **    | IC4                                          | NJM79L06A                                 |  |

|                                                              | C131                                 |                                      | CQMA122J50<br>CQMA152J50   | **    | IC501                                        | NJU4053BD                                 |  |

| C329, C331                                                   |                                      |                                      | CQMA182J50                 |       | IC201                                        | PCM56P-J                                  |  |

|                                                              | C101                                 |                                      | CQMA183J50                 |       | IC106                                        | PDE024                                    |  |

|                                                              | C137, C664                           |                                      | Calviniosoco               |       | IC101                                        | TC40H004P                                 |  |

|                                                              | C418                                 |                                      | CQMA272J50                 | **    | IC206                                        | TC74HC74P                                 |  |

|                                                              | C339, C340                           |                                      | CQMA393J50                 |       |                                              | DNIGOOO                                   |  |

|                                                              | C102, C144                           |                                      | CQMA472J50                 |       | Q201                                         | RN2203                                    |  |

|                                                              | C167                                 |                                      | CQMA563J50                 |       | Q303, Q601<br>Q304, Q305                     | 2SA933S<br>2SB808                         |  |

|                                                              | C122                                 |                                      | CQMA682J50                 |       | Q202, Q203                                   | 2SD1302                                   |  |

|                                                              |                                      |                                      |                            | ^ ^   | 4202, 4200                                   |                                           |  |

|                                                              | C468                                 |                                      | CQMA683J50                 | *     | D106                                         | FC54M                                     |  |

|                                                              | C341, C342                           |                                      | CQMA822J50                 | *     | D101                                         | KV1226YBR                                 |  |

|                                                              | C121                                 |                                      | CQSA181J50                 | *     | D1-D4                                        | 1SR35-100AV                               |  |

|                                                              | C484                                 |                                      | CQSA471J50                 | *     | D5-D8, D107, D108, D301, D302                | 2, 1SS254                                 |  |

|                                                              | C479                                 |                                      | CQSA821J50                 |       | D304                                         |                                           |  |

|                                                              | VC1 C                                | eramic trimmer                       | VCM-003                    |       |                                              |                                           |  |

|                                                              | ,,,                                  |                                      |                            | RELAY | •                                            |                                           |  |

| RESIS                                                        | TORS                                 |                                      |                            | Mark  | Symbol & Description                         | Part No.                                  |  |

| Mark                                                         | Symbol & Desc                        | ription                              | Part No.                   | * *   | RY301 Relay                                  | VSR-005                                   |  |

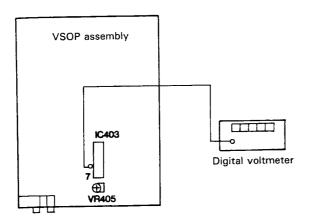

| *                                                            | vR401                                | Semi-fixed (1k $\Omega$ )            | VRTB6VS102                 | * *   | 33                                           | / · · · · ·                               |  |

| *                                                            | VR405                                | Semi-fixed (220 $\Omega$ )           | VRTB6VS221                 | COILS |                                              |                                           |  |

| *                                                            |                                      | Semi-fixed (470 $\Omega$ )           | VRTB6VS471                 |       | Ohal 8 December                              | Doré Ma                                   |  |

| *                                                            |                                      | Semi-fixed (4.7 kΩ)                  | VRTB6VS472                 | Mark  | Symbol & Description                         | Part No.                                  |  |

| *                                                            |                                      | Semi-fixed (47 kΩ)                   | VRTB6VS473                 |       | VL101 Variable coil                          | VTL-275                                   |  |

| *                                                            | r ∨R406                              | Semi-fixed (4.7 kΩ)                  | VRTG6VS472                 |       | 0-974.7.10                                   | (VTL1005)<br>VTL1003                      |  |

|                                                              |                                      | D i - 4                              | DAEC102 !                  |       | L101 Coil (4.7μH)                            | VTH-008                                   |  |

|                                                              | R25                                  | Resistor array                       | RA5S103J                   |       | L102                                         | V 111-000                                 |  |

|                                                              | D400                                 | (10kΩx5)                             | RD1/2PM221J                | CAPA  | CITORS                                       |                                           |  |

|                                                              | R408                                 | _R48_R225_R220                       | RD1/2FM2213<br>RD1/4PM□□□J | CAFA  |                                              |                                           |  |

| R41, R42, R44—R48, R225—R229<br>R205—R207, R333, R334, R338, |                                      | -n40, NZZU-NZZU<br>2333 R334 R338    | RD1/4VM□□□J                | Mark  | Symbol & Description                         | Part No.                                  |  |

|                                                              |                                      | 1000, 11007, 11000,                  | .,                         |       | C201, C203                                   | CCCCH220J50                               |  |

|                                                              | R339<br>R161—R164, R401, R402, R405, |                                      |                            |       | C118                                         | CCCCH560J50                               |  |

|                                                              |                                      |                                      | RN I/OPULILILIE            |       |                                              |                                           |  |

|                                                              |                                      |                                      | RN1/6PQ□□□□F               |       | C310, C311, C312                             | CCCSL101J50                               |  |

|                                                              |                                      | 410, R413, R414,                     | KN I/OPQUUUUF              |       | C310, C311, C312<br>C226, C227<br>C212, C213 | CCCSL101J50<br>CCCSL121J50<br>CCCSL221J50 |  |

| Mark     | Symbol & Description                     | Part No.       | BLDB Assembly |                        |                     |  |  |

|----------|------------------------------------------|----------------|---------------|------------------------|---------------------|--|--|

|          | C107, C214, C215                         |                |               | EMICONDUCTORS          |                     |  |  |

|          | C119                                     | CCCSL391J50    |               |                        |                     |  |  |

|          | C104, C120                               | CCCUJ221J50    | Mark          | Symbol & Description   | Part No.            |  |  |

|          | C103, C202                               | CCCUJ330J50    | **            | IC301                  | TA8413P             |  |  |

|          | C113                                     | CEANP2R2M50    |               |                        |                     |  |  |

|          |                                          |                |               | Q301 Transistor array  | STA302A             |  |  |

|          | C228, C229                               | CEANP220M10    |               | Q302 Transistor array  | STA303A             |  |  |

|          | C110, C230                               | CEAS010M50     |               | Q303—Q305              | 2SA1048             |  |  |

|          | C108, C109, C116, C117, C122             | CEAS100M50     | *             | D301-D303              | S2V10-4001          |  |  |

|          | C121, C123, C125, C206-C211              | CEAS101M10     | 0454          | 0.7.000                |                     |  |  |

|          | C5, C6                                   | CEAS221M10     | CAPA          | CITORS                 |                     |  |  |

|          |                                          | CEAS221M25     | Mark          | Symbol & Description   | Part No.            |  |  |

|          | C3, C4                                   | CEAS222M25     |               | C301-C303 (33µF/50V)   | VCH1034             |  |  |

|          | C1, C2                                   |                |               | C304                   | CEAS4R7M50          |  |  |

|          | C105                                     | CEAS470M25     |               | C305                   | CKCYF103Z50         |  |  |

|          | C112, C204, C205, C222—C225,             | CFTXA104J50    |               |                        |                     |  |  |

|          | C306, C307                               |                | RESIS'        | TORS                   |                     |  |  |

|          | C115                                     | CFTXA474J50    | Mark          | Symbol & Description   | Part No.            |  |  |

|          | C216, C217                               | CFTXA683J50    |               | All resistors          | RD1/6PM□□□          |  |  |

|          | C101, C126, C127, C314                   | CGCYX473M25    |               | 7111 (00.02010         | 110 7701 111 ====   |  |  |

|          | C313                                     | CKCYB102K50    |               |                        |                     |  |  |

|          | C102, C503, C504                         | CKCYF103Z50    | FTSB          | Assembly (VYS1004)     |                     |  |  |

|          | 3,62, 3333, 233                          |                |               | CONDUCTORS             |                     |  |  |

|          | C501, C502                               | CQMA102J50     | SEIVIIC       |                        |                     |  |  |

|          | C111, C218, C219                         | CQMA103J50     | Mark          | Symbol & Description   | Part No.            |  |  |

|          | C220, C221                               | CQMA182J50     | * *           | IC2, IC3               | BA15218N            |  |  |

|          | C106                                     | CQMA223J50     | **            | IC1                    | HA11529             |  |  |

|          | C114                                     | CQMA822J50     | **            | IC6                    | IR3C02A             |  |  |

|          |                                          |                | **            | IC4                    | NJM4556DE           |  |  |

|          |                                          |                | * *           | IC5                    | NJM4556S            |  |  |

| RESIST   | rors                                     |                |               |                        |                     |  |  |

| Mark     | Symbol & Description                     | Part No.       |               | Ω1, Ω3                 | DTC363ES            |  |  |

| *        | VR102, VR501Semi-fixed (22kΩ)            | VRTB6VS223     |               | Q2                     | UN4112              |  |  |

|          |                                          |                |               | Q16                    | 2SA933S             |  |  |

|          | R114, R115, R118, R120, R127, R128, R138 | RN1/6PQ□□□□F   |               | Q5, Q8, Q10<br>Q12     | 2SB1185<br>2SB1238X |  |  |

|          | Other resistors                          | RD1/6PM□□□J    |               | 012 014                | 2SC1740S            |  |  |

|          |                                          |                |               | Q13, Q14               | 2SD1762             |  |  |

| OTHER    | RS                                       |                | **            | Q4, Q7, Q9             | = '                 |  |  |

| 5.0 mml. | Symbol & Description                     | Part No.       | **            | Q11                    | 2SD1859X            |  |  |

| Mark     |                                          |                | **            | Q6, Q17                | 2SK184              |  |  |

| *        | X101 Crystal resonator                   | VSS1004        | 4.            | D1-D5                  | 1SS254              |  |  |

|          | (16MHz)                                  | \/VB 027       | *             | 81-05                  | 133254              |  |  |

|          | Pin jack (2P)                            | VKB-027        | CAPA          | CITORS                 |                     |  |  |

|          |                                          |                |               |                        | Dark Na             |  |  |

| TNTR     | Assembly                                 |                | Mark          | Symbol & Description   | Part No.            |  |  |

|          |                                          |                |               | C2                     | CCPUSL680J50        |  |  |

| SEMIC    | ONDUCTORS                                |                |               | C38                    | CEAL010M50          |  |  |

| Mark     | Symbol & Description                     | Part No.       |               | C52, C53               | CEAL220M6R3         |  |  |

| **       | Q201, Q202                               | RPI-38         |               | C24, C25               | CEAL330M25          |  |  |

|          |                                          |                |               | C9, C37                | CEANPR47M50         |  |  |

| RESIST   | <b>TORS</b>                              |                |               | C3, C56                | CEJANP010M50        |  |  |

| Mark     | Symbol & Description                     | Part No.       |               | C4, C18                | CEJANP100M10        |  |  |

| a. K     |                                          | RD1/6PM472J    |               | C11                    | CEJANI 100M10       |  |  |

|          | R201, R202                               | NU I/OFIVI4/2J |               | C28                    | CEJA010M50          |  |  |

|          |                                          |                |               | C48, C50               | CEJA220M6R3         |  |  |

|          |                                          |                |               | C31, C32               | CEJA330M25          |  |  |

|          |                                          |                |               | C54                    | CFTXA103J50         |  |  |

|          |                                          |                |               | C5, C17, C19, C33, C35 | CFTXA104J50         |  |  |

|          |                                          |                |               | C15, C16               | CFTXA184J50         |  |  |

|          |                                          |                |               |                        | CETYA 223 IEO       |  |  |

C21

CFTXA223J50

| - <del></del>                           | Symbol & Description                                                                            | Part No.                       | CNNB                      | Assemb                              | ly                                        |                            |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|---------------------------|-------------------------------------|-------------------------------------------|----------------------------|

|                                         | C7                                                                                              | CFTXA333J50                    | SEMIC                     | ONDUCT                              | ORS                                       |                            |

|                                         | C8, C14                                                                                         | CFTXA473J50                    | Mark                      | Symbol &                            | Description                               | Part No.                   |

|                                         | C10, C13                                                                                        | CFTXA683J50                    | Mark                      |                                     |                                           | 1SS254                     |

|                                         | C26                                                                                             | CKCYF103Z50<br>CKPUYB101K50    | *                         | D101                                |                                           | 133234                     |

|                                         | C30                                                                                             | CRPOTBIOTROO                   | CAPAC                     | CITORS                              |                                           |                            |

|                                         | C20, C23, C27, C34                                                                              | CKPUYB102K50                   | Mark                      | Symbol &                            | Description                               | Part No.                   |

|                                         | C1, C29                                                                                         | CKPUYB331K50<br>CKPUYF103Z25   |                           | C105                                |                                           | CEJA470M6R3                |

|                                         | C36, C39—C41, C45—C47, C49,<br>C51                                                              |                                |                           | C104                                |                                           | CKPUYF103Z25               |

|                                         | C12<br>C55                                                                                      | CQMA272J50<br>CQMA472J50       | RESIST                    | rors                                |                                           |                            |

|                                         | C44                                                                                             | CSZA220M10                     | Mark                      | Symbol &                            | Description                               | Part No.                   |

| RESIST                                  | TORS                                                                                            |                                |                           | R101<br>R102—R1                     | 04                                        | RD1/6PM103J<br>RD1/4PM221J |

| Vlark                                   | Symbol & Description                                                                            | Part No.                       |                           |                                     |                                           |                            |

|                                         | VR1-VR3, VR6, VR7, VR11                                                                         | VRTB6VS472                     | OTHER                     | RS                                  |                                           |                            |

| ^                                       | Semi-fixed (4.7kΩ)                                                                              |                                | Mark                      | Symbol &                            | Description                               | Part No.                   |

| *                                       | VR10 Semi-fixed (2.2kΩ)<br>R128                                                                 | VRTB6VS222<br>RN1/6PQ5602F     |                           | CN56                                | Connector (20P)                           | VKN1020                    |

|                                         | R82, R86, R93, R98                                                                              | RD1/2PMF□□□J                   |                           |                                     |                                           |                            |

|                                         | Other resistors                                                                                 | RD1/6PM□□□J                    | IRKB A                    | Assembl                             | V                                         |                            |

|                                         |                                                                                                 |                                | SWITC                     |                                     | •                                         |                            |

| OTHER                                   | RS                                                                                              |                                |                           |                                     | D                                         | Dant No.                   |

| Mark                                    | Symbol & Description                                                                            | Part No.                       | Mark                      |                                     | Description                               | Part No.                   |

|                                         | CN10 Side connector (23P)                                                                       | VKN1013                        | **                        |                                     | 06 Tact switch<br>OSE, PLAY/PAUSE, SCAN,  | VSC-012                    |

| FLKY .                                  | Assembly (VYG1017)                                                                              |                                | OTHER                     | RS                                  |                                           |                            |

| SEMIC                                   | ONDUCTORS                                                                                       |                                | Mark                      |                                     | Description                               | Part No.                   |

| Mark                                    | Symbol & Description                                                                            | Part No.                       | Wark                      | Oyilloor a                          | IR sensor unit                            | GP1U50V                    |

| **                                      | IC1                                                                                             | PDG012                         |                           |                                     | m some and                                | u                          |

| **                                      | Q1, Q2                                                                                          | 2SC2458                        | HEPB Assembly             |                                     |                                           |                            |

|                                         |                                                                                                 |                                | SEMIC                     | ONDUCT                              | ORS                                       |                            |

| *                                       | D1-D6                                                                                           | 1SS254                         |                           |                                     |                                           | Post No.                   |

| SWITC                                   | NUEC                                                                                            |                                | Mark                      |                                     | Description                               | Part No.<br>NJM4556S       |

| • • • • • • • • • • • • • • • • • • • • |                                                                                                 | Dont No.                       | **                        | IC201                               |                                           | 14314145565                |

| Mark                                    | Symbol & Description                                                                            | Part No.                       | CAPA                      | CITORS                              |                                           |                            |

| **                                      | S1—S15 Tact switch (SEARCH/MEMORY, RANDOM PLAY,                                                 | VSC-012                        | Mark                      | Symbol &                            | Description                               | Part No.                   |

|                                         | TIME DISPLAY, PROGRAM, AUTO                                                                     |                                |                           | C201-C2                             |                                           | CGCYX473M25                |

|                                         | PGM EDITING, 10 KEY)                                                                            |                                |                           |                                     | <del></del>                               |                            |

|                                         | 0.7000                                                                                          |                                | RESIST                    | rors                                |                                           |                            |

| CAPA                                    | CITORS                                                                                          |                                | Mark                      | Symbol &                            | Description                               | Part No.                   |

|                                         | Symbol & Description                                                                            | Part No.                       | *                         | VR201                               | Variable resistor (2P)                    | VCS1009                    |

| Mark                                    | C1                                                                                              | CEJA100M50                     |                           |                                     | Other resistors                           | RD1/6PM□□□.                |

| Mark                                    | C1                                                                                              | CEJA101M6R3                    |                           |                                     |                                           |                            |

| Mark                                    | C2                                                                                              |                                | AT: :                     | 10                                  |                                           |                            |

| Mark                                    |                                                                                                 | CKPUYF103Z25                   | OTHER                     |                                     |                                           |                            |

|                                         | C2<br>C3                                                                                        |                                | OTHER<br>Mark             | Symbol &                            | Description                               | Part No.                   |

| RESIS.                                  | C2<br>C3<br>TORS                                                                                | CKPUYF103Z25                   |                           |                                     | <b>Description</b><br>Headphone jack      | Part No.<br>VKN1018        |

| RESIS:                                  | C2 C3 TORS Symbol & Description                                                                 | CKPUYF103Z25  Part No.         |                           | Symbol &                            |                                           |                            |

| RESIS:                                  | C2 C3  TORS  Symbol & Description  R1 Resistors array (10kΩx4)                                  | Part No. RA4S103J              | Mark                      | Symbol &<br>JA201                   | Headphone jack                            |                            |

| RESIS'                                  | C2 C3  TORS  Symbol & Description  R1 Resistors array (10kΩx4) R2, R3                           | CKPUYF103Z25  Part No.         | Mark  LFSB 4              | Symbol & JA201  Assemble            | Headphone jack                            |                            |

| RESIS'<br>Mark                          | C2 C3  TORS  Symbol & Description  R1 Resistors array (10kΩx4) R2, R3                           | Part No. RA4S103J              | Mark<br>LFSB A            | Symbol & JA201  Assemble            | Headphone jack                            | VKN1018                    |

| RESIS:                                  | C2 C3  TORS  Symbol & Description  R1 Resistors array (10kΩx4) R2, R3                           | Part No. RA4S103J              | Mark  LFSB A  SWITC  Mark | Symbol & JA201  Assemble:H Symbol & | Headphone jack<br><b>y</b><br>Description | VKN1018  Part No.          |

| RESIS'                                  | C2 C3  TORS  Symbol & Description  R1 Resistors array (10kΩx4) R2, R3  RS  Symbol & Description | Part No.  RA4S103J RD1/6PM154J | Mark<br>LFSB A            | Symbol & JA201  Assemble            | Headphone jack                            | VKN1018                    |

CN57 Connector (20P) VKN1017

## COIL

| Mark  | Symbol & De | scription                          | Part No.             |  |

|-------|-------------|------------------------------------|----------------------|--|

| Δ     | L101        | Line filter                        | VTL-157<br>(VTL-004) |  |

| CAPAC | CITORS      |                                    |                      |  |

| Mark  | Symbol & De | escription                         | Part No.             |  |

|       | C101-C103   | Ceramic capacitor<br>(0.01/AC125V) | RCG-009              |  |

#### **RESISTORS**

| Mark     | Symbol & Description | Part No.    |

|----------|----------------------|-------------|

| <u> </u> | R101                 | RD1/2PM225J |

# SYPS Assembly (VYR1055) **SEMICONDUCTORS**

| Mark   | Symbol & Description | Part No.     |

|--------|----------------------|--------------|

| **     | IC1                  | NJM4558S     |

| **     | Q12, Q14, Q15        | UN4212       |

| **     | Q2, Q6, Q8           | 2SA933S      |

| **     | Q5                   | 2SB1052      |

| **     | Q17                  | 2SB1238X     |

| ★★ Q10 |                      | 2SC1627      |

|        |                      |              |

| **     | Q1, Q7, Q9, Q13      | 2SC1740S     |

| **     | Q16                  | 2SC1847      |

| **     | Q3, Q4, Q11          | 2SD1267      |

|        |                      |              |

| *      | D8, D9               | HZS5.6EB2    |

| *      | D10                  | HZS8.2EB2    |

| *      | D15                  | MTZ36C       |

|        |                      | (MTZ36D)     |

| *      | D16                  | MTZ5.1B      |

|        |                      |              |

| *      | D1, D2               | RB-152LF     |

| *      | D11                  | \$2K20       |

| *      | D12-D14              | 1SR35-100AVL |

| *      | D3-D7                | 1SS254       |

|        |                      |              |

#### COIL

| Mark | Symb | ool & Description | Part No. |

|------|------|-------------------|----------|

|      | 1 1  | Coil              | VTT-070  |

# **CAPACITORS**

| Mark | Symbol &   | Description       | Part No.    |

|------|------------|-------------------|-------------|

|      | C18        |                   | CCCSL331J50 |

|      | C22        |                   | CCCSL471J50 |

|      | C9, C10, 0 | C13, C17, C29     | CEAS100M50  |

|      | C16, C27,  | C28               | CEAS101M50  |

|      | C23        |                   | CEAS3R3M50  |

|      | C7, C8     |                   | CEAS470M25  |

|      | C14, C15   |                   | CEAS470M50  |

|      | C21        |                   | CKCYB102K50 |

|      | C1, C2, C  | 11, C12, C30, C31 | CKCYF103Z50 |

|      | C19        |                   | CQMA183J50  |

|      | C26        |                   | CQMA472J50  |

|      | C3, C4     | (2200µF/25V)      | PHC1027     |

|      | C6         | (4700μF/10V)      | VCH1003     |

|      | C5         | (6800μF/10V)      | VCH1046     |

#### **RESISTORS**

| Mark | Symbol & D | escription      | Part No.     |  |

|------|------------|-----------------|--------------|--|

|      | R27        |                 | RS1PMFR51J   |  |

|      | R26        |                 | R\$1PMF2R7J  |  |

|      | R39        |                 | RS1PMF3R3J   |  |

|      | R42, R43   |                 | RD1/2PMF3R3J |  |

|      | R1, R2     |                 | RD1/2PM471J  |  |

|      | R28-R31    |                 | RN1/6PQ□□□□F |  |

|      |            | Other resistors | RD1/6PM□□□J  |  |

# LMCB Assembly **SEMICONDUCTORS**

| Mark | Symbol & Description | Part No. |

|------|----------------------|----------|

| **   | IC1                  | TA7291P  |

| *    | D1                   | HZS9B3   |

#### **CAPACITORS**

| Mark | Symbol & Description | Part No.    |  |

|------|----------------------|-------------|--|

|      | C1                   | CGDYX473M25 |  |

|      | C3                   | CEAS100M50  |  |

#### **RESISTORS**

| Mark | Symbol & Description | Part No.    |  |  |

|------|----------------------|-------------|--|--|

|      | R1                   | RD1/4VM222J |  |  |

|      | R2                   | RD1/4VM220J |  |  |

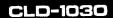

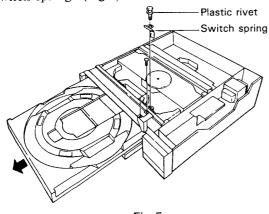

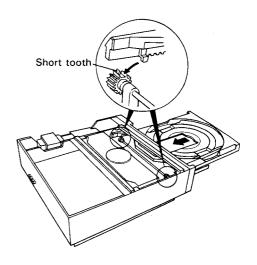

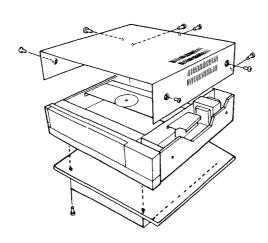

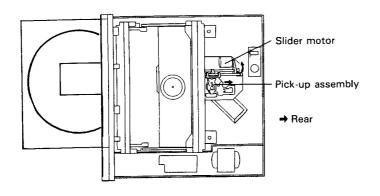

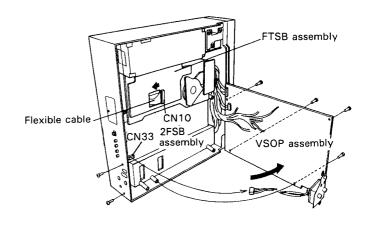

CLD-1030 3 3.4 MECHANISM ASSEMBLY VIEW Parts List of Mechanism Assembly Mark No. Part No. Description No. Part No. Description 101. 1. VLL1058 Tilt base Carriage shaft 2. VBH1040 Slider spring 102. PU holder 3. PMA30P060FCU 103. M holder Screw 4. VXM1021 104. Mechanism base Spindle motor 5. VBH1024 Centering spring 105. TNTR assembly 6. VNT1003 106. BLDB assembly Centering hab 7. CMZ20P080FCU FTS sheet Screw 107. 8. YC40FBT Washer 108. 9. VNL1079 Cam gear 109. Base plate 10. VNL1078 110. Nut 11. VNL1085 Worm 111. Insulator sheet 12. WT21D050D050 112. Dump cushion Washer 13. PMA30P040FCU Screw 113. Cushion E 114. Cord clamper 14. VNL1051 Motor pulley 15. VNL1080 Slider 16. VNE1100 Rock plate 17, VXA1159 Roller assembly В В 18. SMZ30H250FBT Screw 19. PPZ20P050FMC Screw 20. PMA20P040FCU Screw 21. SMZ30H080FBT Screw Slide switch (SLIDER/PARK) (S4) 22. VSK1003 23. VBH1022 Tilt spring 24. VNL1077 Fulcrum cam 25. VWY1011 Pick-up assembly 26. VLL1065 Bolt 3 x 18 27. VLL-378 Bolt 8 28. VYS1004 FTSB assembly 29. IPZ30P080FCU Screw 30. BPZ30P080FCU Screw 31. PMB30P060FCU Screw 32. VEB1029 Timing belt 33. VXA1129 Screw nut assembly 34. VXA1106 TL base assembly 35. VXX1082 Tilt motor assembly-S 36. VXX1155 Slider motor assembly-S 37. VXX1071 Turntable assembly-S 38. VLL1107 Bolt 2.6 x 6 39. VEB1032 Sheet 40. ... . . . 41. VEB1017 Rubber tube 42. VBK1010 SN spring 26 m D D 3 2

3

6

# **6. ELECTRICAL PARTS LIST**

#### NOTES:

- Parts without part number cannot be supplied.

- Parts marked by "®" are not always kept in stock. Their delivery time may be longer than usual or they may be unavailable.

- The A mark found on some component parts indicates the importance of the safety factor of the part. Therefore, when replacing, be sure to use parts of identical designation.

- For your parts Stock Control, the fast moving items are indicated with the marks  $\star \star$  and  $\star$ .

- \*\* GENERALLY MOVES FASTER THAN\*

- This classification shall be adjusted by each distributor because it depends on model number, temperature, humidity, etc.

- When ordering resistors, first convert resistance values into code form as shown in the following examples.

- Ex. 1 When there are 2 effective digits (any digit apart from 0), such as 560 ohm and 47k ohm (tolerance is shown by J =5%, and K = 10%).

| $560\Omega$ | $56 \times 10^{1}$ | 561 |  |

|-------------|--------------------|-----|--|

| $47k\Omega$ | $47 \times 10^{3}$ | 473 |  |

| $0.5\Omega$ | 0R5                |     |  |

| $I\Omega$   |                    |     |  |

## Miscellaneous Parts P.C. BOARD ASSEMBLIES

BLMB assembly

## LPFB Assembly COILS

| Mark | Symbol & Description | Part No. | Mark | Symbol | & Description  | Part No.     |

|------|----------------------|----------|------|--------|----------------|--------------|

|      | LPFB assembly        |          |      | L1     | Axial inductor | LAU330J      |

|      | VSOP assembly        | VWS1025  |      | L2     | Axial inductor | LAU430J      |

|      | 2FSB assembly        | VWV1040  |      | L3     | Axial inductor | LAU270J      |

|      | TNTR assembly        |          |      |        |                |              |

|      | BLDB assembly        |          | CAPA | CITORS | •              |              |

|      |                      |          | Mark | Symbol | & Description  | Part No.     |

|      | FTSB assembly        | VYS1004  |      |        |                | CCPUCH150J50 |

|      | FLKY assembly        | VYG1017  |      |        |                |              |

|      | CNNB assembly        |          |      | C2     |                | CCPUCH2R2K50 |

|      | IRKB assebmly        |          |      | C3     |                | CCDCH560J50  |

|      | HEPB assembly        |          |      | C4     |                | CCPUCH1R5M50 |

|      | FILE B assembly      |          |      | C5     |                | CCDCH510J50  |

|      | LFSB assembly        |          |      | •      |                |              |

|      | SYPS assembly        | VYR1055  |      | C6     |                | CCDCH220J50  |

|      | LMCB assembly        |          |      | C7     |                | CCPUCH180J50 |

# **OTHERS**

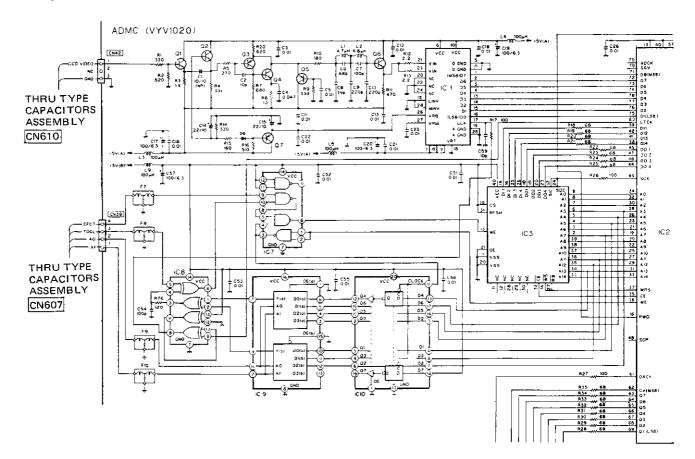

## VSOP Assembly (VWS1025) **SEMICONDUCTORS**

| Mark |            | Symbol & Description |                                                      | Part No. Mark S              | Symbol & Description | Part No.                                     |                                     |

|------|------------|----------------------|------------------------------------------------------|------------------------------|----------------------|----------------------------------------------|-------------------------------------|

| Δ    |            |                      | Fuji card<br>AC Power cord<br>Strain relief          | VDA1051<br>VDG1012<br>CM-22C | **                   | IC7                                          | CXD1095Q<br>HD6303YP<br>(HD63A03YP) |

| Δ    | **         | FU1, FU2             | Fuse (3A)                                            | VEK-018                      | * *<br>* *           |                                              | M74LS00P<br>M74LS27P                |

| Δ    | * *<br>* * | FU3, FU4<br>S1       | Fuse (2A)<br>Slide switch                            | VEK-022<br>VSK1003           |                      | IC8                                          | PD6063                              |

|      | * *<br>* * |                      | (TABLE/PARK) Slide switch (TABLE/IN) Slide switch    | VSK-010<br>VSK-012           | **                   | IC5<br>IC3                                   | M74LS30P<br>M <b>7</b> 4LS74AP      |

|      | **         |                      | (TABLE/OUT)<br>Slide switch                          | VSK1003                      | * *<br>* *<br>* *    | IC403<br>IC103, IC105, IC106<br>IC104, IC107 | NJM2903S<br>NJM4558D<br>NJM4558S    |

|      |            |                      | (SLIDER/PARK)                                        |                              |                      | IC406                                        | PA0017                              |

|      | **         |                      | Loading motor assembly-S                             | VXX1084<br>VXM1021           | **<br>**             | IC301<br>IC102                               | PA0026<br>PA5009                    |

|      | **         |                      | Spindle motor Pick-up assembly Tilt motor assembly-S | VWY1011<br>VXX1082           | * *<br>* *           | IC401<br>IC2                                 | PA5010<br>PD0024                    |

|      | **         |                      | Slider motor assembly-S                              | VXX1155                      | **                   | IC101<br>IC404                               | PD9001<br>PM0001                    |

| Δ    | *          |                      | Power transformer                                    | VTT1026                      | **                   | IC407<br>IC405                               | TA7347P<br>TL8707P                  |

| // Aark  | Symbol & Description                         | Part No.            | Mark | Symbol & Description             | Part No.     |

|----------|----------------------------------------------|---------------------|------|----------------------------------|--------------|

| **       | Q107, Q115, Q120, Q121                       |                     |      | C312, C429, C483                 | CCCCH330J50  |

|          | Q301                                         |                     |      | C311, C453, C662                 | CCCCH390J50  |

| **       | Q101, Q106, Q108, Q113                       | , Q122, UN4212      |      | C417, C470                       | CCCCH430J50  |

|          | Q124, Q302, Q601                             |                     |      | C457, C666                       | CCCCH470J50  |

|          | Q430                                         | 2SA1015             |      | C31, C411                        | CCCCH510J50  |

| **       | Q117, Q109, Q403, Q404                       | -, Q406, 2SA933S    |      | 001, 041)                        | 000011010000 |

|          | Q602                                         |                     |      | C328, C330, C473                 | CCCCH560J50  |

| 4.4      | Q112                                         | 2SC1583             |      | C106, C129                       | CCCCH680J50  |

|          | Q405                                         | 2SC1563<br>2SC1627  |      | C454                             | CCCCH750J50  |

|          | Q2, Q110, Q114, Q118, Q                      |                     |      | C432, C433                       | CCCCH820J50  |

| ^ ^      | Q126, Q303—Q306, Q40<br>Q421—Q426, Q428, Q43 | 7-Q417,             |      | C317, C450, C25                  | CCC\$L181J50 |

| **       | Q119                                         | 2SK184              |      |                                  |              |

|          |                                              |                     |      | C316, C335, C336                 | CCCSL221J50  |

|          | D105                                         | HZS3B2              |      | C458                             | CCCSL241J50  |

|          | D120                                         | HZS5C2              |      | C434                             | CCCSL271J50  |

|          | D407                                         | HZS6C2              |      | C444                             | CCCSL301J50  |

|          | D121, D122, D410                             | HZS7B2              |      | C1, C2, C9                       | CCCSL330J50  |

| *        | D503                                         | HZS9A3              |      |                                  |              |

|          | D505                                         | 1174A11             |      | C435                             | CCCSL391J50  |

| <b>π</b> | D411                                         | HZ4ALL<br>HZ5B2     |      | C447                             | CCDCH220J50  |

|          | D119                                         | SLV31VC3            |      | C668                             | CCDCH620J50  |

|          | D3, D4, D106D109, D1                         |                     |      | C474                             | CCDCH910J50  |

| ^        | D123-D126, D301-D30                          |                     |      | C29                              | CCDSL391J50  |

|          | D402, D405, D406, D409                       |                     |      |                                  |              |

|          | D504                                         |                     |      | C15, C428, C430, C452            | CCPUCH100J5  |

| *        | D502                                         | SM-IXNO2            |      | C455                             | CCPUCH120J5  |

|          |                                              |                     |      | C407, C408, C623, C658           | CCPUCH150J5  |

| OILS     | AND FILTERS                                  |                     |      | C13, C406, C620                  | CCPUCH180J5  |

| lark     | Symbol & Description                         | Part No.            |      | C10                              | CCPUSL220J50 |

|          | L101, L401—L404, L412                        | LAU120J             |      |                                  |              |

|          | Axial inducto                                |                     |      | C14, C16                         | CCPUSL470J50 |

|          |                                              |                     |      | C475                             | CEALNP220M1  |

|          | L409 Axial inducto                           |                     |      | C343                             | CEANLR47K50  |

|          | L410, L426 Axial inducto                     |                     |      | C345                             | CEANL220K16  |

|          | L1 Axial inducto                             | or LAU221J          |      | C145                             | CEANP010M50  |

|          | L102 Axial inducto                           | or LAU270J          |      | C143                             | CEANP101M6R  |

|          | L405, L413, L425                             | LAU330J             |      | C140                             | CEANP2R2M50  |

|          | Axial inducto                                | or                  |      | C166, C142, C146, C318, C319     | CEANP220M10  |

|          | L427 Axial inducto                           | or LAU560J          |      | C403, C503, C508                 | CEASR47M50   |

|          | L411 Axial inducto                           | or LAU680J          |      | C114, C413, C515, C518           | CEASO10M50   |

|          | L406 Coil                                    | LRA271K             |      |                                  |              |

|          | L301 Coil                                    | LRA390K             |      | C3, C22, C334, C337, C338, C349, | CEAS100M50   |

|          | L415 Coil                                    | LRA391K             |      | C354 - C356, C469, C481, C663    |              |

|          | L414 Coil                                    | LRA561K             |      | C4, C7, C314, C315, C353, C493,  | CEAS101M10   |

|          | L420 Coil (3.9MH:                            |                     |      | C494, C522, C525, C622,          |              |

|          | 2011 (0.011111                               | 712170              |      | C11, C151, C357, C358, C443,     | CEAS220M50   |

|          | F301 B.P.F. (2,3M                            | IHz) VTF1002        |      | C501, C505, C507, C511, C513,    |              |

|          | F301 B.F.F. (2.30)                           |                     |      | C516, C655, C656                 |              |

|          | F202 D.D.F./2.0.M                            | (VTF1026)           |      |                                  |              |

|          | F302 B.P.F (2.8 M                            |                     |      | C309, C310, C360                 | CEAS221M10   |

|          | 5505                                         | (VTF1027)           |      | C480, C613                       | CEAS3R3M50   |

|          | F505 L.P.F (1.75N                            |                     |      | C149, C313, C514, C519, C520     | CEAS4R7M50   |

|          |                                              | (VTF1024)           |      | C119, C133, C135, C154, C157,    | CEAS470M25   |

|          |                                              |                     |      | C158, C161,C163, C168, C171,     |              |

|          | F506 Audio B.P.F                             | VTF1022             |      | C177, C179, C180, C350, C402,    |              |

|          |                                              | (VTF1025)           |      | C405, C421, C427, C437, C440,    |              |

|          | F1, F2, F101, F501—F50                       | 3 VTH1001           |      | C446, C488, C490, C610, C612,    |              |

|          | 3 terminal fil                               | ter                 |      | C651                             |              |

| APA      | CITORS                                       |                     |      | C201 C202 C245 C511              | CEAS471M10   |

| 1ark     | Symbol & Description                         | Part No.            |      | C301, C302, C346, C621           | CEJANP470M1  |

|          | C125, C126, C128, C150                       |                     |      | C456                             | CEJANP470WT  |

|          | C624                                         | , 0773, 00000101330 |      | C486                             | CEJA330M10   |

|          | C448, C482                                   | CCCCH121J50         |      | C471<br>C463, C476               | CEJA470M16   |

|          |                                              | いんきょう しきしきり         |      | G4D3, G47D                       | CEJA4/UNITO  |

CCCCH151J50

CCCCH300J50

C124, C465, C467

C451, C523, C659

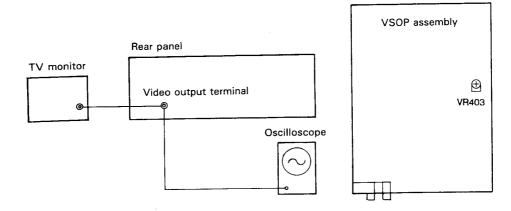

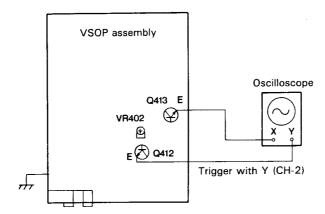

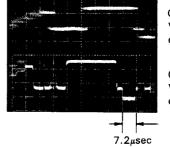

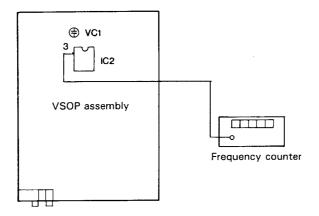

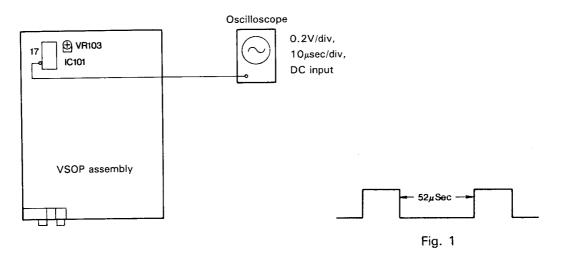

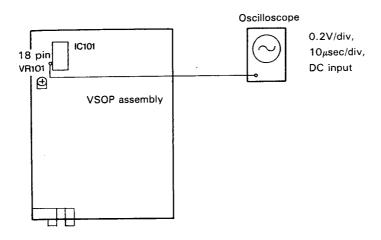

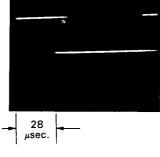

#### 3. VCXO OFFSET ADJUSTMENT

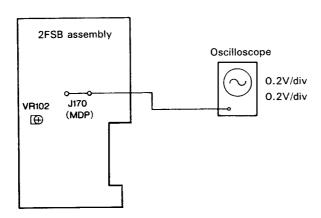

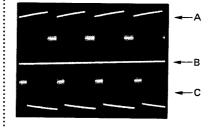

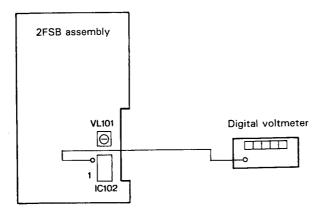

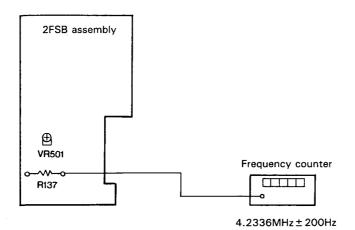

#### 8.6 2FSB Assembly Adjustments

- Purpose: Minimize the VCXO PLL phase error offset voltage

- Symptoms indicating need for adjustment: Intermittent output of digital sound during LDD playback (output of synchronous noise)

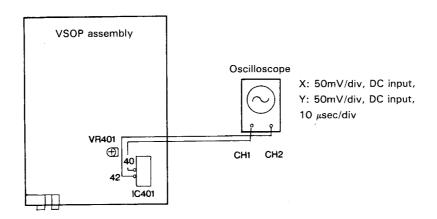

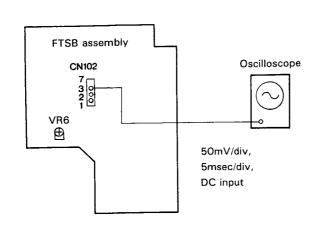

- Measuring instruments and jigs:

- Measuring position

- Test disc and player mode

- Adjustment position

- Oscilloscope

- 2FSB assembly J170 (MDP)

- LDD disc play any frame

- 2FSB assembly VR102

#### Connection diagrams

#### Adjustment procedure

- 1. Play any frame of the LDD disc.